# 科学研究費助成事業 研究成果報告書

平成 26 年 6 月 9 日現在

機関番号: 1 2 3 0 1 研究種目: 若手研究(B) 研究期間: 2011 ~ 2013

課題番号: 23760383

研究課題名(和文)ディジタル・アナログ混在汎用スイッチング電源システムの知能化制御技術

研究課題名 (英文) Intelligent Control Technologies for Digital-Analog Hybrid Switching Power Supply System

#### 研究代表者

橋本 誠司 (Hashimoto, Seiji)

群馬大学・理工学研究院・准教授

研究者番号:30331987

交付決定額(研究期間全体):(直接経費) 3,300,000円、(間接経費) 990,000円

研究成果の概要(和文):本研究の目的は,汎用スイッチング電源に対しディジタル制御方式を導入することにより知能化した新しい汎用電源システムを開発することである。この目的に対し,単一設計パラメータで,多チャンネルマルチレベル電圧出力が可能となる制御法を提案した。ここでは適応制御法を導入することにより,入力電圧変動や負荷変動,AD/DA分解能誤差,スイッチングによる電圧制御という非線形性に対して,制御性能劣化を適応的に補償可能であることを実験により検証した。また,ディジタル化による出力電圧のリミットサイクル振動に対し,分解能を考慮した低コストかつロバストな制御器の実現法を提案した。

研究成果の概要(英文): The purpose of this research is to develop a new intelligent general-purpose switching power supply system by introducing a digital control scheme to the system. To achieve this purpose, a control method with single design parameter which able to control multi-channel and multi-level voltage o utput system is proposed. Here, by introducing an adaptive function, it is experimentally verified that control performance degradation caused by the nonlinearity behavior in the system such as from input voltage perturbation, load variation, AD/DA resolution error and switching regulation could adaptively be compens ated. Moreover, realization method of low cost, robust and appropriately considered AD/DA resolution controller for limit-cycle variation of output voltage that is caused by digitization is proposed.

研究分野: 工学

科研費の分科・細目: 電気電子工学・制御工学

キーワード: スイッチング電源 知能化制御 ディジタル制御 リミットサイクル振動

### 1.研究開始当初の背景

近年,サーバやルータの情報機器に加え,PC や大型 TV,家庭用ゲーム機などの情報家電では,操作性や耐久性の向上,多機能化,通信機能の多様化など求められる性能は高度化している。同時に,そこで用いられる汎用スイッチング電源への要求性能の高性能化・多機能化も著しい。小型・低消費電力化に加え電圧のマルチレベル化,ディジタル負荷に対する安定化,経年変化に対する品質保持,冗長化による信頼性向上,故障診断・警告,自己修復など多岐にわたる。

-方,スイッチング電源は線形素子に加え 非線形素子により構成されるため,その動作 は非線形であり高精度制御が困難な対象で ある。そのエネルギー変換過程は,入力電源 や負荷状態に強く依存しており,制御を困難 にする要因の一となる。このような汎用スイ ッチング電源の制御方式は,コスト面や制御 技術の継承性から PID 制御を代表としたア ナログ制御方式により実現されている。した がって, 広範囲に変動する入力電源や負荷状 態に対し,制御性能を保持することは困難で ある。また,複数の要求を同時に達成するに は回路規模が複雑化,大型化したり,実現不 可能な場合も多い。例えば,金融機関やグロ ーバル通信で使用されるシステムでは,ダウ ンタイムゼロが要求されるが,これはディジ タル制御電源でしか実現できない機能の一 つである。このような状況の下,ディジタル 制御は汎用電源市場を抜本的に変え得る次 世代技術として期待されている。

# 2. 研究の目的

- (1) 本研究は,現状のアナログ制御方式にかわりディジタル制御方式を導入することにより汎用スイッチング電源の高性能化・高機能化を目指した先行研究開発である。パワーエレクトロニクスとアナログ電源技術に新たに先進ディジタル制御技術を導入し,統合化することにより高性能かつ高機能な,すなわち知能化した汎用電源を低消費電力で低コストに実現することが目的である。

- (2) 本目的に対し,近い将来に汎用スイッチング電源に要求される仕様と現状のアナログ制御方式の限界,そしてディジタル制御方式の導入による問題解決法,機能拡張の有効性を調査した。これを基に,まずは提案ディジタル制御技術を実現できる FPGA 駆動の高速 PWM 回路と動力部を含む多チャンネルディジタル制御電源(多チャンネル降圧型DC-DC コンバータ)のハードウェアの試作開発を行った。

- (3) 電源の知能化に対する具体的な課題を以下に示す。

軌跡追従性と制約条件を考慮したディジタル制御法の確立:多入出力システム同定理論を応用し,多チャンネル・マルチレベル高精度出力制御が可能なディジタル制御法を実現する。ここでは,電源の順序起動・停止

管理や突入電流保護に対する各種制約条件を満足できるよう連続軌跡追従型制御系に発展させ、制御帯域内で伝達ゲインが1となる制御系を構築する。また、汎用性と製品ロットばらつきを考慮し、制御系のチューニングは全てブラックボックス化・自動化する。

負荷変動や経年変化に対して適応的に制御性能を保持する制御法の確立:提案している外乱オブザーバ付き内部モデル制御法をオンライン同定法を用いて適応化するにより,ディジタル負荷や最大負荷変動,入力電源変動,アナログ電源回路の経年変化特性に対しても常に最適な制御性能を保持できるような適応化制御システムを実現する。

電源システムの状態監視と故障診断,寿命推定法の確立:電源温度,出力電圧・(推定)電流のポーリングに加え,適応同定法における忘却係数,学習理論における重み係数の変化に着目し,特徴パラメータを抽出する。これにより,アナログ電源回路と負荷のリアルタイム状態監視や故障診断,寿命推定する手法を確立する。

ディジタル・アナログ混在システムの低消費電力・低コスト実現法:制御装置のディジタル化により,アナログ・ディジタル変換(ADC)/ディジタル・アナログ変換(DAC)に起因した分解能問題が顕在化する。分解能と制御性能におけるトレードオフの関係は回避できないが,ここでは低コスト化に向け,目標電圧と入力電源電圧変動を考慮した出力電圧の振動最小化手法を実現する。

### 3. 研究の方法

先進ディジタル制御による知能化汎用スイッチング電源の開発課題に対する具体的な方法とその計画を以下に示す。

- (1) 高性能化課題:基礎研究結果と試作機を 用いた制御実験を基に,提案しているシステ ム同定法と制御手法を応用し,以下に示すデ ィジタル・アナログ混在電源システムに特化 した制御手法を実現する。 部分空間法を用 いた多入出力システム同定法による多チャ ンネルのマルチレベル電圧制御システムの 一括同定法とそれによる製品ロットの公差 同定モデルと外乱オブザーバ付き 内部モデル制御法(DIMC)による単一設計パ ラメータ(制御帯域)での高性能電源制御系の 設計法とそのブラックボックス化。 アンチ ワインドアップ補償と分解加速度制御に基 づく,マルチレベル電源の順序起動・停止と 負荷への突入電流を考慮した DIMC の制約 条件付き連続軌跡追従型の電源制御法への 負荷変動や入力電源変動,経年変化 に対する制御性能保証のための可変忘却要 素を導入した適応同定法による適応化 DIMC の実現と自動化。 DSP 制御方式の導 入による知能化汎用電源の高度評価試験用 実験装置への改良。

- (2) <u>高機能化・知能化課題</u>: 製作したディジタル制御電源試験装置に,提案する高性能

制御方式を実装し,負荷試験を行い電源仕様に対する有効性の検証ならびに改善を行う。また,アナログ回路構成要素等の経年変化に対するロバスト性の評価を行う。 高機能化技術に関しては,実験解析を通じて検出状態量に加え,適応同定法での可変忘却要素,学習理論における重み係数変化に着目した特徴パラメータによるリアルタイム状態推定・監視,異常検出技術を実現する。

(3) 低消費電力・低コスト実現:知能化制御法や推定・診断アルゴリズムの実装において以下の低コスト実現法を達成する。 ADC/DAC分解能と入力電源変動を考慮した出力電圧振動最小化のための目標値補正法。

要求制御性能を考慮した固定小数演算で の低消費電力・低コスト最適実現手法。

### 4. 研究成果

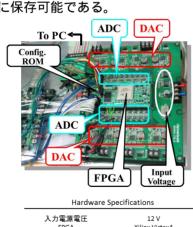

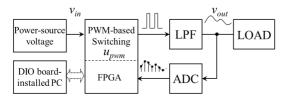

(1) ディジタル制御スイッチング電源装置: 開発したディジタル制御スイッチング電源 とその仕様を図1に示す。また,開発した装 置のブロック構成図を図2に示す。本制御対 象は, FPGA 駆動のディジタル制御化した PWM(DPWM) スイッチングによる降圧型 DC-DC コンバータである。入力信号  $u_{pwm}$  は PWM スイッチング(DAC) の On-Off の Duty 比で,この Duty 比により入力電圧  $v_{in}$ を制御する。出力信号はOn-Off されたv<sub>in</sub> を 各出力端子にあるローパスフィル(LPF)を通 すことで平滑化した電圧  $v_{out}$  となる。 $v_{out}$  は ADC によりディジタル化され,フィードバ ック制御される。ここで,ディジタル信号レ ベルの  $u_{pwm}$  と  $v_{out}$  は DIO ボードを通して PC に保存可能である。

Hardware Specifications

入力電源電圧 12 V

FPGA Xillinx Virtex4

クロック周波数 300MHz

出力チャネル 8ch

AD変換速度 25MHz

AD分解能 12bits

PWM Duty(DA)分解能 0.10%(10bits)

図1 開発したディジタル制御電源と仕様

図2 電源システムのブロック構成図

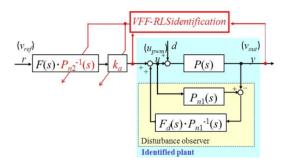

(2) <u>DIMC 制御法</u>: 本開発では,適応同定結果を陽に応用できるよう内部モデル制御(IMC)を用いたモデルベースド制御法を導入する。加えて,IMC に外乱オブザーバを導入し,負荷変動やモデル化誤差に対するロバスト性の向上を図る。すなわち,外乱オブザーバに基づく内部モデル制御(DIMC)を用いる。DIMC のブロック図を図3に示す(同図の朱記以外の部分)。外乱オブザーバの制御構成は,IMC に極めて類似しており,モデル化誤差および外乱が存在しない場合にはフィードバック補償が働かない。従って,DIMC はオープン駆動型という特長を有する。

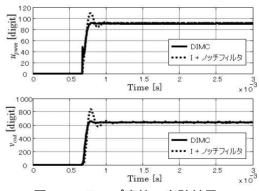

同定モデルに基づいて構築した DIMC と ノッチフィルタ(極零相殺型)付き積分制御の ステップ応答実験結果を図 4 に比較して示す。 実験条件は ,制御帯域を 4 kHz ,目標値を 639 digit(1 V 相当)とした。図 4 よりオーバーシュートにおいて ,極零相殺型の 22.5 %に対し DIMC は 0.63 %となった。また整定時間は極零相殺型が 0.90 ms , DIMC が 0.77 ms となりオーバーシュート ,整定時間ともに DIMC の方が性能改善されることが確認できた。

図 3 適応 DIMC のブロック線図

図4 ステップ応答の実験結果

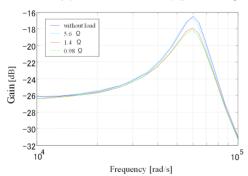

(3) スイッチング電源制御への適応機構の導入:電源システムの出力端に抵抗負荷を接続し,抵抗負荷試験を行った。図5に負荷変動に対する周波数特性を示す。外乱オブザーバがノミナル化特性を有していても,負荷による干渉で応答性能は劣化する。そこで対象のリアルタイム同定を目的に可変忘却要素を用いたオンライン同定法を導入した。

図 3 で示されている DIMC システムは 2 つのノミナルモデル  $P_n(s)$ を有している。外乱オブザーバは実対象をノミナルモデルとし

て補償し,また,印加された外乱の影響を減少させることができる。しかし,その効果は外乱オブザーバの周波数帯域内である。これは,外乱オブザーバを伴う制御対象がすでにそのノミナルモデルへの摂動を有していることを意味する。この事実に基づいて,適応同定機構を図3に示されているフィードフォワードパスの中のノミナルモデル  $P_{n2}(s)$ に導入する。図中のゲイン  $k_a$  は  $P_{n1}(s)$ と  $P_{n2}(s)$ のゲインの不一致を補償するためのものであり,次式とする。

$$k_a = P_{n2}(0) \cdot P_{n1}^{-1}(0)$$

ここでは,可変忘却要素を用いた逐次最小二乗(VFF-RLS)法を採用した。VFF-RLS法は,次の評価関数を最少にする最少二乗推定法を基にしている。

$$J_k(\theta) = \sum_{i=1}^k \lambda^{k-1} \varepsilon^2(i)$$

ここで $\lambda$ は忘却要素, $\varepsilon(i)$ は時間iでの予測誤差である。

オフライン同定実験と同じ条件で VFF-RLS によるオンライン適応同定実験を 行った。オフライン同定での実験出力とモデ ル出力の最少二乗誤差和が  $1.09\times10^3$  であっ たのに対し, VFF-RLS では  $7.80\times10^2$  と, 約 28 %誤差が改善された。

次に得られた次式で示される 2 次 ARX モ デルのパラメータを評価した。

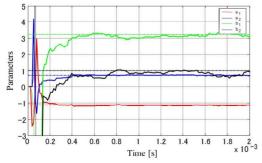

$(1+a_1z^{-1}+a_2z^{-2})y(k)=(b_1z^{-1}+b_2z^{-2})u(k)+e(k)$  図 6 に同定パラメータの時間変化を示す。図 6 にはオフライン結果を点線,オンライン結果を実線で示している。同定パラメータは約 300 ステップで収束していることがわかる。この結果より,VFF-RLS により推定したパラメータはオフライン同定で得られたパラメータに追従していることが確認できた。

図 5 各負荷によるモデルの周波数特性

図6 オンライン同定パラメータ

(4) ディジタル制御電源のリミットサイクル振動低減手法:本開発では,ディジタル制御化した PWM(DPWM)コンバータを対象とし,アナログ・ディジタル変換(ADC)とディジタル・アナログ変換(DAC)に起因した出力電圧振動の低減化手法を提案した。また,出力電圧の振動は入力電圧変動に依存するため,その推定法についても述べる。

### 電圧振動の解析

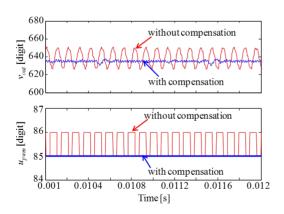

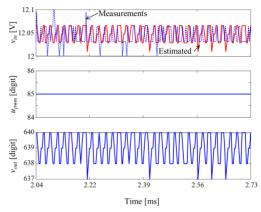

ディジタル制御では,ADC/DACに起因し た入力分解能と出力分解能が存在するため、 所望の出力電圧  $v_{out}$  をえようとしたとき,制 御入力である*u<sub>nwm</sub>*が振動的に二値をとる場合 がある。これは分解能以下の値を入力できず、 二値を時間的に切り替えることにより平均 的に実現することに起因する。この ирми の切 り替えの影響から vout にリミットサイクルを 持つ振動が生じる。一例として,図7に積分 制御器によりフィードバック制御実験を行 ったときの定常状態の拡大図を示す。目標値 は 639 digit (1V 相当)のステップ信号である。  $u_{pwm}$ が 85 と 86 の二値をとり, その結果, 出 力が振動しながらその平均値で 639 digit を 達成していることがわかる。また,入力電圧 v<sub>in</sub> の変動にあわせて二値の時間割合は変化 することに注意する。

# リミットサイクル振動低減手法

以下, $v_{in}$ の変動も考慮した $v_{out}$ の振動低減手法を示す。本手法では, $v_{out}$ 振動の原因となる二値を交互にとる制御入力を一定値となる最適な目標電圧  $v_{ref}^{opt}$ [digit]に補正する。 $u_{pwm}$ [%]の分割数を $n_{pwm}$ [digit]とすると,目標電圧  $v_{ref}$ [V]に対して振動を最小化する入力の整数値 n[digit]は,

$$n[\text{digit}] = \text{round} \left[ \frac{v_{ref}[V]}{v_{in}[V]/n_{pwm}[\text{digit}]} \right]$$

(1)

となる。次に, $v_{out}[V]$ の最大値を  $v_{out\text{-}max}[V]$ , その分割数を  $n_{out}[ ext{digit}]$ とすると ,振動を最小 化する  $v_{ret}^{opt}$  は,

$$v_{ref}^{opt}[\text{digit}] = \text{round} \left[ \frac{n[\text{digit}]v_{in}[V]/n_{pwm}[\text{digit}]}{v_{out-\text{max}}[V]/n_{out}[\text{digit}]} \right]$$

(2)

と表せる。

以下 ,実験により  $v_{in}$  の変動により振動が増大した場合に対する本手法の有効性を示す。実験条件は ,  $v_{ref}$ =639 digit(1 V 相当)とし ,  $v_{in}$ が 12V から 11.98V に変化したとする。この場合 , (1) と (2) 式より , n[digit]=85 ,  $v_{ref}$   $^{opt}[\text{digit}]$ =635 となる。したがって ,  $v_{in}$ =11.98 V での最適目標電圧値  $v_{ref}$   $^{opt}$  は ,635 digit となる。 $v_{ref}$ を補正せず 639 digit のままの場合(先の結果と同一)と , 補正を行い 635 digit とした場合のステップ応答実験結果を図 7 に重ねて示す。ピーク・ピーク値で 17 digit(26.7 mV 相当)減となる。提案する目標電圧補正を行うことにより ,  $u_{pvm}$  が一定となり  $v_{out}$  の振動が最小化されていることが確認できる。

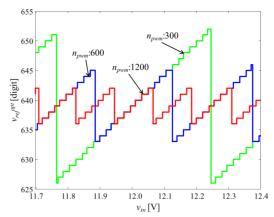

## 入力電圧推定法

前節で述べた(2)式は,入力電圧を含んだ式 となっている。最適目標電圧 v<sub>ref</sub><sup>opt</sup> と入力電圧  $v_{in}$ の関係を図 8 に示す。図 8 では  $n_{vym}=300$ , 600, 1200 digit の場合について示している。 これより,  $v_{in}$  の変動に応じて  $v_{ref}^{opt}$  が周期的 に補正されることがわかる。すなわち目標電 圧補正により ,  $v_{ref}^{opt}$  が変化し , 結果として出 力電圧がわずかに目標電圧と異なる。この補 正による偏差は,入力分解能 $n_{nvm}$ に依存して 大小し, 例えば, npwm =1200 digit のときで は 変動幅が±3 digit(±4.7 mV 相当)となる。 この関係から,提案法では,出力電圧振動に 対する要求性能が与えられた場合,入力分解 能を一意に決定できる。例えば,±5 mV 以内 の振動性能が要求されるなら, $n_{nwm}$ =1200 digit とすれば実現可能である。

以上より,ここでは低コスト化や回路規模の縮小化を目的に,制御入力 $u_{pwm}$ と出力電圧 $v_{out}$ から $v_{in}$ の推定を行う。AD 変換式: $u_{pwm}$ [digit]= $v_{out}$  [V]/ $(v_{in}$  [V]/ $n_{pwm}$  [digit])と,DA 変換式: $v_{out}$  [V]=6.41[V]/ $2^{12}$ [digit] ×  $v_{out}$  [digit]から $v_{in}$ について次式の推定式が導かれる。

$$v_{in}[V] = \frac{6.41[V]}{2^{12}[\text{digit}]} \cdot n_{pwm}[\text{digit}] \cdot \frac{v_{out}[\text{digit}]}{u_{pwm}[\text{digit}]}$$

(3)

(3)式に基づき $v_{in}$ 推定を行った実験結果を図9示す。実験条件は, $n_{pwm}$ = $2^{10}$ , $v_{rel}$ =639 digit とした。この結果より,入力電圧の推定値(平均値)は 12.048 V となり,実測値は 12.046 V であった。実測値に対する推定値の誤差は,0.017%であり,精度よく推定可能であることが確認できた。

図7 ステップ応答実験(定常状態)

図8 入力電圧に対する最適目標電圧

図 9 入力電圧の実測値と推定値の比較

# 5 . 主な発表論文等

## [雑誌論文](計 6 件)

W. Jiang, S. Wang, S. Kan, L. Xie and <u>S. Hashimoto</u>, "Digitally Controlled Multi-Phase Electronic Current Sink," Proc. of The 10th IEEE International Conference on Power Electronics and Drive Systems (PEDS), 查読有, Vol.1, 2013, pp.862-866

S. Hashimoto, H. Saitou and K. Nakajima, "A High Precision Control Based on Learning Algorithm with Reference Model and Disturbance

Observer," Journal of Advanced Science Letters, 查読有, Vol.13, 2012, pp.463-467

S. Hashimoto, S. Naka, Ung S. and N. Honjo, "Generation of Optimal Voltage Reference for Limit Cycle Oscillation in Digital Control-Based

Switching Power Supply," Journal of Energy and Power Engineering, 查読有, Vol.6, No.4, 2012, pp.623-628

S. Hashimoto, S. Sato, S. Naka, K. Motegi and W. Jiang, "Adaptive Identification and Control for Digital Control-Based Switching Power Supply

System," Proc. of Asia-Pacific Power and Energy Engineering Conference (APPEEC2012), 査読有, Vo.4, 2012, S4

S. Hashimoto, S. Naka, U. Sosorhang and N. Honjo, "Generation of Optimal Voltage Reference for Digital Control-Based Switching Power Supply," Proc. of Asia-Pacific Power and Energy Engineering Conference (APPEEC2011), 香読有, Vol.2, 2011

S. Hashimoto, H. Watanabe and K. Nakajima, "Estimation of Physical Parameters using Learning Algorithm in Precision Positioning Control," Journal of Advanced Materials Research, 查読有, Vols.211-212, 2011, pp.469-473

### [学会発表](計 7 件)

蔡華飛,茂木健司,<u>橋本誠司</u>,ディジタル技術による CD-SEM の知能化テンプレートマッチング手法,電気学会第4回栃木支所・群馬支所合同研究発表会資料,2014年3月3日,群馬大学(群馬県桐生市)

安海聡一, 齋藤弘享, 中嶋健治, <u>橋本誠司</u>, モデル規範型ニューラルネットワークによる精密ステージの制御法, 電気学会制御研究会資料, 2013年3月4日, 電気学会本部(東京)

小島侑一郎,<u>橋本誠司</u>,非線形システム同 定法の精密ステージ制御への応用,電気学会 第3回栃木支所・群馬支所合同研究発表会資 料,2013年2月28日,宇都宮大学(栃木県 宇都宮市)

茂木健司,佐藤友紀,中祥司郎,<u>橋本誠司</u>, 負荷変動にロバストなスイッチング電源の ディジタル制御手法,電気学会第2回栃木支 所・群馬支所合同研究発表会資料,2012年3 月1日,桐生文化会館(群馬県桐生市)

入澤健太,<u>橋本誠司</u>,ディジタル制御に基づく DIMC 構造の実現とその適応化手法,電気学会第2回栃木支所・群馬支所合同研究発表会資料,2012年3月1日,桐生文化会館(群馬県桐生市)

N. G. P. Andres, 橋本誠司,外乱オブザーバに基づく内部モデル制御法の多入出力システムへの応用,電気学会第2回栃木支所・群馬支所合同研究発表会資料,2012年3月1日,桐生文化会館(群馬県桐生市)

中祥司郎,佐藤友紀,<u>橋本誠司</u>,ディジタル・アナログ混在スイッチング電源のリミットサイクル振動低減法,平成23年電気学会産業応用部門大会講演論文集,2011年9月8日,琉球大学(沖縄県中頭郡)

### [図書](計 1 件)

涌井伸二,<u>橋本誠司</u>,高梨宏之,中村幸紀, コロナ社,現場で役立つ制御工学の基本, 2012,247(17-18,21-32,164-195,201-214)

## 6. 研究組織

### (1) 研究代表者

橋本 誠司 (HASHIMOTO, Seiji) 群馬大学・理工学研究院・准教授 研究者番号:30331987