# 科学研究費助成事業 研究成果報告書

平成 29 年 6 月 14 日現在

機関番号: 16301

研究種目: 基盤研究(C)(一般)

研究期間: 2013~2016

課題番号: 25330063

研究課題名(和文)プリシリコンテストとポストシリコンテストを併用したタイミング不良診断法の開発

研究課題名(英文)Timing failure diagnosis using pre-silicon test and post-silicon test

#### 研究代表者

高橋 寛 (Takahashi, Hiroshi)

愛媛大学・理工学研究科(工学系)・教授

研究者番号:80226878

交付決定額(研究期間全体):(直接経費) 3,400,000円

研究成果の概要(和文):これまでの縮退故障および遷移故障に対する故障検査のみでは,高速システムオンチップの品質を保証することは困難である。本研究では,抵抗性オープン故障に対する高精度診断用テストとして,2パターン 2ペアテストの概念を提案し,その生成法を提案した。また,診断容易化回路として,アナログバンダリスキャンを適用したオンチップセンサを提案した。さらに,被診断回路のパスの順位に基づく故障診断法を提案した。ベンチマーク回路に対する評価実験結果から,従来法に比べて,高精度な診断用テストが生成可能であること,および良好な故障診断分解能が得られることを示した。

研究成果の概要(英文): It is difficult for the existing methods for the stuck-at faults and the transition delay faults to guarantee the quality of the high-speed system on chips. In this study, we proposed a concept of 2 pattern-2 pair tests as a high quality diagnostic test for resistive open faults. Also we proposed methods for generating the diagnostic tests by using SAT solver and the Simulated Annealing. We proposed an on-chip sensor that is applied by the analog boundary-scan as a design-for diagnosis. Moreover, we proposed a diagnostic method based on the ranking of the sensitized paths. From the experimental results for the benchmark circuits, we show that the proposed methods can generate the high quality diagnostic tests and the proposed diagnosis method can obtain the better diagnostic resolutions compared with the existing methods.

研究分野: 計算機システム

キーワード: ディペンダブルコンピューティング 故障検査 故障診断 オープン故障 タイミング不良

### 1.研究開始当初の背景

半導体の微細化加工技術の進展に伴って、 これまでの縮退故障および遷移故障に対す る故障検査のみでは,製造された高速システ ムオンチップの品質を保証することは困難 である.本研究者らは,これまでに,半断線 故障によって微小な遅延変動が生じること を明らかにし,その故障を検出可能なテスト 生成法を提案した.一方,高速システムオン チップ内の微小な遅延変動が生じる原因(故 障箇所)を指摘する遅延故障診断において, 従来の論理故障診断法および外部解析装置 利用の故障解析法を適用することは容易で はない、したがって、タイミング不良が生じ た高速システムオンチップの故障箇所およ びその原因を調査することは,ますます困難 になっている.更に,タイミング不良の箇所 を高精度に指摘するためには,実チップ(ポ ストシリコン)における遅延変動(トランジ スタばらつきなど)の影響を考慮した自己診 断法に関して新しい取り組みが必要である。

プリシリコンテストにおいて微小な遅延 変動を保持することができる高精度診断用 テストを生成することが必要であること,お よびオンチップセンサを利用したポストシ リコンテストにおいて微小な遅延変動を評 価するために,診断用テストによって活性化 されたパスの長さの変動に着目することが, 組込み自己診断技術として重要であること を認識し,本課題の着想に至った.

# 2.研究の目的

研究の目的は, <u>プリシリコンテストとオン</u> チップセンサを利用したポストシリコンテ ストを併用したタイミング不良に対する診断法を開発することである.

研究期間内に以下のことを明らかにする. 目的1:プリシリコンテストにおいてレイアウト情報を利用した高精度診断用テスト生成法を提案する. 目的 2:オンチップセンサとして,配線の抵抗を計測できる回路を提案する.

目的3:プリシリコンテストにおいて,高精度診断用テストによって活性化されたパスの順位に基づく故障診断法を提案する.また,故障診断法の高精度化法として,機械学習を導入した手法を提案する.

### 3.研究の方法

それぞれの目的に対する研究の方法を述べる。

(1)目的1に対する研究方法:プリシリコンテストにおいてレイアウト情報を利用した高精度診断用テストの生成のために,次の診断用テスト生成法を提案する.

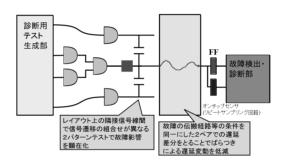

図1に高精度診断用テストの概念を示す.

図1 高精度診断用テストの概念

「2バターン 2ペアテストによる診断用テスト生成法」においては、まず、2パターン 2ペアテスト生成の条件を提案する、提案する条件は、1)目標信号線に信号変化を設定し、その隣接信号線に固定値を設定する2パターンテストであること、2)目標信号線に逆相の信号変化を設定する2パターンテストであること、および3)目標信号線から出力フリップフロップまでの活性化経路が同一であることである。

「2パターン 2ペアテスト」生成法としては、 ドントケアの割り当ての再構成を遅延故障に対するテストパターンに対して行う生成法、 2パターン 2ペアテスト生成の条件を付加回路として表現したテスト生

成用回路を利用した生成法,および 2パターン 2ペアテスト生成の条件を充足可能性問題で表し、それSATソルバーを適用して生成する方法をそれぞれ提案する[論、 発, 発, 21発, 22発].

「IR **ドロップを考慮した診断用テスト生成法」**においては、テストパターン集合からIR ドロップによる信号伝搬遅延時間の変動を受けやすいリスクパターンを選出し、そのテストパターンに対してシミュレーティッドアニーリングに基づくセーフパターンへの変更する[論,発,発].また、この方法の改良方法として、診断用テストの選択問題を0・1整数計画問題に定式化する手法[発,発]および遺伝的アルゴリズムを適応する方法[発]を提案する.

「リーシード法を適用した診断用テストの生成法」では、診断用テストパターンの発生回路としランダムパターン生成回路を利用する場合に、診断分解能を向上するためにランダムパターンのシードを変更するためのリーシード法を適用する手法を提案する[発,発,発].

「診断用テスト集合のテスト分割法」において、テスト時間を短縮するために与えられたテスト集合をゲート出力のトグル回数を評価値として分割する手法を提案する[論].

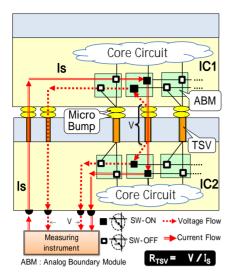

(2)目的2に対する研究方法:オンチップセンサーの開発としては,配線の抵抗値を精密に計測する手法を提案する.具体的には,オンチップセンサーとして,アナログバウンダリスキャン(IEEE1149.4)技術による計測法を拡張して,ICチップ間の相互接続抵抗を高精度に計測する方法を提案する.さらに,提案法の実現可能性を評価するために,まず,小規模回路での評価実験,回路シミュレーションによる評価,およびオンチップセンサーの配線抵抗計測回路の回路設計および実装設計をそれぞれ行う[論,論,論,論,

発, 発, 発, 発, 発].

(3)目的3に対する研究方法:正常回路におけるパスの順位とオンチップセンサを利用したポストシリコンテストにおいて順位付けされた故障回路のパスの順位を比較することによって、タイミング不良の原因となる誤りパスの集合を指摘する故障診断法を提案する[論,発,発,23発].さらに、多変量解析に基づく機械学習を適用した診断法も提案する[発,発,発].

#### 4.研究成果

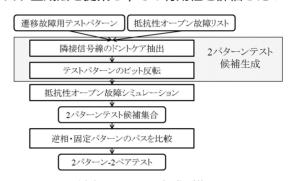

高精度診断用テスト生成法に関する研究成果は,まず下記の流れ図に示す診断用テスト生成法を提案し,その有効性を評価した。

図2 診断用テスト生成手順

評価実験結として,ISCAS89 ベンチマーク 回路において,故障信号線への影響力の強い 隣接信号線2本を選択し,診断用テストを 生成した.テスト生成実験結果を表1に示す.

回路名 対象故障数 テスト生成数 テスト生成 4.519 2.801 59234 61 98 s13207 6.630 76.32 5,060 68.44 s15850 7.215 4,938 9,244 80.32 s35932 11,509 s38417 20,373 18,336 90.00

9,788

68.10

表 1 診断用テスト生成結果

オンチップセンサーの開発成果としては, IEEE1149.4 規格による標準回路構成を変更して「フローティング計測」を実現し,これによりアナログスイッチの ON 抵抗の影響を排除して,高精度計測を可能とした.

提案法の概要を図3に示す.

14,372

s38584

## 図3 提案するオンチップセンサーの概要

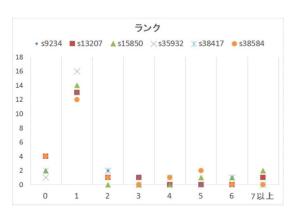

活性化されたパスの順位に基づく故障診断法の成果としては、故障を検出した誤り観測フリップフロップから正常回路のタイミングシミュレーションの情報に基づいて入力側に後方経路追跡を行い、故障の影響が伝搬する最長の経路のみを抽出することによって故障候補を指摘できる手法を開発した.ISCAS'89ベンチマーク回路に対して提案手法を適用した評価実験を行った.結果を図4に示す.図4により回路に存在する故障がランク上位であることが分かる.

図 4 故障診断結果

## 5 . 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

### 〔雑誌論文〕(計 8件)

論 Hanan T. Al-Awadhi, Senling Wang, <u>Yoshinobu Higami</u> and <u>Hiroshi Takahashi</u>, "Pattern Partitioning for Field Testing Considering the Aging Speed ", IEEE Workshop on RTL and High Level Testing, pp.1-6, 2016

論 Senling Wang, Taiga Inoue, Hanan T. Al-Awadhi, <u>Yoshinobu Higami</u> and <u>Hiroshi</u> <u>Takahashi</u>, "A Simulated Annealing based Pattern Selection Method to Handle Power Supply Noise for Resistive Open Fault Diagnosis", Proc. ITC-CSCC2015, pp.592-595, 2015

論 Jun Yamashita, <u>Hiroyuki Yotsuyanagi</u>, Masaki Hashizume, <u>Yoshinobu Higami</u> and <u>Hiroshi Takahashi</u>, "On SAT-based Test Generation for Resistive Open Using Delay Variation Caused by Effect of Adjacent Lines", The 15<sup>th</sup> IEEE Workshop on RTL and High Level Testing, pp.1-6, 2014

論 亀山修一,馬場雅之,<u>樋上喜信</u>,<u>高橋</u> <u>寛</u>,"アナログバウンダリスキャンによる三次 元積層後のTSV抵抗精密計測法",電子情報通 信学会論文誌 D-I, Vol. J97-D-I, No.4, pp.887-890, 2014

論 Shuichi Kameyama, Masayuki Baba, Yoshinobu Higami, and Hiroshi Takahashi, "Accurate Resistance Measuring Method for High Density Post-Bond TSVs in 3D-SIC with Electrical Probes", Proc. International Conference on Electronics Packaging, pp.117-121, 2014

論 Shuichi Kameyama, Masayuki Baba, Yoshinobu Higami, and Hiroshi Takahashi, "Measuring Method for TSV-based Interconnect Resistance in 3D-SIC by Embedded Analog Boundary-Scan Circuit", Journal of Low Power Electronics, Vol.11, No.4, pp.140-146, 2014

論 Koji Yamazaki, Toshiyuki Tsutsumi, <u>Hiroshi Takahashi</u>, <u>Yoshinobu Higami</u>, <u>Hiroyuki Yotsuyanagi</u>, Masaki Hashizume and Kewal K. Saluja, "Diagnosing Resistive Open Faults Using Small Delay Fault Simulation", Proc. 2013 22nd Asian Test Symposium, pp.79-84, 2013

論 Jun Yamashita, <u>Hiroyuki Yotsuyanagi</u>, Masaki Hashizume, <u>Yoshinobu Higami</u>, and <u>Hiroshi Takahashi</u>, "On SAT-based Test Generation for Observing Delay Variation Caused by a Resistive Open Fault and Its Adjacent Lines", The 14<sup>th</sup> IEEE Workshop on RTL and High Level Testing, pp.1-6, 2013 [学会発表](計23件)

発 亀山 修一,王 森レイ,高橋 寛,"三次元積層 ICの TSV 相互接続の評価容易化設計 DFE-アナログバウンダリスキャンによる接続抵抗評価",電子情報通信学会技術研究報告,2017年2月17日,機械振興会館(東京都・港区)

発 香川敬祐,王森レイ,亀山修一,<u>樋上</u> <u>喜信,高橋 寛</u>,"アナログバウンダリスキャンを適用した三次元積層後の TSV 抵抗精密 計測法の計測制度評価",電気関係学会四国 支部連合大会,2016 年 9 月 17 日,徳島大学 (徳島県・徳島市)

発 伊勢幸太郎,<u>四柳浩之</u>,橋爪正樹,<u>樋</u> 上喜信,高橋 寛,"隣接線の信号遷移を用 いる半断線故障判別法の断線位置に対する 有効性調査",電気関係学会四国支部連合大 会,2016年9月17日,徳島大学(徳島県・ 徳島市)

発 王森レイ,香川敬祐,亀山修一,<u>樋上</u> <u>喜信</u>,<u>高橋 寛</u>,"三次元積層後の TSV 抵抗 の精密計測法のアナログ回路設計について", 電子情報通信学会技術研究報告,2016年2月 17日,機械振興会館(東京都・港区)

発 藤谷和依,四柳浩之,橋爪正樹,<u>樋上</u> 喜信,高橋 寛,"論理値割当隣接線の選択 による断線故障用テスト生成時間の削減", 電子情報通信学会技術研究報告,Vol.115, No.449,13-18頁,2016年2月17日,機械 振興会館(東京都・港区) 発 王森レイ,香川敬祐,亀山修一,<u>樋上</u> <u>喜信</u>,高橋 寛,"アナログバウンダリスキャンを用いた三次元積層後のTSV抵抗の精密 計測法の実装について",デザインガイア 2015 -VLSI 設計の新しい大地-,Vol.115, No.339, 31-36頁, 2015年12月1日,長 崎県勤労福祉会館(長崎県・長崎市)

発 伊勢幸太郎, 四柳浩之, 橋爪正樹, 樋上喜信, 高橋 寛, "隣接線の信号遷移による遅延変動を用いる半断線故障の判別法について", デザインガイア 2015 -VLSI 設計の新しい大地-, Vol.115, No.339, 31-36 頁, 2015 年 12 月 1 日, 長崎県勤労福祉会館(長崎県・長崎市)

発 伊勢幸太郎, 四柳浩之, 橋爪正樹, 極上喜信, 高橋 寛, "隣接線の信号遷移を用いる多変量解析による半断線故障の検出可能性について", 平成27年度電気関係学会四国支部大会, 2015年9月26日, 高知工科大学(高知県・香美市)

発 香川敬祐, 王森レイ, 亀山修一, 極上喜信,高橋 寛,"アナログバウンダリスキャンによる 三次元積層後の TSV 抵抗精 密計測法の実装と評価",平成27年度電気関係学会四国支部大会,2015年9月26日,高 知工科大学(高知県・香美市)

発 村上陽紀,宮本夏規, 王森レイ, <u>樋</u> 上喜信,高橋 <u>寛</u>,"組込み自己診断におけるシード候補の生成法",平成27年度電気関係学会四国支部大会,2015年9月26日,高知工科大学(高知県・香美市)

発 宮本夏規, 村上陽紀,王森レイ, <u>樋</u> 上喜信,高橋 <u>寛</u>,"組込み自己診断における遷移故障診断能力の改善法",平成27年度 電気関係学会四国支部大会,2015年9月26日,高知工科大学(高知県・香美市)

発 門田一樹,矢野郁也, 王森レイ,<u>樋</u> 上喜信,高橋 寛,"タイミングシミュレーション情報に基づく故障診断法",平成27年 度電気関係学会四国支部大会,2015年9月 26日,高知工科大学(高知県・香美市)

発 伊勢幸太郎, 四柳浩之, 橋爪正樹, 極上喜信, 高橋 寛, "隣接線の信号遷移を用いる多変量解析による半断線故障 の検出可能性について",平成27年度電気関係学会四国支部大会,2015年9月26日,高知工科大学(高知県・香美市)

発 宮本夏規,村上陽紀,王森レイ,<u>樋上</u> <u>喜信</u>,高橋 <u>寛</u>,大竹哲史,"組込み自己診断におけるテストパターン系列の診断能力に関して",FIT2015(第 14 回情報科学技術フォーラム)第一分冊,273-274頁,2015年9月15日,愛媛大学(愛媛県・松山市)

発 今村亮太,門田一樹,王森レイ,<u>樋上</u> <u>喜信</u>,高橋 <u>寛</u>,"0-1整数計画問題を利用した遅延故障テストの改善",電子情報通信学会総合大会,2015年3月12日.立命館大学(滋賀県・草津市)

発 王森レイ,井上大画,ハナンティアルアワディー,樋上喜信,高橋 寛, "IR-dropを考慮した抵抗性オープン故障の診断用パターンの選択手法",電子情報通信学会技術研究報告,2015年2月13日,機械振興会館(東京都・港区)

発 門田一樹,今村亮太,王森レイ,<u>樋上</u> <u>喜信</u>,<u>高橋</u>寛,"遺伝的アルゴリズムを利 用した診断用テスト生成",平成26年度電気 関係学会四国支部大会,2014年9月13日, 徳島大学(徳島県・徳島市)

発 村上陽紀,宮本夏規,王森レイ,<u>樋上</u> <u>喜信</u>,高橋<u>寛</u>,"0-1整数計画問題を利用した診断用テスト生成システムの開発",平成 26年度電気関係学会四国支部大会,2014年9 月13日,徳島大学(徳島県・徳島市)

発 竹田和生,王森レイ,<u>樋上喜信</u>,<u>高橋</u> <u>寛</u>,"オンチップセンサを利用した抵抗性オープン故障診断",平成26年度電気関係学会 四国支部大会,2014年9月13日,徳島大学 (徳島県・徳島市)

発 井上大画, 王森レイ, 樋上喜信, 高橋

夏, "消費電力制約下での焼きなまし法を利用したテストパターン変更法, 平成 26 年度電気関係学会四国支部大会, 2014 年 9 月 13 日, 徳島大学(徳島県・徳島市)

21発 山下淳,<u>四柳浩之</u>,橋爪正樹,<u>樋上</u> <u>喜信</u>,<u>高橋</u>寛,"SAT手法による隣接線 影響を考慮した微小遅延故障検査用テスト パターン生成に関する一考察",平成 25 年 度電気関係学会四国支部大会,2013年9月2 1日(徳島県・徳島市)

22発 松川翔平,<u>高橋 寛</u>,<u>樋上喜信</u>,四柳浩之,橋爪正樹,"抵抗性オープン故障に対する診断用テスト生成",平成25年度電気関係学会四国支部大会,2013年9月21日(徳島県・徳島市)

23発 竹田和生,<u>樋上喜信</u>,<u>高橋 寛</u>,"抵 抗性オープン故障診断のための後方追跡", 平成 25 年度電気関係学会四国支部大会, 2013年9月21日(徳島県・徳島市)

[図書](計 0件)

〔産業財産権〕

出願状況(計 0件)

取得状況(計 0件)

〔その他〕

ホームページ等

- 6. 研究組織

- (1)研究代表者

高橋 寛(Takahashi Hiroshi)

愛媛大学・理工学研究科 (工学系)・教授

研究者番号:80226878

(2)研究分担者

樋上喜信(Higami Yoshinobu)

愛媛大学・理工学研究科 (工学系)・教授

研究者番号: 40304654

四柳浩之(Yotsuyanagi Hiroyuki)

徳島大学・大学院理工学研究部・准教授

研究者番号:90304550