# 科研費

# 科学研究費助成事業 研究成果報告書

平成 27 年 9 月 18 日現在

機関番号: 13904 研究種目: 若手研究(B) 研究期間: 2013~2014

課題番号: 25820141

研究課題名(和文)微小神経電位プローブに向けた超高密度アナログフロントエンドアレイ

研究課題名(英文)A high-density analog frontend array for neural interfaces

研究代表者

秋田 一平 (Akita, Ippei)

豊橋技術科学大学・工学(系)研究科(研究院)・助教

研究者番号:10612385

交付決定額(研究期間全体):(直接経費) 3,300,000円

研究成果の概要(和文):脳神経電位計測システムを体内に埋込むことが出来るまで小型に実現することは、Brain-Machine Interface(BMI)実現のための重要な要素技術となる。本研究は、そのような応用に向けた電極アレイのための、超高密度信号処理回路の開発を目的としており、提案する新規デジタル補正技術に基づくアナログ回路の高精度化手法について、その指導原理を明らかにした後、神経電位アンプやA/D 変換器への適用し、LSI試作・評価を通じて低消費電力化、小型化、高精度化を実証した。また、これらを基盤としたアレイLSIの設計・試作も行っており、今後の応用計測や実用化研究への発展が期待される。

研究成果の概要(英文): Development of implantable neural interface devices is necessary to realize Brain-Machine Interface (BMI) systems, which are expected to enhance human's quality of life (QoL). This study is aimed at designing such devices with ultra-low power operation and small chip area for arrayed analog front-ends (AFEs), and a novel digital calibration scheme has been proposed. This technique can provide high-accuracy characteristic of AFEs, such as neural amplifiers or analog-to-digital converters (ADCs), without paying additional power and die area, and its effectiveness is confirmed through fabrication and evaluation of prototype chips in silicon CMOS technology. Furthermore, based on above techniques, an arrayed AFE LSI has been also designed and fabricated and these results will enable future multi-channel fully-implantable neural interface devices.

研究分野: アナログ・デジタル集積回路設計

キーワード: アナログ オペアンプ AD変換器 低消費電力化 小型化

#### 1.研究開始当初の背景

#### 2.研究の目的

微小プローブアレイのための超小型・低消費電力 AFE の実現のための回路・デバイス技術の創出を行う。

# 3. 研究の方法

上記目的のために、主に、1 c h 当たりの AFE の最適化に取り組んだ。特に、AFE の 精度を維持しながら、従来よりも小型・低消費電力実装するためのデジタルキャリブレーション技術を創出し、関連する雑音低減回路、電源回路等の開発を行った。また、実用 化のためには、生体適合性の高い実装技術が必須であることから、これにも着手した。

# 4. 研究成果

# 神経電位アンプの検討:

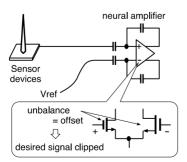

図1神経電位アンプにおける高精度化回路技術

になるようにデジタルキャリブレーションを行うことで、高精度かつ小型な神経電位アンプを実現可能となる。また、十分な精度を実現するための詳細な指導原理を明らかにした。また、LSI 試作・評価を通じて本提案技術の有効性を確認している(主に雑誌論文[3])。

#### AD 変換器の検討:

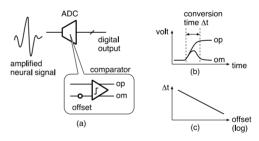

上記に示した再構成可能な差動入力段を AD 変換器に利用される比較器 (コンパレータ) に適用した。比較器は、アナログ信号をデジ タル信号に変換する際に利用される回路ブ ロックであり、入力電圧差を検出してその大 小を判別することで、デジタルの 0/1 を決定 する重要な回路ブロックである。そのため、 神経電位アンプ同様、ここにオフセット電圧 が存在すると、誤判定が生じアナログ・デジ タル変換結果に大きな誤差が発生してしま う。非線形回路である比較器に、本提案のデ ジタルキャリブレーション技術を適用する 際は、線形回路である神経電位アンプとは異 なり、オフセットの検出手法に工夫が必要で ある。本技術においては、これを解決するた めに、比較器の判定確定時間が、入力電圧差 (つまり、オフセット電圧)に依存すること を利用して、この時間計測を行うことで正確 なオフセット電圧の計測と正確なデジタル キャリブレーションを実現した。本技術は試 作LSIの評価を通じてその有効性が確認され ている(主に雑誌論文[2])。

図 2 デジタルキャリブレーション技術を用いた再構成可能入力段の AD 変換器への適用(a): (b)オフセット電圧の時間遅延検出手法と(c)それの関係概略

# 要素技術等:

低消費電力 AFE などに向けた安定電源回路の検討を行い、電源の先につながる回路(負荷)の電力消費の程度は、システムの制御信号等の情報から事前に推定することが可能であるという知見を利用し、従来必要とされていた受動素子を大幅に小さくすることが可能となった。本技術についても、試作 LSI の評価を通じてその有効性を実証した(主に、雑誌論文[4])。

一方で、神経電位アンプに、高インピーダンスセンサが接続された場合に問題となる電流雑音の問題を解決する手法として、時間ゲ

ーティングによる簡易な方法で回避する技術を提案し、ディスクリート部品からなる回路の実測結果からその有効性を確認した(主に、雑誌論文[1])。

# 多チャネルシステムの設計:

以上の要素技術の知見に基づいて、多チャネル神経電位計測システムに向けた、AFE アレイ LSI の設計・試作を行った。本施策 LSI は各チャネルに神経電位アンプ、特性可変フィルタ (低域通過フィルタ/帯域通過フィルタの相互切り替え) 低消費電力 AD 変換器等を備えており、また、これらの回路における特性を所用仕様内に維持するためのデジタルキャリプレーション回路を搭載している。

# 5 . 主な発表論文等 (研究代表者、研究分担者及び連携研究者に は下線)

#### 〔雑誌論文〕(計 4件)

- [1] **Ippei Akita**, Makoto Ishida, "A current noise reduction technique in chopper instrumentation amplifier for high-impedance sensors," *IEICE Electron. Express (ELEX)*, vol.12, no.11, pp.1-5, June 2015.

- [2] Takayuki Okazawa, <u>Ippei Akita</u>, Makoto Ishida, "A digitally calibrated dynamic comparator using time-domain offset detection," *Analog Integr. Circuits Signal Process.* (AICSP), vol. 81, no. 3, pp. 561-570, Dec. 2014.

- [3] **Ippei Akita**, Makoto Ishida, "A chopper-stabilized instrumentation amplifier using area-efficient self-trimming technique," *Analog Integr. Circuits Signal Process. (AICSP)*, vol.81, no. 3, pp. 571-582, Dec. 2014.

- [4] **Ippei Akita**, Shochi Asai, Makoto Ishida, "A low-power output-capacitor-less low-dropout regulator with adjustable charge injection technique for on-off keying transmitters," *Jpn. J. Appl. Phys. (JJAP)*, vol. 53, pp. 04EE17-1-5, April 2014.

### [学会発表](計14件)

- [1] Kenji Okabe, **Ippei Akita**, Shota Yamagiwa, Takeshi Kawano and Makoto Ishida, "A thin film flexible antenna with CMOS rectifier chip for RF-powered implantable neural interfaces," in Proc. *Int. Conf. Solid-State Sensors, Actuators, and Microsystems (Transducers)*, Anchorage, Alaska, June 2015. (accepted)

- [2] Horagodage Prabhith Jeewan, 岡部謙志, **秋田一平**, 山際 翔太, 河野 剛士, 石田誠, "完全埋込神経インターフェースデバイスに向けたフレキシブル基板上へのフリップチップ実装技術," 応用物理学会, 11p-D6-9, 神奈川, March. 2015.

- [3] 岡部謙志, **秋田一平**, 浅井翔地, 石田誠, "ワイヤレス神経インターフェースに向けた無線電力伝送用パリレンフィルムアンテナ," 集積化 MEMS シンポジウム,22PM1-C5, 松江, Oct. 2014.

- [4] Kenji Okabe, <u>Ippei Akita</u>, Shochi Asai, and Makoto Ishida, "A flexible antenna using a parylene film for wireless powered neural recording devices," in Proc. *Int. Conf. SolidState Devices and Materials* (SSDM), Tsukuba, Japan, D-4-3 pp. 972-973, Sept. 2014.

- [5] 岡部謙志, **秋田一平**, 石田誠, "無線神経 インターフェースに向けたパリレンフ ィルムアンテナの設計," 応用物理学会, 18a-PA2-12、札幌, Sept. 2014.

- [6] 藤澤良太, **秋田一平**, 石田誠, "SAR ロジックの低消費電力化に関する検討,"電子情報通信学会 第 36 回アナログRF研究会、屋久島, July 2014.

- [7] Kenji Okabe, <u>Ippei Akita</u>, and Makoto Ishida, "Design of a flexible antenna using parylene film for implantable sensor nodes on brain surface," in Proc. *Asia-Pacific Conference on Transducers and Micro/Nano Technologies (APCOT)*, E-T05-0250, Daegu, Korea, June 2014.

- [8] 岡澤貴之, **秋田一平**, 石田誠, "オフセット自動補償型コンパレータにおける時間ドメインオフセット検出技術," 信学技報 ICD2013-102, p.9, Jan. 2014.

- [9] <u>Ippei Akita</u>, "Analog mixed-signal circuit technique for micro/nano sensor devices," IEICE Technical Reports, ICD2014-101, Kyoto, pp.7-8, January 2014.(invited)

- [10] 岡部謙志, **秋田一平**, 石田誠, "体内埋め 込みに向けた小型オンチップアンテナ," 信学技報 ICD2013-104, p.13, 京都, Jan. 2014.

- [11] ハイビヒシャム, **秋田一平**, 石田誠, "低 雑音・小面積 3 段オペアンプのための位 相補償技術," 信学技報 ICD2013-111, 京都, p.29, Jan. 2014.

- [12] Hicham Haibi, **Ippei Akita**, and Makoto Ishida, "A 27-nV/√Hz 0.015-mm² three-stage operational amplifier with split active-feedback compensation," in Proc. *IEEE Asian Solid-State Circuits Conf.* (A-SSCC), Singapore, pp. 365-368, Nov. 2013.

- [13] Takayuki Okazawa, **Ippei Akita**, and Makoto Ishida, "A low-offset-voltage dynamic comparator using automatic differential-pair matching for low-power ADCs," in Proc. *Int. Conf. Analog VLSI Circuits* (AVIC), Montreal, Canada, pp. 47-51, Oct. 2013.

- [14] **Ippei Akita**, Shochi Asai, and Makoto Ishida, "A low-power capacitor-less LDO regulator with adjustable charge injection

technique for OOK transmitter," in Proc. *Int. Conf. SolidState Devices and Materials* (SSDM), Fukuoka, Japan, H-6-2, pp. 904-905, Sept. 2013.

# [図書](計 0件) 〔産業財産権〕 出願状況(計 0件) 名称: 発明者: 権利者: 種類: 番号: 出願年月日: 国内外の別: 取得状況(計 0件) 名称: 発明者: 権利者: 種類: 番号: 出願年月日: 取得年月日: 国内外の別: 〔その他〕 http://www.ee.tut.ac.jp/~akita 6. 研究組織 (1)研究代表者 秋田一平(Ippei Akita) 豊橋技術科学大学・大学院工学研究科・助 研究者番号:10612385 (2)研究分担者 ( ) 研究者番号: (3)連携研究者

(

研究者番号:

)