# 科学研究費助成事業 研究成果報告書

平成 29 年 6 月 12 日現在

機関番号: 11501

研究種目: 基盤研究(C)(一般)

研究期間: 2014~2016

課題番号: 26330058

研究課題名(和文)細粒度分割型三次元積層技術による高エネルギー効率プロセッサの設計空間探索

研究課題名(英文) Design space exploration of highly energy efficient processors by fine-grain 3-D IC stacking technologies

研究代表者

多田 十兵衛 (Tada, Jubee)

山形大学・大学院理工学研究科・助教

研究者番号:30361273

交付決定額(研究期間全体):(直接経費) 3,600,000円

研究成果の概要(和文):本研究の目的は、細粒度分割型三次元積層技術を用いることにより高エネルギー効率のプロセッサを実現することである。本研究では、まず三次元積層技術によりプロセッサ構成要素の性能向上を図った。その結果、細粒度分割を行う事により、二次元実装の場合と比較して演算器の性能が最大で20%向上し、消費電力が最大10%削減可能であることが示された。次に、複数の演算器から構成される計算ノードの三次元積層技術による高エネルギー効率化を目指し、細粒度分割による回路分割手法の検討および設計空間探索を行った。その結果、二次元実装の場合と比較して性能が最大で8%向上し、消費電力が最大18%削減可能であることが示された。

研究成果の概要(英文): The purpose of this study is to realize a highly energy efficient processor by using a fine-grain 3-D IC stacking technology. At first, this study aimed to improve components of the processor by the 3-D IC stacking. As a result, it has been shown that the fine-grain partitioning of the components could improve the performance and the power consumption of the arithmetic unit. As compared to the 2-D implementation, the 3-D stacked arithmetic unit improved the performance up to 20%, and the power consumption up to 10%. Next, in order to improve the energy efficient of the computing node which has several floating-point units, the fine-grain circuit partitioning method was considered and the design space was explored. As a result, As compared to the 2-D implementation, the 3-D stacked computing node achieved an 8% performance improvement and an 18% power consumption reduction in maximum.

研究分野: 計算機アーキテクチャ

キーワード: 計算機アーキテクチャ 三次元積層技術 集積回路設計

#### 1.研究開始当初の背景

近年、シリコン貫通電極(Through Silicon Via, 以下 TSV)を用いた三次元積層集積回路が注目されている。従来、集積回路はシリコン基板に平面上に実装されてきたが、TSV 技術が確立されたことにより、複数のシリコン基板を積層して接続することが可能といる。三次元積層集積回路の利点としては、実面積の縮小、高メモリ帯域の実現、異種混合集積などが挙げられる。これらの利点はプロセッサの高性能化に大きく寄与するものであるため、これまで様々な三次元積層型プロセッサが提案されてきた。

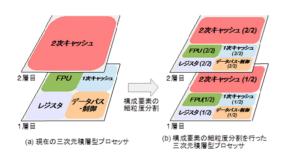

しかしながら、これまでの三次元積層型プロセッサは、図 1(a)に示すように複数のプロセッサコアを単に積層したもの、あるいは二次キャッシュなどの大きな面積を占める構成要素を分離して積層することで実装面積の縮小・高メモリ帯域の実現を目指す粗粒度分割を行ったものが主であった。

しかし、これまでの研究代表者・分担者らの研究により、浮動小数点演算器やキャッシュメモリなどのプロセッサの構成要素に対して細粒度での分割を行う事により、その処理性能・消費電力が 2~4 割程度向上することが示されている。本研究課題ではこれらの研究を発展させ、図1(b)に示すようにプロセッサの各構成要素を分割し、三次元空間上での最適な配置を行う事で高処理性能化・ギー効率化を目指す。

図1:三次元積層型プロセッサ

#### 2.研究の目的

これまでの研究代表者・分担者らの研究により、プロセッサの構成要素の細粒度分割を行う際に、どのように分割を行うかにより性能が大きく異なることが示されている。一方、プロセッサ内の複数の構成要素を細粒度分割する場合、分割された構成要素間をどのように組み合わせるかがプロセッサの性能に大きく影響すると予想される。性能を向上させるためには三次元空間上での配置の最適化を行う必要があるため、この設計空間探索が重要である。

そこで本研究課題では、大きく分けて二つ の課題について取り組み、プロセッサの高エ ネルギー効率化を図る。一つは細粒度分割によるプロセッサ構成要素の性能向上である。これまでの研究で知見が得られているFPUやキャッシュメモリに加え、レジスタファイルやデータパス・制御部などのプロセッサ構成要素に対して細粒度分割を行い、それぞれの構成要素に最適な分割手法を検討する。もう一つは分割した構成要素をどのように組み合わせてプロセッサを再構成する配置によりプロセッサの性能は大きく変化することが予想されるため、様々な配置について検討を行い、その性能を評価する。

## 3.研究の方法

(1)プロセッサ構成要素の細粒度分割手法の検討

高性能ワークステーション上で VDEC(大規模集積システム設計教育研究センター)が提供する回路シミュレータを用い、細粒度分割によるプロセッサ構成要素の処理性能・消費電力の向上を試みる。

これまでの研究代表者らの研究により、細粒度分割の際にどのように回路を分割するかにより回路の性能・消費電力が大きく変化することが示されている。本研究では、プロセッサの各構成要素について最適な回路分割手法の検討を行う。例えばレジスタファイルの分割については、各層ごとに数個のレジスタを配置する手法・レジスタを数ビット幅で分割する手法などが考えられる。

またデータパス・制御部については、パイプラインごとに各層に配置する方法・パイプラインのステージ単位で分割する手法などが考えられる。このように、プロセッサの各構成要素に対して、その処理性能・消費電力を大きく向上させる細粒度分割手法について検討を行う。

#### (2)三次元積層型プロセッサの設計空間探索

細粒度分割を行ったプロセッサの構成要素について、プロセッサの処理性能・消費電力の向上を目的として三次元空間上での配置を最適化する設計空間探索を行う。研究代表者および研究分担者は、これまで三次元積層型キャッシュメモリの開発など、三次元空間上でのプロセッサ構成要素の配置が処理性能・消費電力へ与える影響についての研究を行ってきた。

プロセッサ構成要素の細粒度分割の結果を踏まえ、細粒度分割を行ったレジスタ、データパス・制御部、FPU およびキャッシュメモリなどを三次元空間上に様々に組み合わせて配置する。それぞれの場合について、各層での配線長や必要な TSV 数などのパラメータ抽出を行い、プロセッサシミュレータを用いてプロセッサの性能への影響を評価し、最もエネルギー効率を高めることが可能な配置手法を求める。

(3)チップ試作・評価およびプロセッサ設計へのフィードバック

設計した三次元積層型プロセッサについて、それぞれの層ごとにチップ試作を行い、性能を評価する。設計には VDEC (大規模集積回路設計教育センター)が提供する LSI 設計のための各種 EDA ツールを用い、VDEC を通じてチップ試作を行う。試作したチップは、VDEC の設備を用いて処理性能および消費電力を評価する。

評価により得られたデータと回路シミュレータで得られたデータの比較検討を行い、その結果を細粒度分割手法・設計空間探索へフィードバックする。再度三次元積層型プロセッサの設計を行い、チップを試作・評価する。

## 4.研究成果

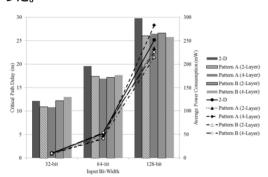

(1)プロセッサ構成要素の細粒度分割手法の 検討、および分割後の構成要素の三次元空間 上での配置の最適化を試みる設計空間探索 を行った。プロセッサの構成要素について、 回路規模を変化させた場合の細粒度分割手 法の影響を調査することを目的とし、三次元 積層型乗算器のビット幅を変化させた場合 の性能への影響について研究を行った。図 1 に示すように、細粒度分割を行う事により、 二次元実装の場合と比較して乗算器の性能 が最大 13%向上し、消費電力が最大 10%削減 可能であることが示された。また、演算回路 の規模および複雑さにより有効な分割手法 が異なることが示され、構成要素の細粒度分 割の研究を進める上での指針となった。研究 成果は国際会議 IEEE 3DIC 2014 で発表を行 った。

図1:細粒度分割による乗算器の性能評価

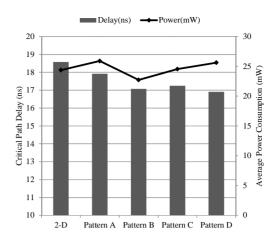

(2)三次元積層型浮動小数点演算器の設計を行い、その性能を評価した。図2に示すように、三次元積層技術により浮動小数点除算器の性能が従来の二次元実装に比べ最大8%向上し、また最大7%の消費電力の削減が可能であることを示した。また、図3に示すように、浮動小数点乗算器において最大20%の性能向上が達成可能であることを示した。研究成果は国際会議IEEE 3DIC 2015 および電子情報通信学会ICD研究会でそれぞれ発表を行った。

図 2:三次元積層型浮動小数点除算器の性能 および電力評価

図 3:三次元積層型浮動小数点乗算器の性能 評価

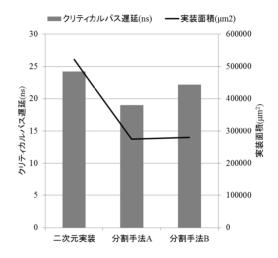

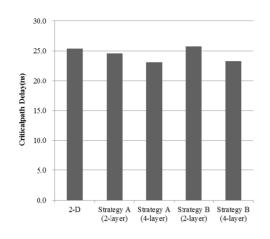

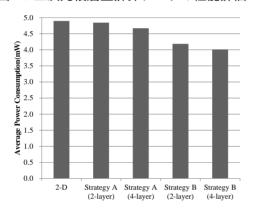

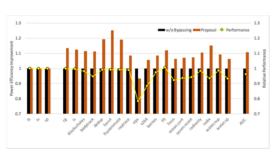

(3)これらの研究成果を踏まえ、複数の演算 器から構成される計算ノードの低消費電力 化および高性能化を目指し、新たに細粒度分 割による回路分割手法および配置手法を提 案した。提案手法に基づいて三次元積層型計 算ノードの設計・評価を行い、図4および図 5 に示すように三次元積層技術により計算ノ ードの性能が最大で8%向上し、消費電力を 最大 18%削減可能であることを示した。また、 三次元積層技術を用いた広帯域メモリを使 用する際、プロセッサのラストレベルキャッ シュを条件に応じてバイパスすることによ り、図6に示すように最大で25%エネルギー 効率を改善可能であることを示した。研究成 果はそれぞれ国際会議 HEART2016、国際学会 ACM の論文誌 SIGARCH Computer Architecture News、および国際会議 IEEE 3DIC 2016 で発 表した。

## 図4:三次元積層型計算ノードの性能評価

図 5:三次元積層型計算ノードの電力評価

図 6:三次元積層型高帯域メモリ使用時における LLC バイパスによる消費エネルギー削減

## 5. 主な発表論文等

## [雑誌論文](計4件)

<u>Jubee Tada</u>, Maiki Hosokawa, <u>Ryusuke Egawa</u> and Hiroaki Kobayashi, "Effects of Stacking Granularity on 3D Stacked Floatingpoint Fused Multiply Add Units", ACM SIGARCH Computer Architecture News, Vol.44, no. 4, pp. 62-67, Sep. 2016, 查

Ryusuke Egawa, Wataru Uno, Masayuki Sato, Jubee Tada, and Hiroaki Kobayashi, "A Power-Aware LLC Control Mechanism for 3D-Stacked Memory Subsystems", IEEE International Conference on 3D System Integration (3DIC2016), pp.1-4, Nov. 2016,

## 杳読有

Jubee Tada, Ryusuke Egawa and Hiroaki Kobayashi, "Design of a 3-D Stacked Floating-point Goldschmidt Divider", IEEE International Conference on 3D System Integration (3DIC2015), pp.1-4, Aug. 2015, 香蒜有

Jubee Tada, Ryusuke Egawa and Hiroaki Kobayashi, "An Impact of Circuit Scale on the Performance of 3-D Stacked Arithmetic Units", IEEE International Conference on 3D System Integration (3DIC2014), Dec. pp.1-5, 2014, 查読有

## [学会発表](計2件)

Jubee Tada, Maiki Hosokawa, Ryusuke Egawa and Hiroaki Kobayashi, "Effects of Stacking Granularity on 3D Stacked Floatingpoint Fused Multiply Add Units", Proceedings of International Symposium on Highly-Efficient Accelerators and Reconfigurable Technologies (HEART2016), 香港(中国), July 26 2016

細川磨生,<u>多田十兵衛</u>,<u>江川隆輔</u>,小林 広明

三次元積層型浮動小数点積和演算器の回路 分割手法の検討,電子情報通信学会 ICD 研究 会,作並温泉一の坊(宮城県仙台市), Oct. 26 2015

[図書](計0件)

# 〔産業財産権〕

出願状況(計0件)

取得状況(計0件)

〔その他〕 ホームページ等

#### 6.研究組織

## (1)研究代表者

多田 十兵衛 (TADA, Jubee) 山形大学・大学院理工学研究科・助教

研究者番号:30361273

## (2)研究分担者

江川 隆輔 ( EGAWA, Ryusuke ) 東北大学・サイバーサイエンスセンター・ 准教授

研究者番号: 80374990