#### 科学研究費助成事業 研究成果報告書

平成 28 年 5 月 2 0 日現在

機関番号: 10101

研究種目: 挑戦的萌芽研究 研究期間: 2014~2015 課題番号: 26630141

研究課題名(和文)サイドゲート制御型抵抗変化メモリの開拓

研究課題名(英文)Development of a new resistive memory controlled by a sidegate

研究代表者

高橋 庸夫 (Takahashi, Yasuo)

北海道大学・情報科学研究科・教授

研究者番号:90374610

交付決定額(研究期間全体):(直接経費) 3,000,000円

研究成果の概要(和文): ニューラルネット応用に適用可能な抵抗変化メモリ(ReRAM)実現に向けて、制御端子による抵抗変化の可能性について、その動作原理の確認から見通しを得た。

RERAM開発では、動作原理の不明確さが実用化の壁となっている。ナノスケールで生じる構造変化の把握が難しいためで、解決法として、TEM中でReRAMを動作させて電気特性と構造変化の対応を取るTEMその場観察法がある。これまでは2端子ReRAMに対して有効性が示されてされてきた。今回、多端子に対応可能なTEMその場観察技術を構築し、Cu/WOxu系のReRAMに適用してCuフィラメントの成長を確認し、その機構から制御ゲートが機能する可能性を示した。

研究成果の概要(英文):In order to realize resistive random access memories (ReRAMs) usable to neural-network application, we achieved great advance showing the possibility of resistance change by the use of a control terminal in multiple-terminal ReRAM devices. One of the biggest problems of development of ReRAMs is the unclearness of the operation mechanisms because it is very difficult to find out structural changes occurring in nano-scale area. To overcome the problem, we have employed in-situ transmission electron microscopy (TEM) technology in which electrical characteristics are measured during TEM observation. Although the in-situ TEM has been used for two-terminal devices, we developed a new system applicable to multiple-terminal devices. By employing the system to analyze Cu-filament formation mechanism in the Cu/WOx ReRAM, we found that the mechanism strongly suggest the possibility of filament formation caused by the electric field from the control

研究分野: 電子工学

terminal.

キーワード: 抵抗変化メモリ 多値メモリ 不揮発性機能デバイス ニューラル素子 電子顕微鏡

#### 1. 研究開始当初の背景

LSI として広範なシリコン(Si)を中心とし た集積化半導体デバイスの進展は著しく、自 由な情報流通できる環境が整いつつある。ビ ッグデータの解析・利用や IOT が重視され、 便利な社会の実現は、全て Si 集積回路を基盤 としたものである。しかし、微細化が限界に 近づき、集積化の進展による性能向上が見込 めなくなりつつある。一方では、高度で高速 な情報処理は、多くのデバイスを高速で動作 させることを原理としているため、情報処理 によるエネルギー消費が膨大になりつつあ り、人類の持続的な発展のためには、省電力 化は必須である。これと同時に、膨大な情報 の中から自分に必要な情報を効率的に取得 する手法の確立が誰にでもできる形で実現 されることが強く望まれている。加えて、処 理する情報量が増えれば、動作する集積化素 子も膨大になるため、エラーが起きる確率が 増え、システムの高度化と素子数の増大は、 システムの確度(正確な動作)を保証するこ とを困難にする。これらの相反する要望を実 現ためには、従来の Si-CMOLSI とは異なる 仕組みで機能する低電力でフレキシブルな 新デバイスが必須である。

# 2. 研究の目的

上に述べた情報処理を実現するには、高い 機能性とともに、フレキシブルで冗長性の高 いシステムの構築が必要である。このために は、ニューラルネットワーク的な学習により 最適化を計っていくようなシステムが必要 になるが、現状では、これに適したハードウ エアが無い。人工知能と称して、デジタル CMOSLSI による CPU を用いて、ソフトウ エアでニューラルネットを構築する試みが あり、成功を収めているように見えるが、こ れを人類が多用すれば、膨大な消費電力を費 やすことになる。この事実は、Google などの データセンターの膨大な消費電力を見れば 明らかであり、原発をいくら新設しても足り ない。ここでは、ニューラルネットワークに 適した新たなデバイスの構築を目指した。

ニューラルネットで重要なのは、刺激の強さによりシナプス結合の強さが変わることであり、電子デバイスで置き換えることに対応えると、例えば抵抗値が変化することに対応する。しかも、省電力に動作するためには、この抵抗値は電源が切れても保存させるが、このような電源無で状態を保存されているが、残念ながらデジタルデータ(0と1)の記憶に限定されて確立されており、アナログデータには対応していない。各種の大口でで、抵抗変化メモリ(ReRAM)は、その書き込み方によって、アナログ値を記憶することが可能である。

本研究の目的は、この ReRAM をアナログ値の記憶に用いることを考える。加えて、従来の ReRAM は、2 端子のデバイスであり、

アナログ抵抗値の書込みが複雑になる。これを回避する目的で、トランジスタのように新たな制御端子を追加した3端子構成とし、この端子への入力により抵抗値を可変にする(ReRAM として、抵抗値は不揮発に保存される)デバイスの開発を目指した。その際、ReRAM はいまだその動作メカニズムが不り確であることが課題となっているデバイスであることから、単に機能が実現されても、その機能を保証する物理的な機構が明らかにならない限り、広範に使われることは無いという視点に立って、その動作原理の解明も含めた検討を行うこととした。

#### 3. 研究の方法

上記の目的のため、以下の検討を行うこととした。(1)トランジスタを埋め込んだReRAM素子による、アナログ値の記憶とその制御性の確立。(2)3端子ReRAMデバイス開拓とその原理確立を目指した検討。

具体的には、(1)の ReRAM 素子は、Si 基 板上に MOSFET を作製し、その Al 配線上に Cu/MoOx の ReRAM を作製した。ReRAM は、書込み時の電流の大きさで、高抵抗から 低抵抗に変わる際に抵抗値を変えて書き込 むことができることは知られているが、個別 に作製すると、その両端に付随する寄生容量 が大きくなる。ReRAM の抵抗可変な動作が ゆっくりと生じれば問題はないが、実用が見 込まれているデバイスであることから想像 できるように、ナノ秒から1 usec 以下の応答 速度を持つ。したがって、低抵抗にスイッチ する際に寄生容量に充電された電荷が一気 に ReRAM に流れ込むため、大きな電流が流 れてしまい、書込み電流の制御ができないと いう問題がある。これを回避するために、 ReRAM の直下に MOSFET を取り付け、 ReRAM と MOSFET 間の寄生容量を小さく 抑え、MOSFET の飽和特性により流れる電 流を制限し、精度良くアナログ抵抗値を書き 込もうという思想である。MOSFET の飽和 電流値は、ゲート電圧で制御できるので、こ の素子構成で自由な書き込を可能にするも のである。

(2)の制御端子を付加した3端子 ReRAM の開拓に向けては、まず、多端子デバイスの 動作機構を透過型電子顕微鏡 (TEM) 内で観 察する手法の構築から行う。我々は、別の研 究計画により、TEM 内で ReRAM を動作さ せ、その抵抗変化動作中に ReRAM セル内で 生じる現象のその場観察に成功している。す なわち、抵抗変化の電気的特性の測定と同時 に TEM 観察を行うことに成功している。し かし、この評価は通常の断面 TEM 観察用サ ンプルに、測定用の可動探針を当てて評価す る手法で行っているため、2端子までの評価 であり、多端子化は難しい。本研究でターゲ ットとする3端子デバイスや、これを用いて 構築するニューラルネットでは、さらなる端 子数が必要になることは明白であり、従来手

法での対応には無理がある。したがって、ここでは、多端子に対応可能な TEM その場観察システムを構築する。次いで、これをCu/WOx の ReRAM デバイスに適用して、ReRAM の動作時の構造変化を可視化することとした。

# 4. 研究成果

- (1) ReRAM 素子によるアナログ値の記憶

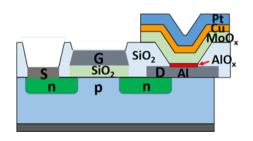

- ① MOSFET 搭載 ReRAM デバイスの作成 ReRAM の直下に MOSFET を設置し、電流を迅速に制限することでオーバーシュート電流を制御し、本研究目的のアナログ値の記憶(データの多値化)の実現を検討した。作製したデバイスの模式的な断面図を図1に示す。

SiO $_2$ /Si 基板に n チャネル MOSFET(チャネル長 L=2 $\mu$ m, チャネル幅 W=6 $\mu$ m, ゲート酸化膜厚 tox=25nm)を作成後、そのドレイン端子から Al-Si 電極パッドを引き出した後、層間絶縁層として SiO $_2$  を堆積した。この Al-Si パッド上にスルーホール(直径 $\phi$ =4 $\sim$ 64 $\mu$ m)を形成した。ReRAM の二層絶縁層構造の一層目となる AlO $_x$  を形成するため、下部電極となる Al-Si の表面を O $_2$  プラズマ処理で酸化した。その後、スルーホール内に反応性スパッタリング法で二層目の絶縁層である MoO $_x$  20 nm、スパッタリング法でフィラメント要素となる Cu 30nm、上部電極 Pt 100 nm を堆積し ReRAM デバイスを作製した(図 1)。

図 1 MOSFET を搭載した基板上に作成した Pt/Cu/MoOx/Al<sub>2</sub>O<sub>3</sub>/Al 構造の ReRAM デバイスの断面模式図

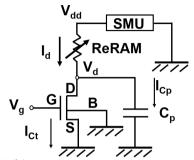

等価回路で表示すると図2のようになる。 測定は、ゲート電圧  $V_g$  を印加し MOSFET の飽和特性でドレイン電流を制限し、ソー スメジャーユニット(SMU)で電圧  $V_{dd}$  を印 加して、ReRAM に流れる電流  $I_d$  を測定し た。

ReRAM の抵抗は、SET 動作直後に高速に且つ大きく減少するため、寄生容量  $C_p$ に溜まった電荷が瞬間的にオーバーシュート電流  $I_{cp}$  として ReRAM に流れる。本デバイス構造では、 $C_p$  は MOSFET と ReRAM を接続する Al-Si 配線が持つ浮遊

図 2 作製した MOSFET 付 ReRAM の等価 回路

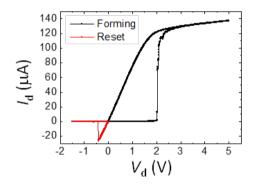

図3 作製された ReRAM の I-V ヒステリシ ス特性

## ② アナログ値の記憶の確認

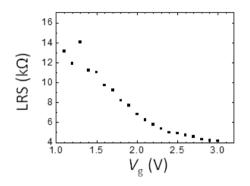

アナログ的動作を確認するため、上記の図 3のような Forming と RESET を行った後、 ゲート電圧 Vgを 1V から 3V に向けてステッ プ的に変えながら I-V Sweep による SET 動 作を行った。Vgの変化に対する SET 時の抵 抗値(LRS)を図4にまとめて示す。ここでは  $V_g$ を変える度に、RESET 動作を行い、 $V_g$ の 値を設定して SET 動作を行っている。図か らわかるように、 $V_g$ の上昇につれて、ほぼ単 調に抵抗値(LRS)が小さくなっていること がわかる。ゲート電圧の増加により、実効的 な制限電流が大きくなり、SET後に形成され るフィラメントも太くなるため、ReRAM の 抵抗値が単調に下がると考えられる。この結 果は、抵抗値を Vg によりアナログ的に変化 させることができることを示している。

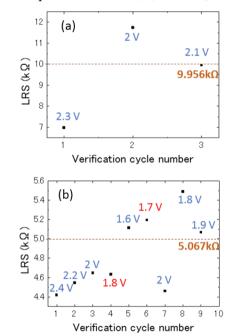

しかし、上記の操作では、 $V_g$ を低い値から高い値に単調に増加させて得られた結果である。実際のアナログ値を得る操作では、必要な値がランダムに決まる。このような操作に対する変化について評価した。図5は、目標の抵抗値を決め、Verify操作によって抵抗

の制御を試みた結果を示したものである。 Verify 操作は、毎回 RESET を行った後、抵抗を下げたい場合は  $V_g$  を大きくし、抵抗を高めたい場合は  $V_g$  を小さくして SET 操作を繰返し、目標値に近づける手法で行った。目標到達の誤差の許容範囲は $\pm 100\Omega$  とした。図 5(a)の例では、3回の操作で目標に到達できているが、(b)の例では 9回の Verify 操作により目標の抵抗値に到達できた。

図4 毎回 RESET 後、Vg を変えながら I-V Sweep による SET 動作後の抵抗値 (LRS)

図5 目標値を(a)10k $\Omega$ 、(a)5k $\Omega$ として、 $V_g$ を変えながら Verify 操作をした際の抵抗値

しかし、上記の(b)の結果からわかるように、時々、抵抗を高めようとして  $V_g$ を小さくしても高くならない場合(図の4回目)、抵抗を低くしようとして  $V_g$ を大きくしても低くならない場合(図の6回目)などがある。この結果は、電流制限による SET を行っても、フィラメントサイズには確率的な揺らぎがあることを示している。詳細な検討の結果、目標値に近づいた後は、本質的に持つ揺らずの効果を用いて、 $V_g$ を変更せずに繰り返し書き込むことで目標値に確率的に近づける手法が良いことがわかった。

(2) 多端子 ReRAM の開拓に向けての動作原理の確認

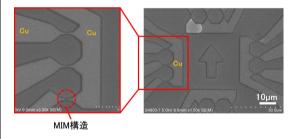

(1)の検討で、ReRAM はアナログ的な抵抗 変化素子として動作することはわかったが、 その動作原理に関してはいまだ不明である。 特に、抵抗制御ゲートを付加して3端子化し、 電界等によりフィラメントサイズを制御す る場合には、フィラメントが形成される原理 を確定し、且つそれが操作できることを示す 必要がある。ここでは、透過型電子顕微鏡 (TEM) 内で、ReRAM を動作させ、その動 作メカニズム(フィラメントの形成メカニズ ム)を評価し、3端子化の可能性を検討した。 これまでも、ReRAM の動作メカニズムを TEM その場観察することで、動作メカニズ ムが解明されつつある。そこでは、FIB加工 などで作成した断面観察サンプルを用いて、 上下に電極を配置して2端子構成でTEM観 察している。この構成では、多端子のデバイ スの評価は難しい。本研究では、平面型で16 端子までの多端子に対応可能な構成の TEM 用サンプルホルダとその評価システムを構 築した。図6は、16端子のTEM内測定用パ ターンの走査型電子顕微鏡 (SEM) 写真であ る。右の像は上下左右に 4 端子ずつの Cu の 引き出し電極が形成されており、4端子のデ バイスが4個搭載されている様子を示してい る。左図は、その1つの拡大像である。ここ では、Cu 電極間にナノギャップが形成され ており、この間に ReRAM 材料を堆積する。

図6 TEM その場観察に用いた電極パターンの電子顕微鏡像

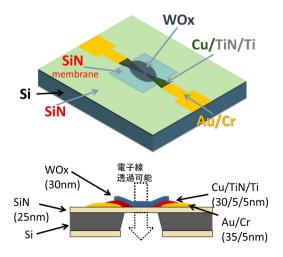

図7 平面型 TEM その場観察用サンプルの 構造(上:鳥瞰図、下:断面図)

図7に WOx を材料として形成した Cu/WOx/Cu の ReRAM 構造の模式図を示す。 図6のパターンの下部は厚さ25nmのSiNメ ンブレンとなっており、TEM で観察可能な 構造となっている。この構造は裏側の 550 μ m 厚の Si 支持基板を KOH 水溶液で選択エ ッチを行うことで、25nmの SiN メンブレン のみを残した構造として実現できる。Cu 電 極で引き出された先は、Si 基板上の 16 個の Au 電極パッドに接続され、上から電気的接 続が取れる構造となっている。図6は、電子 ビーム露光を用いて、12個のナノギャップパ ターンを作製したものであるが、露光パター ンを変更することで自由に 16 端子を使った デバイスを設計し、評価を行うことができる。 この基板の、図1左の下部の赤丸印で示し

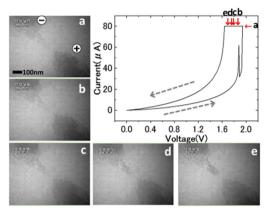

た部分に作製した、Cu/WOx/Cu 構造 ReRAM の電気的特性と、TEM 像を同時に評価した。 電気的特性は SMU を用いて行い、データは パソコン (PC) に取り込まれる。 同時に TEM 像は、CCD カメラで撮影され、同じ PC に取 り込まれる。図8は、その一例である。電圧 を0Vから正方向に約2Vまでスキャンした 後、OV に戻した時の、電圧 - 電流 (I-V) 特 性と、特性中に示す a~e までの各測定点で 観察された TEM 像をビデオ動画から切り出 して示してある。また、ReRAM の抵抗スイ ッチ前後の TEM 像(静止像) は、より解像 度が高いフィルムでも撮影してある。図9に、 初期(左)状態と抵抗スイッチ後(右)の状 熊(ともに電圧は0V印加)のフィルムで撮 影した TEM 像も示してある。図8、9とも に、少し黒っぽい濃いコントラストが、Cu である。

図8の測定では、ReRAM 素子が低抵抗に スイッチした際に、大きな電流が流れて破壊 されないように、80µA の電流制限を設けて いる。図からわかるように、2V付近で、急 激に電流が増大し、同時に抵抗が低下し、電 圧を引き戻しても、同じカーブの上はたどら ないヒステリシス特性を示している。図9左 の初期状態と比べて、図8aの低抵抗化後は、 わずかに、負電極側から Cu が伸びてきてい るように見えるが明確ではない。しかし、b、 c、d、e と時間を経るごとに、負電極から正 電極側に Cu が徐々に伸びて成長していって いる様子が見て取れる。加えて、図9の左右 の TEM 像を比べると分かるように、低抵抗 化後は正極側の Cu 電極が粒状に疎になって いる。これは、正極側の Cu が負極方向に移 動して、負極から正極に向かって成長したこ とを示す。これらの結果は、これまで構築さ れている、Cu 正電極から Cu イオンとして解 け出し、固体電解質(WOx)中を移動して抵 抗スイッチするというモデルと一致し、また、 実用的な ReRAM で用いられる μA オーダの 電流では、初めてこのような途中経過が観測 された結果であると言える。また、電極の正 負を入れ替えた場合には、逆向きの Cu の移

動が起きることも確認している。

図8 TEM その場観察で得られた電気的特性 (抵抗のヒステリシス特性:右上)と図中 の a~e に対応する特性位置での TEM 像

図9 図8の測定前(左)、後(右)の TEM 像

以上の結果は、Cu イオンを電界によって 移動させ、正電極側から析出させることを証 明した最初の結果として、意味があると同時 に、このメカニズムを使うと、多端子化され たデバイス構成を取ることで、電極の接続関 係を変更することができることが容易に想 像できる。すなわち、もう一つの電極を設け ることで、そちらに負電圧(あるいは正電圧) を印加することで、Cu の析出を誘導でき、 最初に形成した2端子間の接続関係をもう一 つの電極で操作することができることにな る。まだ検討できていないが、図6に示した 16 端子の電極パターンでは、容易にその変更 が可能であり、所望の構造の多端子機能性素 子が作製できる。本研究を立案した際に提案 した絶縁性のゲート電極による3端子デバイ スとは少し異なるが、実効的に同等の効果が ある。今後の検討として、絶縁性ゲートを配 置することで、最初に提案した、絶縁ゲート による抵抗スイッチ素子の可能性も出てく ると考えている。

# (3) 萌芽的先端研究としての新たな発見

本研究の大きな特徴は、抵抗変化メモリの 多端子化と新たな機能付加に向けて、その原理も含めて新たなデバイス構造を構築する ことにある。今回の検討では、電流の大さい で抵抗値を決めるフィラメントサイズが決定できることを示すとともに、そのフィラメントの基になる金属を電界で引き出せることを実験的に確認できたことが大きな成果である。これまでも、微小な電流で金属が動く例などは報告されているが、抵抗変化動作 とともに、電子デバイスとして使える電流領域で観察に成功したのは、世界的で初めてである。

## (4) まとめ

以上の結果は、揺らぎに強い人間の脳のような冗長性の高い計算システムを構築するニューラルネットワークに対応可能な新機能素子実現の可能性を示したものであり、さらなる機能性と省電力性を有する人工知能の進展が期待できることを示したものとして価値が高い。

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

[雑誌論文](計10件:内査読有9件)

- (1) M. Kudo, M. Arita, Y. Ohno, and Y. Takahashi: Filament formation and erasure in molybdenum oxide during resistive switching cycles, *Applied Physics Letters*, **105**, 173504-1-4 (2014). Doi: 10.1063/1.4898773

- (2) T. Uchida, M. Arita, A. Fujiwara, and Y. <u>Takahashi</u>: Coupling capacitance between double quantum dots tunable by number of electrons in Si quantum dots, Journal of Applied Physics, **117**, 084316-1-6 (2015). Doi: 10.1063/1.4913393

- (3) <u>Y. Takahashi</u>, M. Kudo, and <u>M. Arita</u>: Visualization of conductive filament of ReRAM during resistive switching by in-situ TEM, *ECS Transactions*, Vol. **69**, No. 10, 299-309. Doi: 10.1149/06910.0299ecst

- (4) T. Uchida, M. Jo, A. Tsurumaki-Fukuchi, M. Arita, A. Fujiwara, and Y. Takahashi: Evaluation of a triple quantum dot series device fabricated by thermal oxidation of Silicon nanowire, *AIP Advances*, **5**, 117144-1-9 (2015). Doi: 10.1063/1.4936563

- (5) M. Arita, A. Takahashi, Y. Ohno, A. Nakane, A. Tsurumaki-Fukuchi, and <u>Y. Takahashi</u>: Switching operation and degradation of resistive random access memory composed of tungsten oxide and copper investigated using in-situ TEM, *Scientific Reports*, **5**, 17103-1-9 (2015). Doi: 10.1038/srep17103

- (6) M. Jo, T. Uchida, A. Tsurumaki-Fukuchi, M. Arita, A. Fujiwara, Y. Ono, K. Nishiguchi, H. Inokawa, and Y. Takahashi: Fabrication and single-electron-transfer operation of a triple-dot single-electron transistor, *Journal of Applied Physics*, 118, 214305-1-6 (2015). Doi: 10.1063/1.4936790

- (7) M. Arita, Y. Ohno, and <u>Y. Takahashi</u>: Switching of Cu/MoOx/TiN CBRAM occurred at MoOx-TiN interface, *Physica Status Solidi A*, **213**, (2), 306–310 (2016). Doi: 10.1002/pssa.201532414

- (8) T. Tohara, H. Liang, H. Tanaka, M. Igarashi, S. Samukawa, K. endo, <u>Y. Takahashi</u>, and <u>T. Morie</u>: Silicon nanodisk array with a fin field-effect transistor for time-domain weighted sum calculation toward massively parallel spiking neural networks, *Applied Physics Express*, **9**, 034201-1-4 (2016). Doi: 10.7567/APEX.9.034201

- (9) H. W. Kye, B. N. Song, S. E. Lee, J. S. Kim, S.J. Shin, J.-B. Choi, Y.S. Yu, and <u>Y. Takahashi</u>: One Electron-Controlled Multiple-valued Dynamic Random-Access- Memory, *AIP Advances*, **6**, 025320-1-5 (2016). Doi: 10.1063/1.4942901

## 〔学会発表〕(計71件)

(1) <u>Y. Takahashi</u>, M. Kudo, and <u>M. Arita</u> (invited): Visualization of Conductive Filament of ReRAM during Resistive Switching by in-situ TEM, 224th Electrochemical Society Meeting (ECS), G04-1107 (2015.10.11-16, October 14, Oral 発表@ The Phoenix Convention Center, Arizona, USA).

#### [図書] (計 1件)

(1) M. Arita, K. Hamada, Y. Takahashi, K. Sueoka and T. Shibayama, "In-situ Transmission Electron Microscopy for Electronics", in "The Transmission Electron Microscope (358 pages)", Edited by Khan Maaz, pp.35-68, (ISBN 978-953-51-2150-3, InTech open access book, September 02, 2015). 358 pages, Publisher: InTech.

〔産業財産権〕(計 0件)

[その他]

ホームページ等

http://www.ist.hokudai.ac.jp/labo/nano-mat

- 6. 研究組織

- (1)研究代表者

高橋 庸夫 (TAKAHASHI YASUO)

北海道大学 大学院情報科学研究科・教授 研究者番号:90374610

(2)研究分担者

有田 正志 (ARITA MASASHI)

北海道大学大学院情報科学研究科・准教授 研究者番号:20222755

森江 隆 (MORIE TAKASHI)

九州工業大学·生命体工学研究科 教授研究者番号:20294530