# 科学研究費助成事業 研究成果報告書

平成 30 年 6 月 14 日現在

機関番号: 82108

研究種目: 基盤研究(B)(一般)

研究期間: 2015~2017

課題番号: 15H03568

研究課題名(和文)酸化膜アンチドープ制御機構解明と新元素構成トランジスタのマテリアルデザイン

研究課題名(英文) Material design for oxide thin film transistor controlled by anti-doping scheme

#### 研究代表者

塚越 一仁(TSUKAGOSHI, KAZUHITO)

国立研究開発法人物質・材料研究機構・国際ナノアーキテクトニクス研究拠点・MANA主任研究者

研究者番号:50322665

交付決定額(研究期間全体):(直接経費) 12,800,000円

研究成果の概要(和文):アモルファス酸化インジウム薄膜を伝導チャネルとした薄膜トランジスタにおいて、特性の不安定性を抑制するための添加元素がホスト材料に及ぼす効果を調べた。アモルファス酸化インジウム薄膜の構造の安定性は、アモルファス中の酸素欠損の密度に依存する。伝導の安定性は、伝導電子を供給する酸素欠損の密度に反比例する。この安定化のためにSiを添加した。原子半径の小さいSiの添加は、ホスト酸化インジウムを歪ませて、伝導電子の5s軌道の重なり確率を高めていることがわかった。これらの知見を基にして、Si添加の少ない構造不安定な高導電層と高密度でSiを添加した低導電性層を積層して、特性を補う構造の形成に成功した。

研究成果の概要(英文): In thin film transistors with amorphous indium oxide thin films as conduction channels, the effect of additive elements to suppress instability of transistor characteristics was investigated. The stability of the atomic-scale structure of the amorphous oxide thin film depends greatly on the density of oxygen vacancies. In addition, the stability of conduction is inversely proportional to the density of oxygen vacancies supplying conduction electrons. Si was added for this stabilization. It was found that additive Si with small atomic radius distorts indium host oxide and enhances the overlap of conduction electron 5 s orbit. Based on these findings, we succeeded in forming a structure with double layer composed of unstable high conductivity layer with small density Si additive and a low conductivity layer with high density Si. This new structure successfully behaves as high performance TFT.

研究分野: 薄膜エレクトロニクス

キーワード: 半導体物性 先端機能デバイス 表面・界面物性 酸化膜半導体 酸素欠損 ドーピング

#### 1. 研究開始当初の背景

IoT (Internet of Things) や AI (人工知能)による生活の電子化は、便利さや安全性を向上させる反面、半導体での電力消費を急増させている。データセンタの消費電力量は最近10年で約10倍に増大し、国内では総電力使用量の1%になる。身近なところでは、近年のディプレイ高精細化に伴い、消費電力が急増している。これらの機器を制御する半導体は、微細化や構造の工夫で省エネ化が試みられているが、さらなる新化には、薄膜半導体の新材料が必要である。

一般に、アモルファス酸化膜半導体は、高移 動度と引き換えに、特性不安定性が生じる (酸化膜半導体のトレード・オフ課題)。この 不安定性は、熱によるアモルファスの構造変 化や酸素欠陥不安定化による。酸化膜半導体 は、酸素欠陥から電子が供給され電気導電が 生じるが、従来の低温成膜での多種金属元素 混合酸化膜では、不安定性要因の抑制と高移 動度の両立できない本質的な物性である。こ れに対して、我々は単純酸化膜 InOx(内在高 移動度材料) に着目し、酸素欠損 Vo の不安 定性の要因を調べ、金属元素と酸素を結合す る結合乖離エネルギーに着目して、スパッタ 成膜での酸素欠損の不安定要因を見出した。 本来 Vo 安定性が低いアモルファス酸化イン ジウム薄膜に、酸素結合乖離エネルギーの高 い元素を添加してエネルギー順位の低い Vo を低減し、Vo の過剰発生を抑制することに成 功していた。

## 2. 研究の目的

本研究では、アモルファル酸化インジウム膜に Si を添加して構造を安定化させる際に、添加 Si が導電性を決める物性を解明することを目的として、薄膜形成と薄膜トランジスタ構造の工夫の検討を行った。

### 3. 研究の方法

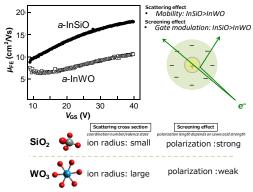

アモルファス酸化インジウム膜中での添加物特性解明のために、結合解離エネルギーの高い Si 元素と W 元素をホスト In に対して添加元素比を等しくした膜(In 元素に対する添加密度~0.11)を類似条件で形成し、トランジスタ構造に加工して、導電特性を比較した(図 1)。

### 4. 研究成果

Si 添加と W 添加共に、薄膜トランジスタとして高い特性を示す。トランジスタ形成時の違いは、スパッタ成膜後の熱アニールにおいて、W 添加 (アニール温度=150  $^{\circ}$ C)が Si 添加 (250  $^{\circ}$ C)よりも低温でトランジスタ特性が安定化する。これは、酸化インジウム、酸化ケイ素、酸化タングステンのそれぞれのギブスエネルギー(Gf)によって、解釈できる。それぞれの 150  $^{\circ}$ Cでのギブスエネルギーは、 $In_2O_3=-524$  kJ/mol,Si $O_2=-831$  kJ/mol,W $O_3=-508$  kJ/mol であることから、In と W は

図1. Si 元素とW元素をホストIn に対して添加元素 比を等しくした InOx 酸化膜半導体の比較。

150℃で共に酸化し安定化することが推測できる。一方で、Siの酸化には更に熱エネルギーが必要であることが示唆されている。

Si添加とW添加のアモルファス膜トランジスタの電界効果移動度をゲート電圧依存性として比較した(図 2)。ゲート電圧をプラス印加では、n型導電性キャリアの密度が増大し、明瞭な2つの差が観られた:Si添加は、W添加よりも移動度が高く、ゲート電圧印加の際の移動度上昇が大きい。Si添加の移動度が、W添加に対して高くなるのは、SiとWの原子サイズで理解できる。Si原子はW原子よりもサイズが小さいために、酸化インジウム膜中で、導電キャリアに対して散乱断面積が小さくなる。これによって導電性が優位になる。

図 2. Si 元素とW 元素による導電性の差。

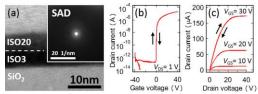

図3 InOx 酸化膜半導体への異なる密度での Si添加で二層構造を試作し、トランジスタ特性を評価。

また、電荷密度の変化は、ルイス酸強度の差で理解できる。ルイス酸強度が高いSiでは、周囲の電荷を元素中心に強く束縛するために、偏極部位が実効的に小さくなる。これによって、周囲の導電電荷の移動への散乱が低下し、添加による移動度低下が比較的小さくなる。

これらの添加元素 Si の特性に加えて、原子 半径の小さいSi がホストInOxを歪ませる効 果が有ることも、精密な XRD 計測で判った。 アモルファスで準備した Si 添加膜を加熱ア ニールして結晶膜として計測した。Si 添加す ることで格子定数が 0.4 %縮小することが 観測された。Si 添加した膜を結晶化すると、 本来であれば In<sub>2</sub>O<sub>3</sub> 化してバンドギャップが 拡がり、結晶粒界効果と相まって、導電性が 低下する筈であるが、実際には導電性が高ま る。これは、Si添加によるホスト InOx の歪 みに依って、導電性を担う5 s 軌道の重なり 確率が高まって導電性を向上させていると 考えられる (今後、精密評価を計画中)。こ の結果から、ホストアモルファスの構造と導 電性の安定化に不可欠な異種元素の添加に 関して、添加元素による導電性の低下を最小 限とすることができる。

しかしながら、熱による構造の安定性をえる ための Si 添加は、確実に薄膜の移動度低下 を及ぼす。このため、可能な限り添加量を少 なくして、ホストの導電性を引き出す必要が ある。このために Si 添加を調整した二層積 層構造を提案し、評価した(図 3)。

導電性の高い下層には 3 wt%添加 InOx(単層での移動度~23 cm²/Vs: ISO3)を用いて、導電性の低い上層には 20 wt%添加(単層での移

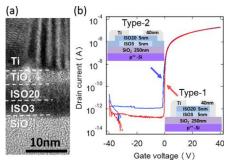

図 4 二層 InSiO 薄膜トランジスタの端子構造の違いによるトランジスタ特性。

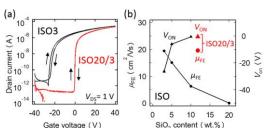

図 5. 二層 InSiO と単層膜との特性比較。

動度 < 0.1 cm<sup>2</sup>/Vs: ISO20) として、それぞれ 5nm をスパッタで連続成膜した。上層は、ほ ぼ絶縁膜である。TEM 観察で、明瞭な二層構 造が観測された。また、二層膜の上から、上 層のエッチグをすることなく Ti 電極を形成 するだけで、オーミック接続が可能であり、 トランジスタ特性が計測できた。薄膜と Ti 端子との接触を調べた(図4)。導電性を担う ISO3 層は同型にパターンニングして、電極を 形成した際に ISO3 に全く接しない様に基板 と ISO 全体を覆う ISO20 構造と、ISO3 に横か ら接する構造の2種を比較した。興味深いの は、いずれの構造でも薄膜に電気的接触があ り、移動度はほぼ同等であることである。違 いは、基板全体に ISO20 が覆う場合は、ISO20 が微小な導電性ながらも導電性野有る膜で あることから、リーク電流が1桁程度大きく なることだけであった。

積層 ISO20/3 の接触抵抗を、ISO 単層膜との比較(図5)で、考察する。積層 ISO20/3 は、2 層が均等である場合の ISO11 よりも移動度が高く、導電層の移動度向上には効果がででいる。当初懸念であった導電性の低い上層 ISO20 が導電性 ISO3 へのアクセス抵抗を大幅に高めて二層膜トランジスタとしての特性を低下させる効果は、問題となっていない。これは、低導電性の ISO20 膜厚が 5nm と薄く、上に形成した Ti 電極が InOx 部位から酸素を引き抜いて界面に薄い酸化 Ti 層を形成することで、導電 ISO3 層との接触抵抗を低下させていると推測できる。

また、ISO3トランジスタ特性の閾値電圧 Vth は-23 V 程度であり、ISO20/3 よりも大きく 負にシフトしていることから過剰に酸素欠 損があるが、ISO20/3 では ISO20 で覆うことで酸素抜けが抑制できていて、キャッピング 効果が生じている。

このキャッピング効果に対して、薄膜の水素 還元特性を調べた(図 6)。水素還元は、薄膜 トランジスタを作製する工程で、水素が発生 する CVD 成膜にて生じてしまう。これによっ て、トランジスタ特性が劣化してしまうこと が問題となっている。特に、閾値 Vth が還化 工程で大きく負にシフトして、その後の酸化 処理でも基に戻らない。これに対して、 ISO20/3 膜では、水素雰囲気加熱で単層 同様に閾値 Vth の負シフトが生じてしまうも のの、その後のオゾンアニールで閾値 Vth は

積層膜 ISO20/3 の還元処理に対する特性 耐性。

0 V に戻ることが確認できた。この結果は、 上層に用いられている ISO20 膜は、水素は透 過してしまうものの、酸素に対して封止性が あるために、酸素欠損の絶対量は変化せずに 保持できると考えられる。

これらの結果から、アモルファス酸化インジ ウム膜への添加物は、アモルファス構造の熱 安定性を高めるためるが、添加元素による伝 導散乱を生じさせてしまうことへの対策が 必要であることがわかった。しかし、移動度 低下は、添加元素を Si とすることで、移動 度低下要因を比較的軽減させることが出来 ていることが判明した。その上で、移動度を 高く保ち、還元特性に対する耐性を作り込む ために、移動度の高い低密度 Si 添加層と構 造安定性の高い高密度 Si 添加層を積層する ことで、移動度と熱安定性の双方を有するト ランジスタ半導体層を造れることが判った。 今後、薄膜の酸素欠陥密度を高度に制御でき る成膜法を開発し、積層へテロ膜での酸化膜 移動度限界の実現を目指した研究を進める。 さらに、Si 添加による格子構造歪みなども、 精密計測にて科学解析を行う予定である。

## 5. 主な発表論文等 〔雑誌論文〕(計7件) [1-7:全て査読あり]

25102/1-6 (2017).

- 1. Correlation between active layer thickness and ambient gas stability in IGZO thin-film X.Gao, M.-F. Lin, B.-H.Mao, M.Shimizu, N.Mitoma, T.Kizu, W.Ouyang, T.Nabatame, Z.Liu, K.Tsukagoshi, S.-D.Wang, Journal of Physics D: Applied Physics 50 (2)

- 2. Amorphous oxide semiconductor In-Si-O fabricated by solution process H. E. Jan, T. Nakamura, T. Koga, T. Ina,

- T.Uruga, T.Kizu, K.Tsukagoshi, T.Nabatame, A.Fujiwara Journal of Electronic Materials 46 (6) 3610-3614 (2017).

- 3. Radial Interference Contrast in in-situ SEM Observation of Metal Oxide Semiconductor Film Crystallization, Kunji Shigeto, Takio Kizu, Kazuhito Tsukagoshi, Toshihide Nabatame, Microscopy and Microanalysis 23 (S1), 1512–1513 (2017).

- 4. Homogeneous double-laver amorphous Si-doped indium oxide thin-film transistors for control of turn-on voltage T.Kizu, S.Aikawa, T. Nabatame, A.Fujiwara, K.Ito, M.Takahashi, K.Tsukagoshi, Journal of Applied Physics 120 (4) 045702/1-4(2016).

- 5. Phase transitions from semiconductive amorphous to conductive polycrystalline in Indium Silicon Oxide thin films N.Mitoma, B.Da, H.Yoshikawa, M.akahashi, K.Ito, T.Nabatame, M.Takahashi, K.Ito, T.Kizu, A.Fujiwara, K. Tsukagoshi Applied Physics Letters 109 (22) 221903/1-5

- 6. Suppression of excess oxygen for environmentally stable amorphous In-Si-O thin-film transistors S.Aikawa, N.Mitoma, T.Kizu, X.Gao, M.-F.Lin, T.Nabatame, K.Tsukagoshi, Applied Physics Letters 106 (19) 1921103/1-5 (2015).

- 7. Codoping of zinc and tungsten for practical high-performance amorphous indium-based oxide thin film T.Kizu, N.Mitoma, M.Miyanaga, H.Awata, T.Nabatame, K.Tsukagoshi, Journal of Applied Physics 118 (12) 125702/1-4 (2015).

# [学会発表](計 10 件)

1. Nanoscale material transport for future electronics

### Kazuhito Tsukagoshi

The 2nd Nippon-Taiwan Workshop on Innovation of Emergent Materials JAIST, Kanazawa, February 28-March 2, 2018.

- 2. Silicon induced Metal Oxide thin film transistor, K. Tsukagoshi, K. Kizu, S.Aikawa, T.Nabatame, The first International Semiconductor Conference for Global Challenges (ISOGC-2017)

- Nanjing, China, July 16-19, 2017. 3. 結晶化した InSiO 薄膜の反射電子像コントラ

重藤訓志、木津たきお、<u>塚越一仁</u>、 生田目俊秀

電子顕微鏡学会第72回学術講演会

- 東北大学, 2017 年 6 月 14-16 日. 4. 急峻なサブスレッショルドスロープを持つ ALD-AlOx ゲート絶縁膜アモルファス InSiO 相川慎也,木津たきお,生田目俊秀,

- 第78回応用物理学会秋季学術講演会 福岡国際会議場, 2017年9月5-8日. ALDで形成した InOx 高移動度 TFT

- 木津たきお,相川慎也,池田幸弘,上野啓 司,生田目俊秀,<u>塚越一仁</u> 第78回応用物理学会秋季学術講演会

福岡国際会議場, 2017年9月5-8日.

東京工業大学, 2016 年 3 月 19-22 日. 7. Structure and Tolerance to Thermal Stress

of Doped In<sub>2</sub>O<sub>3</sub> Thin-Films, Fujiwara, N. Mitoma, T.Kizu, T.Nabatame, <u>K.Tsukagoshi</u>, Y.Tamenori, K.Kako, T.Ina, T.Uruga, K.Ohara, L.S.R.Limara, C.H.Spmg, O.Sakata, S.Kohara,

The 9th International Conference on the Science and Technology for Advanced Ceramics (STAC-9)

Tsukuba, Japan, October 19-21, 2015.

8. Low-temperature Processable Amorphous In-W-O thin-film transistors

T. Kizu, S. Aikawa, N. Mitoma, M. Shimizu, X.Gao, M-F. Lin, T. Nabatame, K.

Tsukagoshi

The Oth International Conference on the

The 9th International Conference on the Science and Technology for Advanced Ceramics (STAC-9)

Tsukuba, Japan, October 19-21, 2015.

9. 過剰酸素の抑制による真空環境で安定な In-Si-O TFT 相川慎也, 三苫伸彦, 木津たきお, 生田目 俊秀, 塚越一仁,

第76回応用物理学会秋期学術講演会名古屋国際会議場、2015年9月13-16

10.二層 InSiO 構造を用いた薄膜トランジスタ 木津たきお、相川慎也、生田目俊秀、 塚越一仁、 第76回応用物理学会秋期学術講演会、 名古屋国際会議場、2015年9月13-16日.

[図書](計0件)

### 〔産業財産権〕

○出願状況(計1件)

名称:多層構成の薄膜トランジスタ及びその製造方法並びにアクティブマトリクス駆動ディスプレイ

発明者:生田目俊秀, 木津たきお, 塚越一仁

権利者:NIMS 種類:特願

番号: 2015-126796

出願年月日:2015年6月24日

国内外の別:国内 ○取得状況(計0件)

[その他]

ホームページ:/www.nims.go.jp/pi-ele\_g/

# 6. 研究組織

(1)研究代表者

塚越 一仁 (TSUKAGOSHI, Kazuhito)

国立研究開発法人物質・材料研究機構・国際ナノアーキテクトニクス研究拠点・MANA 主任研究者

研究者番号:50322665

(2)研究分担者

なし

(3)連携研究者 なし

### (4)研究協力者

木津 たきお (KIZU, Takio)

国立研究開発法人物質・材料研究機構・国際 ナノアーキテクトニクス研究拠点・ポスドク研究 員