# 平成27年度(基盤研究(S))研究概要(採択時)

## 【基盤研究(S)】

理工系 (工学)

# 研究課題名 オンチップ光配線のための超低消費電力半導体薄膜光 回路の構築

あらい しげひさ 東京工業大学・大学院理工学研究科・教授 **荒井 滋久**

研究課題番号: 15H05763 研究者番号: 30151137

研 究 分 野: 工学、電気電子工学 キーワード: 光デバイス・光回路

## 【研究の背景・目的】

スーパーコンピュータの性能ランキングである TOP500 (www.top500.org)などをみると性能上位に占めるコンピュータの内、ほとんどがラック間、ボード間での光通信技術を取り入れており、シリコンフォトニクス技術を中心としてチップ間通信への光技術の適応も検討されている。さらに、チップ内のコア数の増加、微細化によるトランジスタ数の増加より、この次の段階としてオンチップ光通信が重要になってくると考えられる。

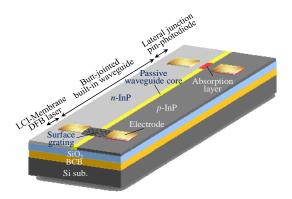

オンチップ光通信においては、10-100 fJ/bit 以下という極低エネルギーコストでの高効率データ伝送、小型化が特に必要である。われわれは半導体活性層およびその周辺のみを薄膜(メンブレン)として残し、上下を誘電体や空気によって挟み込むメンブレン構造により、通常の半導体レーザの約 3 倍の活性層への光閉じ込め効果を利用するメンブレンレーザを提案し、シリコン基板上に世界最小しきい値電流のDFBレーザ、InP 細線導波路、10 Gbps 動作メンブレン光検出器などを形成する要素技術を実現してきた。

本研究では、図 1 に示すように、これらの素子を 集積した半導体薄膜光回路を構築することを目的と している。

図1 半導体薄膜 (メンブレン) 光回路の基本構造

# 【研究の方法】

前述した目的を達成するため 4 年間で主に 4 つの 分類に分け、研究を推進する。

① **要素デバイス探究**:将来的な集積化を念頭に置き、 光源、導波路、光検出器の各要素に要求される特

- 性の明確化とそれを実現するための構造設計および素子実現を行う。

- ② 集積加工技術の確立:特に常温表面活性化技術の 光集積回路への適応可能性を明らかにする。

- ③ シリコン基板上集積:半導体レーザの高効率化と 光検出器特性の改善を合わせ最終的に 10 Gbps 以上で 30 fJ/bit のエネルギーコストの実現を目 指す。

- ④ **CMOS 基板上集積**: CMOS 回路への光集積回路 積層技術、特に電気的接続方法などを確立し、そ の CMOS 基板上光集積回路動作を実証する。

### 【期待される成果と意義】

本研究申請者らは、既に超低電流動作可能な半導体レーザを実証しているが、オンチップ光通信を現実的なものとするためには、送信光源の高効率化および低電力動作可能な光検出器の実現が必須となる。本研究により、低消費電力・小型光伝送構成を実現できれば、オンチップ光配線の現実性が大きく高まり、当該分野の研究開発の活性化が期待され、将来的な高性能 LSI の実現に近づく。また、学術的観点からは、低消費電力伝送を実現するためのレーザおよび光検出器の理想構造について明らかにできる。

## 【当該研究課題と関連の深い論文・著書】

- D. Inoue et al., Appl. Phys. Express, vol. 7, no. 7, pp. 072701-1-4, July 2014.

- S. Matsuo, et al., IEEE J. Sel. Top. Quantum Electron., vol. 19, no. 4, p 4900311, July/Aug. 2013.

- K. Takeda et al., Nature Photonics, vol. 7, no. 7, pp. 569 575, May 2013.

- S. Arai et al., IEEE J. Sel. Top. Quantum Electron., vol. 17, no. 5, pp. 1381-1389, Sep. 2011.

### 【研究期間と研究経費】

平成 27 年度 - 30 年度 153,200 千円

#### 【ホームページ等】

http://www.pe.titech.ac.jp/AraiLab/index.html arai@pe.titech.ac.jp