# 科研費

## 科学研究費助成事業 研究成果報告書

平成 30 年 6 月 7 日現在

機関番号: 10101

研究種目: 基盤研究(C)(一般)

研究期間: 2015~2017

課題番号: 15K04672

研究課題名(和文)高温熱処理アルミナ超薄膜による絶縁体/窒化インジウムアルミニウム界面の制御と応用

研究課題名(英文)Control of insulator/InAIN interface using high-temperature annealed Al203 ultrathin layer and its application

#### 研究代表者

赤澤 正道 (Akazawa, Masamichi)

北海道大学・量子集積エレクトロニクス研究センター・准教授

研究者番号:30212400

交付決定額(研究期間全体):(直接経費) 3,800,000円

研究成果の概要(和文):窒化ガリウム系高電子移動度トランジスタは第5世代の無線通信向けのデバイスとして貢献しうるが、動作電力および周波数を向上させるためにはバリア層材料として窒化インジウムアルミニウム (InAIN)の採用が期待される。しかし、InAINの本質的な特性から漏れ電流が大きく、絶縁体と組み合わせてMOSゲート構造とすることが必須となる。本研究においては、このような背景の中、SiO2とInAINの界面の制御に関する研究を行い、酸化アルミニウム超薄膜層およびプラズマ酸化膜超薄膜層を介在層とすることが有効であることを突き止め、これまでにない良好な特性を有する界面の形成に成功した。

研究成果の概要(英文): GaN-based HEMTs can contribute to the 5G wireless communication system. InAIN which can be used as a barrier material on GaN is attracting much attention to improve the operational power and frequency limit. However, since the leakage current through InAIN is high due to its material properties, a combination with an insulator to form a MOS gate structure is necessary. In this project, a research work was made to control an SiO2/InAIN interface. An insertion of ultrathin AI2O3 or plasma oxide interlayer was found to be efficient, leading to a successful formation of an excellent SiO2/InAIN interface.

研究分野: 半導体デバイスプロセス

キーワード: 窒化インジウムアルミニウム MOS MIS 二酸化シリコン InAIN SiO2

## 1.研究開始当初の背景

(1) 窒化インジウムアルミニウム(InAlN)は、窒化ガリウム(GaN)に格子整合可能な窒化物混晶である。これを用いた InAlN/GaN ヘテロ構造は、高電子移動度トランジスタ(HEMT)においてすでに実用化されている窒化アルミニウムガリウム(AlGaN)によるAlGaN/GaN ヘテロ構造に比べ、電流密度が大きく化学的・熱的にもより安定な HEMTを実現できることがKuzmikにより報告された。その報告以降、本国をはじめとし、米国、欧州各国、中国から多くの研究発表がなされた。

(2) InAlN をバリア層とする HEMT の試作に ついて、多くの発表がなされたが、従来の HEMT 構造ではゲートの微細化が進行して も遮断周波数の記録が 200GHz 台に留まり、 伸び悩んでいた 。一方、これらの報告よ りも先に、HEMT の性能向上の妨げとなる要 因として、ゲートリーク電流が課題であるこ とが報告され、金属 - 絶縁体 - 半導体(MOS) 構造とすることが提案されていた 。この方 針に従った素子開発が行われ始めると、作製 された MOS ゲート HEMT(MOSHEMT)は、 遮断周波数の記録を次々に塗り替え 400GHz に至った 。しかし、絶縁体と InAlN との界面の性質を最良のものとするための 制御方法についてはよく調べられていない 状況であった。なお、本研究開始後、自立 GaN 基板上の良質な InAlN 結晶においても ゲートリーク電流は大きく、InAlN 自身の特 徴である大きな自発分極が主要な要因であ ることが報告されており 、その防止策とし て MOS ゲート構造を構成することが必須で あることが分かってきた。

(3) 5G 世代の無線通信においては大電力の通信用デバイスが求められる。 GaN 系 HEMT はその要求に応えうるデバイスとして貢献しうるが、動作周波数を向上させるためにはバリア層材料として InAlN の採用が期待される。

## 2.研究の目的

本研究の目的は、絶縁膜と InAIN との間に 良好な界面を形成する手段を確立し、高密 度・高移動度の 2 次元電子ガスを生成する InAIN/GaN ヘテロ構造と組み合わせ、デバイ ス集積化に有利な金属 - 酸化物 - 半導体ゲ ート型高電子移動度電界効果トランジスタ (MOSHEMT)の基本構造を試作・評価してそ の有効性を実証することにある。

#### 3.研究の方法

本研究においては、電子デバイス製造において実用化されている絶縁膜の中で最も禁制帯幅の大きい $SiO_2$ とInAINの界面の制御を試みた。当初、原子層堆積法(ALD)による、

Al<sub>2</sub>O<sub>3</sub> 超薄膜を界面制御層として挿入する計画であったが、研究が進むにつれ、より有効な界面の制御方法としてプラズマ酸化膜超薄膜層を挿入する方法を見出し、大幅な界面準位低減に成功したのでこれについてさらに詳しく検討し、MOS 構造の作製と評価、さらには MOSHEMT ゲート構造の作製と評価を行った。

具体的な手順としては、(1) 界面形成プロセス各段階(自然酸化膜除去、ALD Al<sub>2</sub>O<sub>3</sub>超薄膜堆積あるいは N2O プラズマ酸化処理による介在層形成、介在層上への SiO<sub>2</sub> 超薄膜堆積)での X 線光電子分光法(XPS)による分析を行い、(2) 厚い絶縁膜及び金属電極を形成して MOS 構造を完成し、その容量-電圧(C-V)特性から界面準位密度分布を評価し、(3)種々の界面形成条件について比較を行った。さらに、(4) 最適化された界面形成プロセスを MOSHEMT ゲート構造に応用しその効果を確認した。

## 4.研究成果

(1) InAIN 上にプラズマ CVD により  $SiO_2$  を直接成膜した場合には、絶縁体 - 半導体界面において制御されていない酸化が進行することが XPS により判明した。完成した MOS 構造において界面準位密度は、測定可能な範囲内では最低でも  $10^{12}$   $cm^2 eV^{-1}$  台と、高い値となった。

(2) この結果をもとに、界面形成時に引き起こされる、制御されていない酸化を抑制するべく、 $Al_2O_3$  超薄膜を介在層として挿入することを検討した。2 nm 程度の  $Al_2O_3$  超薄膜を挿入したところ、若干の界面準位の低減(測定可能な範囲内で最低でも  $10^{12}$  cm $^2$ eV $^{-1}$ 台)が見られた。さらに、2 nm 程度の  $Al_2O_3$  超薄膜を高温熱処理(850)してから  $SiO_2$  を堆積することにより界面の制御を試みたが、高温熱処理の効果は見られず、熱処理を行っていない  $Al_2O_3$  超薄膜を挿入した試料とほぼ同じ界面準位密度分布が得られた。

(3) 種々の膜厚 (1 nm, 0.5 nm, 0.25 nm) の  $Al_2O_3$  超薄膜を介在層として挿入した MOS 構造に対し界面準位を評価したところ、1 nm よりも薄い場合に界面準位が大幅に低減(伝導帯下 0.3 eV で  $10^{11} \text{ cm}^2 \text{eV}^{-1}$ 台)することが分かった。XPS による分析により、0.5 nm の  $Al_2O_3$  超薄膜を挿入した場合、InAIN 最表面が酸化されることが分かった。このような酸化が、整然と進行し界面での乱れが低減されたため、界面準位の低減につながったものと考えられる。この結果から、InAIN 表面をプラズマ酸化することにより介在層を形成し、その上に絶縁膜を挿入することで、界面準位が低減できないかという着想に至った。

(4) N<sub>2</sub>O プラズマによる InAlN 表面の酸化によりプラズマ酸化膜超薄膜層を形成し、これ

を介在層として界面を形成する方法を試み た。プラズマ出力を 30W に固定し、処理時間 (酸化時間)を0.5分、1分、3分と変えてプ ラズマ酸化膜超薄膜層を形成し、試料表面の XPS 分析を行ったところ、1 分程度までは酸 化膜厚が単調に増加するものの、3 分行った 試料では膜厚増加が飽和傾向にあり、しかも 表面のストイキオメトリーが著しく乱され たことが分かった。MOS 構造完成後、各試料 の界面準位密度分布を評価した結果、1分の 処理を行った試料において界面準位が大幅 に低減(伝導帯下 0.3 eV で 10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup>台) することが分かった。すなわち、界面準位を 低減するには、プラズマ処理時間に最適値が 存在することがわかった。また、その低減の 度合いは、1 nm よりも薄い ALD Al<sub>2</sub>O<sub>3</sub> 超薄膜 層を介在層として挿入した試料と同程度で あり、表面酸化の進行が制御された形で整然 と行われた場合には界面準位が低減するこ とが判明した。

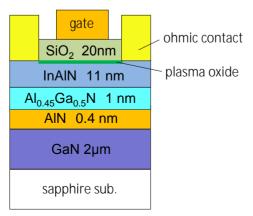

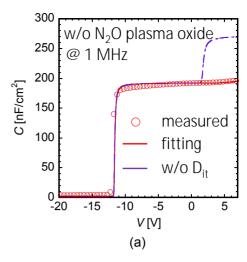

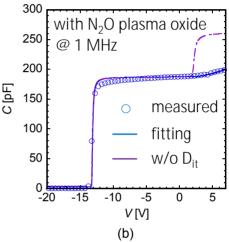

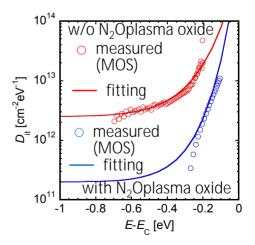

(5) 最適化されたプラズマ酸化膜挿入プロセ スを、MOSHEMT ゲート構造に応用し、界面 準位の低減を確認した。実際に作製された構 造を図1に示す。この構造において、合金散 乱を抑制するためのスペーサ層として、 InAIN 層の結晶品質を向上するとして報告さ れている AlGaN/AIN スペーサ層を用いてい る。C-V 特性とそのフィッティング結果を 図2に示す。図3のような界面準位密度分布 を仮定したシミュレーションにより、特性が よくフィッティングできることがわかった。 得られた界面準位密度は、MOS 構造において 得られた界面準位密度分布と良好な一致を 示した。これらにより、最適化されたプラズ マ酸化膜介在層挿入プロセスは、実際の MOSHEMT のゲート構造においても界面準 位低減に有用であることが判明した。しかし、 最適の界面制御法をもってしても、伝導帯の 近傍では未だ界面準位密度が高いため、これ が影響し、C-V 特性は理想とは大きく違っ たものとなった。理想に近い C-V 特性を実 現するには、数値例として伝導帯から 0.2eV の位置において界面準位をさらに1桁下げな くてはならない。これは残された課題である。

図 1 MOSHEMT ゲート構造。

図 2 MOSHEMT ゲート構造の C-V 特性。 (a)  $SiO_2$ を InAIN 上に直接堆積した場合。 (b) プラズマ酸化膜介在層を有する場合。

図3 MOSHEMT ゲート構造 C-V 特性のフィッテングにより得られた界面準位密度分布。MOS ダイオードにおいて得られた結果を白抜きの円で比較して示した。

#### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## 〔雑誌論文〕(計 2件)

$\underline{M.~Akazawa}$ , and A. Seino; "Reduction of interface state density at SiO<sub>2</sub>/InAlN interface by inserting ultrathin Al<sub>2</sub>O<sub>3</sub> and plasma oxide interlayers," Phys. Status Solidi B, Vol. 254, No. 8, pp. 1600691-1 - 6 (2017). [査読有]

M. Matys, B. Adamowicz, A. Domanowska, A. Michalewicz, R. Stoklas, M. Akazawa, Z. Yatabe, and T. Hashizume; "On the origin of interface states at oxide/III-nitride heterojunction interfaces," J. Appl. Phys., Vol. 120, No. 22, 225305-1 - 12 (2016). [查読有]

## [学会発表](計11件)

北嶋翔平,赤澤正道;「プラズマ酸化膜介在層を有するSiO<sub>2</sub>/InAlN界面の特性」 2018年 < 第65回 > 応用物理学会春季学術 講演会,東京,早稲田大学 (2018).

北嶋翔平 , 赤澤正道; 「 $Al_2O_3$ およびプラズマ酸化物超薄膜介在層を有する $SiO_2$ /InAlN界面の特性」第53回応用物理学会北海道支部/第14回日本光学会北海道支部合同学術講演会, 札幌, 北海道大学 (2018).

北嶋翔平,赤澤正道;「Al<sub>2</sub>O<sub>3</sub>超薄膜介在層を有するSiO<sub>2</sub>/InAlN界面の特性」2017年 <第78回>応用物理学会秋季学術講演会, 福岡,福岡国際会議場 (2017).

清野 惇、<u>赤澤 正道</u>:「Al<sub>2</sub>O<sub>3</sub>超薄膜層を 挿入したSiO<sub>2</sub>/InAlN界面の特性—Al<sub>2</sub>O<sub>3</sub> 膜厚依存性—」2017年 < 第64回 > 応用物理 学会春季学術講演会,横浜市,パシフィ コ横浜 (2016).

M. Akazawa, A. Seino, N. Yokota and T. Hasezaki; "Reduction of Interface State Density at SiO<sub>2</sub>/InAlN Interface by Inserting Ultrathin Interlayers," Abstract Book of the International Workshop on Nitride Semiconductors 2016 (IWN2016, Hilton Orlando Lake Buena Vista, Orlando, Florida, USA, October 2 · 7, 2016), p.194.

清野 惇、横田 直茂、<u>赤澤 正道</u>:「プラズマ酸化層を挿入したSiO<sub>2</sub>/InAIN界面の特性」2016年 < 第77回 > 応用物理学会秋

季学術講演会,新潟市,朱鷺メッセ(2016).

清野 惇 , 長谷崎 泰斗 , 横田 直茂 , <u>赤澤</u> <u>正道</u>:「プラズマCVD  $SiO_2$ /InAlN界面への  $Al_2O_3$ 超薄膜層挿入の効果」2016年 < 第63回 > 応用物理学会春季学術講演会 , 東京 , 東京工業大学大岡山キャンパス(2016).

M. Akazawa; "Characterization of Surfaces and Interfaces of InAlN (invited)," 2016 RCIQE International Seminar (Hokkaido University, Sapporo, Japan, March 8, 2016).

M. Matys, B. Adamowicz, R. Stoklas, <u>M. Akazawa</u>, Z. Yatabe, and T. Hashizume; "Nature and origin of interface states at dielectric/III-N heterojunction interfaces," 2015 MRS Fall Meeting & Exhibit (Boston, Nov. 29 – Dec. 4, 2015).

清野 惇,赤澤 正道:「プラズマCVDにより形成されたSiO<sub>2</sub>/InAIN界面の評価」2015年 < 第76回 > 応用物理学会秋季学術講演会,名古屋市,名古屋国際会議場(2015).

M. Akazawa and T. Hashizume; "Characterization of Surfaces and Interfaces of InAlN/GaN Heterostructures (invited)," 11th International Conference on Nitride Semiconductors (ICNS-11, Beijing, China, Aug.30-Sept. 3, 2015).

[図書](計 0件)

[産業財産権]

出願状況(計 0件)

取得状況(計 0件)

〔その他〕 なし

6.研究組織

(1)研究代表者

赤澤正道(AKAZAWA, Masamichi)

北海道大学・量子集積エレクトロニクス研

究センター・准教授 研究者番号:30212400