# 科研費

# 科学研究費助成事業 研究成果報告書

平成 30 年 6 月 21 日現在

機関番号: 17104

研究種目: 基盤研究(C)(一般)

研究期間: 2015~2017

課題番号: 15K06021

研究課題名(和文)ビッグデータの高速検索処理を可能にする超低消費電力レシオレスCAMの研究

研究課題名(英文)Study on fully digital ternary content addressable memory for high-speed processing of the big data.

#### 研究代表者

中村 和之(NAKAMURA, KAZUYUKI)

九州工業大学・マイクロ化総合技術センター・教授

研究者番号:60336097

交付決定額(研究期間全体):(直接経費) 3,500,000円

研究成果の概要(和文):超低電圧下での動作を可能としたレシオレスSRAM技術により、素子ばらつきや経年劣化の影響を受けずに、高速かつ超低消費電力な、T-CAM (Ternary Content Addressable Memory)を開発した。24トランジスタ構成のT-CAMセルと、階層型AND構成のマッチング回路を開発した。180nmCMOSプロセスでT-CAM回路の実証チップを試作し、同時に試作した6トランジスタSRAM型のT-CAMとの性能比較を行った。その結果、電源電圧0.25Vまでの動作を実測で確認し、従来の6トランジスタSRAMを用いたT-CAMに対して、半分以下の電源電圧で動作することを実測で確認した。

研究成果の概要(英文): A fully digital ternary content addressable memory (TCAM) using the ratioless static random access memory (RL-SRAM) technology and fully complementary hierarchical-AND matching comparators (HAMCs) was developed. Since its fully complementary and digital operation enables the effect of device variabilities to be avoided, it can operate with a quite low supply voltage. A test chip incorporating a conventional TCAM and a proposed 24-transistor ratioless TCAM (RL-TCAM) cells and HAMCs was developed using a 0.18um CMOS process. The minimum operating voltage of 0.25V of the developed RL-TCAM is less than half of that of the conventional TCAM.

研究分野: 工学

キーワード: TCAM SRAM 素子劣化 レシオレス ばらつき 動作マージン 低電圧 連想メモリ

### 1.研究開始当初の背景

映像配信や電話網を含め全ての情報が IP パケットにより、インターネット網を通して 行われるようになってきた。その中核をなす インターネットルータ(IP ルータ)における パケット処理には、リアルタイム性が最重要 であるため、検索専用ハードウエアエンジン である CAM ( Content Addressable Memory)が利用されている[1]。CAM は、 連想メモリとも言われ、データを与えて、そ れと一致する(あるいは部分一致する)アド レスを出力するという特殊な機能を持つ。特 に、記憶単位を2ビット化し、0値1値に加 えて、ドントケアの計3値の格納が可能で、 部分一致検索が可能な T-CAM (3値 CAM: Ternary-CAM)が、IP ルータのパケット処 理には用いられる。さらに今後、T-CAMは、 コンピュータウィルスや不正アクセス監視、 生命情報(DNA)パターンの照合に加えて、 インターネット上に蓄積される膨大なビッ グデータからの高速な情報抽出エンジンと しての応用が期待されている。T-CAM は、 SRAM(Static Random Access Memory)回路 を基本としている。CAM の基本セルは、 SRAM セルにトラジスタを3つ追加した構 成で、検索線対に照会データを与えることで メモリセル内の情報と照合し、共通マッチ線 (ML)を駆動する。CAM は,検索ワードと メモリ全体を、一度に比較するため、消費電 力が1チップ当たり15-20Wと、一般のメモ リに比べて桁違いに大きく、IP ルータにおけ る検索テーブルの増大やネットワーク速度 の向上に伴う CAM の消費電力の増加は深刻 な問題となっていた。

CAM の低電力化の技術に関しては、CAM の一括同時検索を避け、メモリを部分活性化する手法が主体であり、その他、システムレベルで格納情報圧縮を行いメモリ容量を削減する技術や、不揮発性の特殊な素子を利用して待機時消費電力を削減するもの等が提案されていた[1-4]。一方、回路内の一部を低電圧化(低振幅化)することで、動作時電力を一部削減する回路的技術等が提案されているが、回路全体の低電圧動作化による抜本的な低消費電力化の提案と実証はなされていなかった[5]。

## 2.研究の目的

T-CAM は、超高速な情報検索が可能なハードウエアエンジンであるが、消費電力が非常に大きいという課題がある。本研究では、素子ばらつきの影響を受けず、超低電圧下での動作を可能とした、我々オリジナルのレシオレス SRAM 技術を CAM 回路へ適用する[6]。それにより、素子ばらつきや経年劣化の影響を受けず、高速かつ超低消費電力な新分野向けの新しい検索ハードウエアエンジン:レシオレス CAM を実現する。

#### 3.研究の方法

初年度は、レシオレス CAM のメモリセル構成の候補の抽出と、最適構成の探索を行う。次年度には、メモリセルの T-CAM 化と並行して、プライオリティエンコーダ等のロジックを含む T-CAM 全体回路の低電圧化設計を行う。

提案技術の性能実証のために、VDECを利用した実証 LSI の試作を行う。0.18um プロセスを用い、最終的には、電源電圧 0.2V クラスで動作可能な新規 T-CAM 回路及び、従来構成の T-CAM 回路を同一チップ上に搭載した LSIを開発し、その実測データの比較より、性能実証を行う。

#### 4. 研究成果

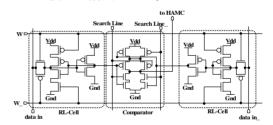

(1)レシオレス SRAM セルを、T-CAM(3値 CAM)セルへ展開する場合の課題と、共通マッチライン回路のレシオレス化に関しての検討を行った。その結果、超低電圧動作が可能なレシオレス T-CAM セルを構成する場合、読み出し回路部分を削減することで24個のトランジスタで構成できることが分かった。図1に得られたレシオレス T-CAM のメモリセルを示す。従来の6トランジスタ SRAM ベースの T-CAM セルでは、16トランジスタが必要のため、オーバーヘッドはセル単体の2倍から1.5倍まで削減できた。

図 1 レシオレス T-CAM メモリセル

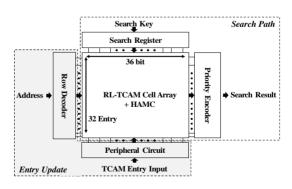

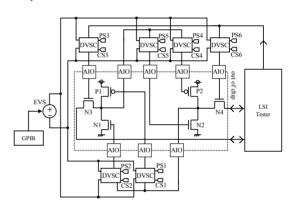

図2試作したT-CAMの全体構成

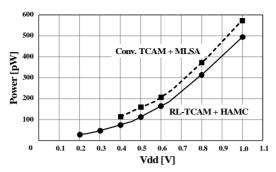

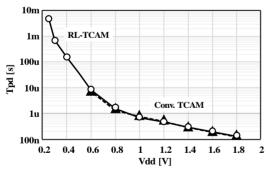

最終年度は、180nmCMOS プロセスで設計・試作したレシオレス T-CAM 回路の実証チップの評価を行い、同時に試作した6トランジスタSRAM 型の T-CAM との性能比較を行った。図2に開発した T-CAM の全体構成を示す。消費電力の消費が大きい共通マッチ線を持たない階層型 AND 構成とした。その結果、図3に示すように、従来方式に対して、15%程度の消

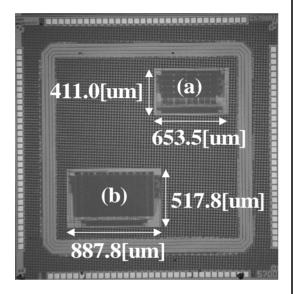

費電力の削減を達成し、かつ半分の電源電圧で動作を可能とした。図4に開発した T-CAMチップの写真を示す。

図3 マッチング回路の性能改善

図4 試作した T-CAM 回路 (a) 従来構成 (b) レシオレス構成

図5 T-CAM 最低動作電圧の測定結果

図5に測定結果を示す。電源電圧0.25Vまでの動作を実測で確認し、従来の6トランジスタ SRAM を用いた T-CAM に対しては、少半分以下の電源電圧で動作することを実測で確認できた。さらには超低電圧領域における測定法に関しても検討を行うことで、典型のなデジタル I/O 回路を用いても 0.2V 程度の領域での測定を可能にした。一方で、超低電源電圧で動作する LSI を電源間に直列に積み重ね、電源電流を有効に利用する技術に関し

ても検討を行った。(詳細については雑誌論文 、学会発表 参照)

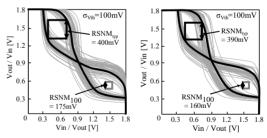

(2) Vth ばらつきに対する動作特性評価 MOSFET のしきい値電圧のばらつきに対す る耐性を実測により直接定量評価するため に、可変 Vth - TEG を利用して、実測により モンテカルロ解析を行う手法を開発した。こ れは従来の方式では、メモリセルを構成する 各トランジスタへ与えるしきい値(Vth)ば らつきの電圧として、+ Vth[V]または-Vth[V]の2種類のみであったものを、新提案 の方式では、任意の値に設定できる。各トラ ンジスタへ与えるしきい値電圧を、制御電圧 源と、リレーを自動的に切り替えることで、 各大容量キャパシタへ順次ストアし、評価を 繰り返すものである。図6に実測によりモン テカルロ解析を行う構成を示す。図7に、実 測結果と回路シミュレーションとの比較を 示す。両社はほぼ一致しており、従来の回路 シミュレーションでしか行うことができな かったモンテカルロ解析を実測で行うこと に成功した(詳細については学会発表

図6 任意 Vth シフト設定構成

(a) SPICE SIM (b) 実測 図7 モンテカルロ解析結果例

## < 引用文献 >

照)

- [1] K.Pagiamtzis, A.Sheikholeslami, "Content-Addressable Memory (CAM) Circuits and Architectures: A Tutorial and Survey", IEEE Journal of Solid-state Circuits, Vol.41, No.3, Mar.2006.

- [2] G.Chen et al., "Yield-Driven Near-Threshold SRAM Design", IEEE Trans.

on VLSI Systems, Vol.18, No.11, Nov.2010. [3] K.Nii et al., "A 28nm 400MHz 4-parallel 1.6Gsearch/s 80Mb ternary CAM", IEEE ISSCC Digest of Tech. Papers, pp240-241, Feb.2014

- [4] S.Matsunaga et al., "A 3.14  $\mu$  m2 4T-2MTJ-Cell Fully Parallel TCAM Based on Nonvolatile Logic-in-Memory Architecture," IEEE Symposium on VLSI Circuits Digest of Tech. Papers, pp. 44-45, Jun.2012.

- [5] I.Hayashi et al., "A 250-MHz 18-Mb Full Ternary CAM With Low-Voltage Matchline Sensing Scheme in 65-nm CMOS", IEEE Journal of Solid-state Circuits, Vol.48, No.11, pp2671-2680, Nov.2013.

- [6] Takahiro Kondo, Hiromasa Yamamoto, Satoko Hoketsu, Hitoshi Imi, Hitoshi Okamura, <u>Kazuyuki Nakamura</u>, "Ratioless full-complementary 12-transistor static random access memory for ultra low supply voltage operation", Japanese Journal of Applied Physics, Vol. 54 No. 4S, pp04DD11-1,04DD11-6, D0I:10.7567/JJAP.54.04DD11, April. 2015

# 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

# [雑誌論文](計 2 件)

D. Nishikata, M. A. Bin Mohd Ali, K. Hosoda, H.Matsumoto, <u>K. Nakamura</u>, "Design and measurement of fully digital ternary content addressable memory using ratioless static random access memory cells and hierarchical-AND matching comparator", Japanese Journal of Applied Physics, Vol. 57 No. 4S, pp04FF11, D0I:10.7567/JJAP.57.04FF11, 查読有, March. 2018

Yusuke Kohara, Naoya Kubo, Tomofumi Nishiyama, Taiki Koizuka, Mohammad Alimudin, Amirul Rahmat, Hitoshi Okamura, Tomoyuki Yamanokuchi, Kazuyuki Nakamura, "Self-stabilization techniques intermediate power level in stacked-Vdd integrated circuits using DC-balanced coding methods", Japanese Journal of Physics, Applied Vol.55 No.4S. pp04EF06-1-7, D0I:10.7567/JJAP.55.04EF06, 查読有, April. 2016

## [学会発表](計 3 件)

D. Nishikata, M. A. Bin Mohd Ali, K. Hosoda, H.Matsumoto, <u>K. Nakamura</u>, "Fully Digital Ternary Content Addressable Memory using Ratio-less SRAM Cells and Hierarchical-AND Matching Comparator for Ultra-low-voltage Operation", Extended

Abstracts of the 2017 International Conference on Solid State Devices and Materials, pp339-340, @Sendai Japan, Sep 22, 2017

S. Yamaguchi, H. Imi, S. Tokumaru, T Kondo, H. Yamamoto, <u>K.</u> <u>Nakamura</u>,"Vth-Shiftable SRAM Cell TEGs for Direct Measurement for the immunity of the Threshold Voltage Variability", IEEE International Conference on Microelectronic Test Structures (ICMTS) 2017, pp.59-61, @Grenoble France, 2017.03.28

Shogo Yamaguchi, Hitoshi Imi, Shogo Tokumaru, K. Nakamura, "Vth-Shiftable SRAM Cell TEGs for Direct Measurement for the immunity of the Threshold Voltage Variability", IEEE/ACM Workshop on Variability Modeling and Characterization, Poster #3, @Austin TX. USA, 2016.11.10

# 〔産業財産権〕

出願状況(計 1 件)

名称:符号変換回路及び並列信号変換送受信

システム

発明者:小原祐輔、久保直也、中村和之

権利者:九州工業大学

種類:特許

番号:特願 2016-53531

出願年月日:平成28年3月17日

国内外の別: 国内

## 〔その他〕

ホームページ等

http://www.design.cms.kyutech.ac.jp/~nakamura

tuma i c

#### 6. 研究組織

(1)研究代表者

中村 和之 (NAKAMURA, Kazuyuki)

九州工業大学・マイクロ化総合技術センタ

ー・教授

研究者番号:60336097