# 科学研究費助成事業 研究成果報告書

平成 29 年 5 月 17 日現在

機関番号: 1 1 3 0 1 研究種目: 若手研究(B) 研究期間: 2015~2016

課題番号: 15K15958

研究課題名(和文)圧縮したまま演算可能なデータ表現に基づくスマートストレージの開発

研究課題名(英文) Developing a Smart Storage based on a Succinct Data Structure that Processes Compressed Data

#### 研究代表者

Waidyasooriya Ha(Waidyasooriya, Hasitha)

東北大学・情報科学研究科・助教

研究者番号:60723533

交付決定額(研究期間全体):(直接経費) 2,900,000円

研究成果の概要(和文):多くの文字列処理ではビッグデータが用いられ,データアクセスが処理のボトルネックになることが多い、本研究ではデータアクセスに着目し,圧縮したまま演算できるような簡潔データ構造とその演算回路構成を提案した.ウェーブレット木を用いた階層的なデータ構造を用いられることにより,データ量が27%まで削減した.その結果メモリアクセスを73%まで削減できた.本研究では,データアクセス削減のための簡潔データ表現に基づいたスマートストレージ構造を提案した.それを用い,遺伝子配列位置推定や文字列検索処理を高速化するアクセラレータを再構成可能な集積回路(FPGA)上で実装し,従来のCPUの21倍の高速処理を実現した.

研究成果の概要(英文): Big-data are used in many text processing applications. As a result, data access often becomes a bottleneck. This research is focused on data access reduction using a succinct data structure and its processor architecture. The data amount is reduced to 27% using wavelet tree based succinct data structure. In addition, memory access is reduced to 73%. A smart storage and its processor architecture is designed based on the proposed succinct data structure to reduce the data access. Using this storage, accelerators are designed for genome data alignment and text data search processes. The designed system that contains accelerators and storage is implemented using an FPGA. A speed-up of over 21 times is achieved compared to the conventional CPU-based implementation.

研究分野: 計算機アーキテクチャ

キーワード: 簡潔データ構造 文字列処理 高速ストレージ ビッグデータ処理

#### 1.研究開始当初の背景

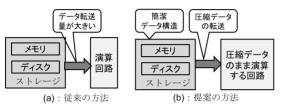

バイオインフォマティクス,データマイニングなどの様々なビッグデータ処理の高図1(a)に示すように,従来ではデータが記憶されているストレージから演算回路までのアク転送量が膨大であり,転送時間が処理のボトルネックとなっている.そこで,SSD(Solid State Drive)やメモリからなはのアクセスを削減することとよりなデータを圧縮して記憶し伸長せずに計算に用いられるようなデータ表現とその演算回路構成について研究を行った。

図1: ビッグデータ処理

#### 2. 研究の目的

本研究では,圧縮したまま演算ができる簡潔データ表現に着目し,演算回路とディスクを一体化したストレージ構造を研究する.研究項目は次の通りである.

- 種々の応用に対して対応可能なハード ウェア向き簡潔データ表現

- データ転送時間に着目した最適構成理 論(演算回路、ディスク上のデータ配置 などの最適化)

#### 3.研究の方法

本研究では主に以下の3点について研究 開発を行った.

- (1) ハードウェア向き簡潔データ表現の開発

- (2) データ転送に着目した ,ストレージを含むハードウェアアーキテクチャについての研究と開発

- (3) ビッグデータへの応用についての研究

## (1) ハードウェア向き簡潔データ表現

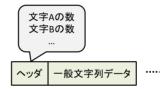

簡潔データ表現とは,データの記憶容量を 削減し,効率よく計算をできるデータの記憶 方法である.効率の良い計算のため,任意の 場所からアクセスし圧縮データのまま計算 できるのは重要である.本研究では図2のよ うなブロックデータ構造を考慮する.ワン プロックのデータは一回のメモリアクセス で読めるようにブロックサイズを設定する. プロックのヘッダには,そのブロックの表現 までの各種の文字の数を記憶する.この表現

により,どのブロックにアクセスしても演算 に必要なデータをすべて取得できる.

この方法では文字の種類が多いと以下のような問題が生じる.

- ヘッダの記憶容量が大きくなる(図3).

- 一つの文字を表すビット数が増える。

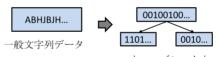

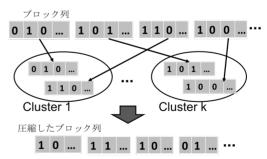

このような問題によりブロックのデータ量が増え、データを読むのに複数回のメモリアクセスが必要になる.この問題を解決するため、ブロック内のデータを圧縮することを考える.圧縮の考え方は以下で示す.

- ウェーブレット木を使い文字の種類を 減らす ヘッダを圧縮(図3).

- ビットペアエンコーディングとクラス タ化 ビット情報を圧縮(図4).

図3で示すように,「ウェーブレット木」を用いて文字列データを階層構造で表すことができる. 各階層では2値の情報を用いることにより, 文字の種類が減りブロックのヘッダサイズが削減される. さらに, ブロックの性質によりクラスタ化を行い, ビットペアエンコーディングにより圧縮する. 図4に示すようにクラスタ内のブロックが似ているので高い圧縮率を達成できる.

文字の種類が多いとヘッダ情報が大きい

ウェーブレット木

図3:ウェーブレット木によりヘッダサイズの削減

図4:クラスター化によりブロックのビット列の圧縮

# (2) <u>データ転送に着目した,ストレージを含むハードウェアアーキテクチャ</u>

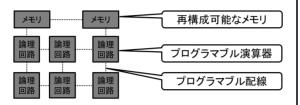

このようなブロック構成を用いて計算するため、ブロックデータを演算に必要な形式に変更する必要がある.そのため演算を高速に行う必要があり並列処理を要求される.さらに、処理応じて必要な演算が異なっているこのような状況に対応するため、本研究では再構成可能な集積回路であるFPGAを用いた.FPGA は図5に示すように、プログラマブル演算回路・配列と再構成可能なメモリを持つ集

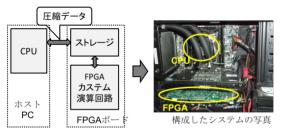

積回路である .FPGA を用いて図6に示すよう な計算システムを構築した.システム構成と それぞれのユニットの役割は以下に示す.

- CPU: オフラインでデータを圧縮し FPGA に転送する.FPGAの制御を行う.

- FPGA: 演算処理やストレージへのアクセ ス・制御を行う.

- ストレージ:圧縮したデータを記憶する. 構成したシステムにはStratix V FPGAとcore i7-960 CPU を用いた、FPGA はハードウェア 記述言語 (HDL) や OpenCL 高位言語により設 計可能である.

図5:再構成可能な集積回 (FPGA)

図6:ビッグデータ処理用の計算システム

### (3) ビッグデータへの応用

#### 遺伝子配列の位置推定処理の高速化

本研究では,遺伝子配列の位置推定処理を 高速に行うためのデータ構造とそのアクセ ラレータ設計について研究を行った.遺伝子 配列 は A , C , G , T の 4 種類の塩基 (文字) で構成されている.位置推定の概要を図7に 示す.参照ゲノム配列というすでに塩基の位

## TCGGCAATAGGCAATCTG

... T C G C C A A T A G G C A A T C T G ...

図7:遺伝子配列一推定処理

置が知られているものを用いて未知の遺伝 子配列を推定する、そのため、位置を測定し たいものから塩基列がわかる小さい断片(シ ョートリード)を利用する.このようなショ ートリードを遺伝子シーケンサーという機 械から作成できる.同じ生物の遺伝子配列が 似ているという性質を利用し、ショートリー ドを参照ゲノム配列と最も似ている位置に 配置する、大量のショートリードを使えば未 知の遺伝子配列の位置推定が可能になる.

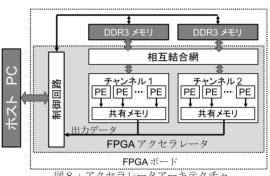

しかしながら,遺伝子配列の塩基数が30 **億以上あり** , 推定するのにその何倍ものシ ョートリードが必要になる.このようなビッ グデータ処理を効率よく行うためには,簡潔 データ構造が用いられる. 本研究では,遺伝 子配列データを簡潔データ構造により圧縮 し, ストレージに保存する.その後,必要 なブロックごとにデータをアクセスし計算 に用いる,このような処理を行うために設計 したアクセラレータの概要を図8に示す.遺 伝子配列データの検索をプロセッシングエ レメント (PE) 内で行い, マッチした位置を ホスト PC に返す. 複数の PE により並列計 算を行うことで高速な処理を実現できてい る.並列計算に必要なデータを圧縮し保存す ることでストレージとのアクセスが削減さ れている.この研究成果を「雑誌論文1]によ り発表した.

図8:アクセラレータアーキテクチャ

## 文字列検索処理の高速化

本研究では,大規模な文字列検索を高速化 するアクセラレータを FPGA 上に設計した. データ量を削減するためウェーブレット木 を用いた簡潔デー表現とその演算回路アー キテクチャを提案し、「学会発表2]により発 表した. 提案アクセラレータを Altera 社の Stratix V FPGA を用い, 100MHz の動作周波 数で実装した.その研究成果を「雑誌論文2, 学会発表1,31により発表した.

### 4. 研究成果

提案の簡潔データ構造を用いる遺伝子配 列の位置推定アクセラレータを FPGA 上に実 装した.アクセラレータは 90MHz の周波数で 動作することを確認できた.CPU を用いて圧 縮したデータは FPGA のストレージに転送さ れ,FPGAで高並列な演算を行い,処理した結 果がまた CPU に転送される. アクセラレータ の処理時間の比較を表1で表す.従来のソフ トウェアベースの処理と比較し最大21倍 以上の高速化を達成できた.さらに,消費電 力は CPU に比較し50%までに削減できた.

さらに ,CPU と FPGA を両方使いヘテロジ: アスな処理を実装することでミスマッチが 多い場合でも高速な演算を行うことができ た.ミスマッチとはショートリードの一部が 参照ゲノム配列に完全に一致しない塩基で ある. ミスマッチ数が高いほど存在する可能

性が小さくなる.そこで,ミスマッチ数により,計算を CPU と FPGA に分割し並列に処理した.その時の処理時間の結果は表2に示す.これによりミスマッチ数が高い場合はヘテロジニアス処理が高速であることが明らかになった.

| ショート<br>リード数 | 従来方法の<br>処理時間(分) | 提案方法の<br>処理時間(分) | スピード<br>アップ |

|--------------|------------------|------------------|-------------|

| 126,605,856  | 371.5            | 30.8             | 12.0        |

| 59,087,904   | 482.0            | 22.0             | 21.8        |

| 277,328,866  | 2,091.8          | 182.2            | 11.4        |

表1:遺伝子配列一推定アクセラレータの処理時間比較

| ミスマッチ数 |        | CPU+FPGAでの<br>処理時間(秒) | 処理時間<br>削減(%) |

|--------|--------|-----------------------|---------------|

| 2      | 69.5   | 92.5                  | -40.4         |

| 3      | 447.7  | 160.8                 | 64.1          |

| 4      | 4134.9 | 219.1                 | 94.7          |

表2: ヘテロジニアス計算における処理時間の削減

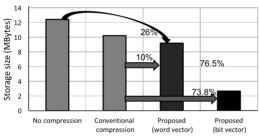

木に基づいた簡潔データ構造によるデータ量の削減結果は図9に示す.提案方法では従来の圧縮方法と比べ73%以上のデータ圧縮が可能になった.これにより FPGA からストレージへのアクセス回数の27%を削減することができた.

図9:提案した簡潔データ表現によるデータ量の削減

## 5 . 主な発表論文等 (研究代表者、研究分担者及び連携研究者に は下線)

## 〔雑誌論文〕(計 5件)

<u>Hasitha Muthumala Waidyasooriya</u> and Masanori Hariyama, Hardware-Acceleration of Short-read Alignment Based on the Burrows-Wheeler Transform, IEEE Trans. on Parallel and Distributed Systems, 查読有, Vol. 27, No. 5, 2016, pp. 1358-1372. DOI:10.1109/TPDS.2015.2444376

Hasitha Muthumala Waidyasooriya, Daisuke Ono and Masanori Hariyama, Hardware-Oriented Succinct Data Structure for Text Processing Based on Block-Size-Constrained Compression, International Journal of Computer Information Systems and Industrial Management Applications, 查読有, Vol.8,

2016, pp.1-11.

http://www.mirlabs.org/ijcisim/volume\_8 .html

#### [学会発表](計13件)

張山昌論, ウィッデヤスーリヤ ハシタムトゥマラ, 文字列検索アクセラレータのためのブロックサイズ制約に基づく簡潔データ構造, 電子情報通信学会技術報告(信学技報), リコンフィギャラブルシステム研究会, Vol. 116, No. 53, RECONF2016-2, pp.3-8,2016 年 05 月 19 日, (株式会社富士通研究所 岡田記念ホール)川崎

Hasitha Waidyasooriya, Daisuke Ono and Masanori Hariyama, Hardware-Oriented Succinct-Data-Structure based on the Block-Size-Constrained Compression, Proc. International Conference on Soft Computing and Pattern Recognition (SoCPaR), pp.136-140, 2015年11月15日, 九州大学(福岡)

Hasitha Muthumala Waidyasooriya, Daisuke Ono, Masanori Hariyama, Michitaka Kameyama, An FPGA Architecture for Text Search Using a Wavelet-Tree-Based Succinct-Data-Structure, International Conference on Parallel and Distributed Processing Techniques and Applications(PDPTA), pp.354-359, 2015 年07月28日、ラスベガス、(アメリカ).

[図書](計 0件)

### 〔産業財産権〕

出願状況(計 0件)

名称: 発明者: 権利者: 種類: 番号:

出願年月日:平成 年 月 日

国内外の別:

取得状況(計 0件)

名称: 発明者: 権利者: 種類: 番号:

出願年月日:平成 年 月 日 取得年月日:平成 年 月 日

国内外の別:

# 〔その他〕

- 6.研究組織

- (1)研究代表者

Waidyasooriya Ha (Waidyasooriya Hasitha)

東北大学・大学院情報科学研究科・助教

研究者番号:60723533

(2)研究分担者

( )

研究者番号:

(3)連携研究者

)

研究者番号: