# 科学研究費助成事業 研究成果報告書

令和 元年 5月31日現在

機関番号: 17401

研究種目: 基盤研究(C)(一般)

研究期間: 2016~2018

課題番号: 16K00077

研究課題名(和文)超大規模集積回路の高速検証を可能にする論理エミュレータの研究・開発

研究課題名(英文)Research and Development of High-speed Logic Emulator for Ultra-Scale Integrated

#### 研究代表者

久我 守弘 (Kuga, Morihiro)

熊本大学・大学院先端科学研究部(工)・准教授

研究者番号:80243989

交付決定額(研究期間全体):(直接経費) 3,400,000円

研究成果の概要(和文):集積回路の論理検証を行うためのFPGA-based論理エミュレータは広く用いられているものの,実装上の問題から動作速度が遅く複数FPGAへの分割実装も容易でない.そこで,高速シリアル通信を用いる新しいFPGA-based論理エミュレータの研究・開発を行った.提案エミュレータは,配線の仮想化により複数FPGA間の物理的端子数の制約から解放され高速化を図ることが可能になると共に,実装時の回路分割についても容易になる特徴がある.本研究により,エミュレータの基本構成,および,それに適した回路分割法を明らかにした.

# 研究成果の学術的意義や社会的意義

別元成果の子内的思義では云的思義では云いる表 高速シリアル通信によりFPGA間を接続するFPGA-based論理エミュレータにおいて,当初の目標性能である20MHz 以上の論理エミュレーション性能を達成できることを示した.また,提案論理エミュレータの利便性を向上させ るための検証回路の分割実装法についても汎用グラフ分割ツールを改良することで実現することができた.この ように本研究は新たなFPGA-based論理エミュレータの構成方式を示した点で学術的・社会的意義があるといえ

また,これらの基盤技術はFPGA-based論理エミュレータのみならず,複数のFPGAを利用するFPGA-basedアクセラレータへの応用にも役立つ点で意義がある.

研究成果の概要(英文): Although FPGA-based logic emulators for logic verification of integrated circuits are widely used in worldwide, they have low frequency operation due to implementation problems and cannot easily partition the test circuit into multiple FPGAs. Therefore, in this research, a novel FPGA-based logic emulator using high-speed serial communication is proposed. The proposed emulator connects among multiple FPGAs by the virtual wiring, which enables many inter FPGA wirings and it also enables the circuit partitioning easily. In this research, researcher clarifies the basic architecture of the emulator and the circuit partitioning method suitable for it.

研究分野: 計算機システム

キーワード: 論理エミュレータ FPGA 高速シリアル通信 回路分割

### 1.研究開始当初の背景

集積回路の検証を行う際に用いる FPGA-based 論理エミュレータは,計算機上でのシミュレータと比べて高速な検証を行うことができ,検証期間の大幅な短縮が図れるため広く用いられてきている.しかし,FPGA が備えている論理資源量や外部入出力ピンの数には物理的な上限があるため,これらを超える規模の回路は複数の FPGA に分割して搭載しなければならない.複数の FPGA を用いる論理エミュレータでは FPGA 間のデータ通信が必要になる.分割された検証対象回路の配線が FPGA 間にまたがるため,データ配線については入出力バッファによるディレイやデータ配線間のスキュー,またクロックにおいても複数 FPGA との間のスキューが

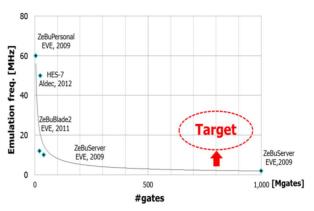

問題となる.図1に示すように,検証回路の規模が比較的小さい場合は高速なエミュレーションが可能であるものの,上記の影響によりFPGA-based 論理エミュレータ全体の動作周波数が大きく低下してしまう.また複数FPGAへの検証対象回路の分割実装も検証速度を維持できるように分割することは容易でない.そこで,複数のFPGAを用いる論理エミュレータの高速化およびその利便性の向上を目的として,上記の問題を克服できる新しいFPGA-based 論理エミュレータの開発研究に着手した.

図 1: FPGA-based 論理エミュレータの現状

#### 2.研究の目的

提案する FPGA-based 論理エミュレータの構成方式は "Virtual wire" (J.Babb, R.Tessier and A.Agaral, "Virtual wires: Overcoming pin limitations in FPGA-based logic emulators," IEEE Workshop on FPGA-based Custom Computing Machines (FCCM1993), pp.142-151, 1993.) の研究がベースとなっている. 仮想配線 (Virtual wire)を用いることにより FPGA 間の接続が従来の並列接続よりも物理的な配線を少なくできることに加え FPGA の物理端子の制約をなくすことができるため, FPGA 間の接続を容易にするとともに複数 FPGAへの分割実装も容易にすることが可能である. 近年の高性能・高機能 FPGA ではギガビットクラスの転送能力を持つ高速シリアル通信インタフェースを利用することができるため, FPGA 間の通信において高いデータ転送レートを実現することができる.このため, 2,000 本程度の仮想配線を使用することが見込め, 従来の FPGA エミュレータの欠点を解消することができる.

本研究の目的は,高速シリアル通信を利用した複数 FPGA による FPGA-based 論理エミュレータの基本構成およびその利便性を向上させるための手法を明らかにすることである.特に以の項目について研究・開発を進め,提案する FPGA-based 論理エミュレータの実現を図る.

- (1)高速シリアル通信を利用した FPGA-based 論理エミュレータのアーキテクチャ設計・開発:高速シリアル通信を用いる FPGA-based 論理エミュレータを設計・構築し,その有効性を示す.本研究においては比較的大規模な回路検証においても 20MHz 以上で動作可能な論理エミュレータの開発を目指す.

- (2) 複数 FPGA への回路分割の手法の開発:提案エミュレータに向けて適切な回路分割を行うための手法を検討し開発すると共に使用する際の利便性を考慮した分割実装ツールを開発する.

### 3. 研究の方法

(1) 高速シリアル通信を利用した FPGA-based 論理エミュレータのアーキテクチャ設計・開発

検証対象回路を複数の FPGA へ実装し論理エミュレーションを行う際には,サイクルベースシミュレータの概念により論理エミュレーションを行う.そのためには回路内に存在するフリップフロップ(FF)に着目して,FFが持つ内部状態を複数の FPGA 間でエミュレーションサイクル毎にシリアル転送を行うことで論理回路の同期動作を保証する.したがって,開発すべき重要なユニットは,FF内のデータを相互に通信するための通信仕様である.先ず通信インタフェースとしては FPGA が持つ高速シリアル通信用のトランシーバ/レシーバを用いる.通信プロトコルとしては FPGA ベンダが提供する高機能なシリアル通信 IP(例えば Xilinx 社 FPGAであれば Aurora等)を利用することも考えられるが,事前評価により通信レイテンシが非常に大きく論理エミュレーションの高速化には適切でないことが分かった.論理エミュレータの検証速度向上のために通信レイテンシができるだけ小さい通信 IPを利用する.具体的にはデータとクロックとを重畳させる8B10B や64B66B エンコーディング/デコーディングについては使用する一方で,これよりも上位レベルの通信階層にあたるフロー処理プロトコルは利用しな

いこととした.これは論理エミュレータとして使用する場合,FPGA 間の物理的なシリアル通信距離が短いため通信エラーをほとんど起こすことがないことを事前評価により確認したからである.

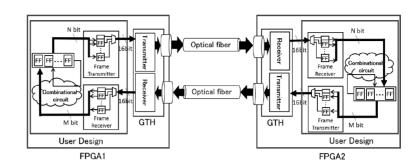

開発した論理エミュレータの概略を図 2 に示す .Xilinx 社製 Kintex Ultra Scale FPGA を用いる例では ,GTH トランシーバと呼ばれる光通信ベースのシリアルインタフェースを使用できる .

この GTH トランシーバは 500Mb/s から 16.375Gb/s のラインレートをサポートしている.この GTH トランシーバ/レシーバー対し,検証する回路を FF が並ぶように分割した分割回路に FF 内のデータを通信フレームに相当でマルチプレクと受信行えくずる.

図2:論理エミュレータの概略図

#### (2) 複数 FPGA への回路分割の手法の開発

複数の FPGA 向けに検証対象回路の分割を行う際には,サイクルベースエミュレーションを行えるようにいくつかの制約を守る必要がある.具体的には FF 間の組合せ回路が複数の FPGA を横断するような分割を避ける.これにより FF が保持する内部状態のみを各エミュレーショ

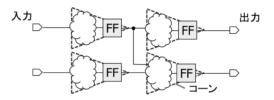

ンサイクルに 1 回のみ FF ないデータの通信を行うことで論理エミュレーションを行えることが保証できる.このアイデアによる回路分割手法としてロジックコーンに着目した方法に着目した.ロジックコーンは図 3 に示すように FF を頂点として,その FF の値を決定する論理ゲートおよび外部入力端子の集合と定義する.このロジックコーン単位で回路分割を行うことができる.

図3:ロジックコーンの概念図

グラフを分割ツールとして、汎用のグラフ分割ツールである METIS やハイパーグラフの分割を行うことができる hMETIS が知られている.分割対象回路をロジックコーンをノードとしたグラフとして表現することで,グラフ分割ツールを利用して回路の分割を行うことができる.しかし,汎用のグラフ分割ツールでは2つの分割したグラフにまたがるエッジ数が少なくなるように分割することができるものの,論理エミュレータ向けに回路分割を行うために利用するには使いづらい面がある.具体的には,複数 FPGA に回路分割する際に回路分割の比率を制御したり,クリチカルパスを考慮し分割した回路の遅延が大きくばらつかないように考慮したりする必要がある.本研究ではソースコードが入手でき,カスタマイズが可能な METIS をベースとして、分割比やクリチカルパスを考慮することができる回路分割ツールとして改良を行った.

また,論理エミュレータの利便性を向上させるためには,論理エミュレータへ実装する際の手間をいかに削減するかが鍵となる.論理エミュレータに分割実装される回路はそれ単体では動作することはできず,テストベンチに相当する階層を用いて検証回路から/への入出力を制御しなければならない.また,回路分割面には高速シリアル通信用のトランシーバ/レシーバや,それとデータの授受を行うマルチプレクサ/デマルチプレクサを配置する必要がある.これらの作業を自動化することにより,エミュレータの利便性を向上させる.ホストとなる計算機上で,これらの処理を自動で行うことにより,ユーザにとって容易に利用することができる論理エミュレーション環境を提供する.

# 4. 研究成果

Xilinx 社製 Kintex UltraScale FPGA である XCKU040-2FFVA1156E を使用した KCU105 Evaluation Kit ボード 2 枚を使用し,ベンチマーク回路を検証回路とした場合の分割実装による論理 エミュレータの評価を行った.3 種類の VTR ベンチマーク回路(fir\_scu\_rtl\_restructured\_for\_cmm\_exp, rs\_decoder1 および mac2)に加えて,DES 暗号・復号化回路の性能最適化版および面積最適化版の 2 つのベンチマーク回路を追加し,論理エミュレータとしての適用させるための検討を行った 検証回路の分割に際しては METIS をベースとして面積最適化指向で分割回路間の信号数(転送ビット数)が最小となるような回路分割を行っている.評価の結果,6Gbps の通信性能を備える 1 本の高速シリアル通信では  $5.73 \sim 11.70$ MHz でエミュレーション可能であることが分かった.また Vertex UltraScale+ デバイスである XCVU13P を用い

32.75Gbps の通信性能を備える 128 本の高速シリアル通信が用意できる場合は 29.97 ~ 45.02MHz での動作が見込めると予測することができ,当初の目標性能を達成できることを示した.これらの研究成果の詳細については雑誌論文および学会発表において公開した.詳細については雑誌論文 および を参照されたい.また,128 本の高速シリアル通信が利用できる場合,9 個のFPGA を完全結合する場合には 1 接続当たり 16 本の高速シリアルリンクを使用できるなど,検証回路の規模に応じた論理エミュレータの構成を選択できることを確認した.

また,本研究に関連して FPGA の高速シリアル通信を利用した複数 FPGA へのアプリケーション実装事例として,データベース処理向けのハードウェアソータやデータフィルタリング処理ハードウェアについても実装を試みた.いずれの場合も,プロセッサによるソフトウェア処理と比較して,高速に実行可能であり複数 FPGA への分割実装が有用であることを示した.本研究成果の詳細については,雑誌論文 および を参照されたい.

#### 5 . 主な発表論文等

### 〔雑誌論文〕(計4件)

村瀬 大,高木大智,尼崎太樹,久我守弘,飯田全広,末吉敏則:"高速シリアル光インターコネクトを用いた FPGA 分割実装,"電子情報通信学会技術研究報告 RECONF2016-56, vol.116, no.417, pp31-36, Jan. 2017. (査読なし)

M.Amagasaki, F.Murase, M.Kuga, M.Iida, and T.Sueyoshi: "FPGA based ASIC Emulator with High Speed Optical Serial Link," Proc. of the 8th International Workshop on Highly-Efficient Accelerators and Reconfigurable Technologies (HEART2017), Article No. 18, June 2017. doi:10.1145/3120895.3120913 (查読有)

高木大智,趙謙,久我守弘,尼崎太樹,飯田全広,末吉敏則:"FPGA の高速シリアル通信を用いたクラスタコンピューティング環境の一検討,"火の国情報シンポジウム2018,A6-1,情報処理学会九州支部,pp1-6,March.2018. (査読なし)

中川裕貴, 久我守弘, 尼崎太樹, 飯田全広, 末吉敏則: "ストリーミングによるデータベースフィルタ処理の一検討,"電子情報通信学会技術研究報告 RECONF2018-33, vol.118, no.215, pp79-84, Sep. 2018. (査読なし)

# [学会発表](計4件)

村瀬 大,高木大智,尼崎太樹,久我守弘,飯田全広,末吉敏則: "高速シリアル光インターコネクトを用いた FPGA 分割実装,"電子情報通信学会リコンフィギャラブルシステム研究会 RECONF2016-56, vol.116, no.417, pp31-36, Jan. 2017.(2017/1/23 発表)

M.Amagasaki, F.Murase, M.Kuga, M.Iida, and T.Sueyoshi, : "FPGA based ASIC Emulator with High Speed Optical Serial Link," Proc. of the 8th International Workshop on Highly-Efficient Accelerators and Reconfigurable Technologies (HEART2017), Article No. 18, Bochum, Germany, 9th June 2017.

高木大智,趙謙,久我守弘,尼崎太樹,飯田全広,末吉敏則: "FPGA の高速シリアル通信を用いたクラスタコンピューティング環境の一検討,"火の国情報シンポジウム2018,A6-1,情報処理学会九州支部,pp1-6,March.2018.(2018/3/2発表)

中川裕貴, 久我守弘, 尼崎太樹, 飯田全広, 末吉敏則: "ストリーミングによるデータベースフィルタ処理の一検討," 電子情報通信学会リコンフィギャラブルシステム研究会 RECONF2018-33, vol.118, no.215, pp79-84, Sep. 2018. (2018/9/18 発表)

# [図書](計0件)

### 〔産業財産権〕

- ○出願状況(計0件)

- ○取得状況(計0件)

### 〔その他〕

ホームページ等 http://www.arch.cs.kumamoto-u.ac.jp/

# 6.研究組織

(1)研究分担者 なし

(2)研究協力者

研究協力者氏名: 趙 謙

ローマ字氏名: (ZHAO, Qian)

研究協力者氏名: 尼崎 太樹

ローマ字氏名: (AMAGASAKI, Motoki)

研究協力者氏名: 飯田 全広

ローマ字氏名: (IIDA, Masahiro)

研究協力者氏名: 末吉 敏則

ローマ字氏名: (SUEYOSHI, Toshinori)

※科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等については、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。