#### 研究成果報告書 科学研究費助成事業

今和 2 年 7 月 9 日現在

機関番号: 26402

研究種目: 基盤研究(C)(一般)

研究期間: 2016~2019

課題番号: 16K00082

研究課題名(和文)省電力セルフタイム回路によるヘテロジニアス無線通信プロセッサ

研究課題名(英文)Heterogeneous Wireless Communication Processor Based on Low-Power Self-Timed Circuits

研究代表者

岩田 誠(IWATA, Makoto)

高知工科大学・情報学群・教授

研究者番号:60232683

交付決定額(研究期間全体):(直接経費) 3,400,000円

研究成果の概要(和文):本研究では、広域系・無線LAN系・ミリ波系回線を統合した将来の無線通信環境に必須となる、複数の無線通信方式に適応可能なヘテロジニアス無線通信プロセッサの構成法を明らかにすることにある。このため、マルチユーザMIMOによるマルチモード受信機を想定し、変復調、誤り訂正、MACを対象に、(1)パイプライン並列アルゴリズム、(2)それらを多重に処理可能なストリーム信号処理アーキテクチャ、および、(3)それを構成する高機能メモリ機構と専用エンジンを省電力セルフタイムパイプラインSTP回路により実現する方法、に関して、これらの基礎技術を明らかにし、いくつかの学術論文として公表した。

研究成果の学術的意義や社会的意義本研究の成果は、セルフタイム回路を基盤として、複数の異速度信号ストリームを多重に処理可能なプロセッサを構成することによって、WPAN、WLAN、MBWA等の無線信号ストリームを円滑に多重処理可能なシステムを実現できる見通しを得られたことである。これによって、異種の無線に対応したチップ/回路モジュールを組み合わせた複雑なハードウェア構成ではなく、本提案のように均質なアーキテクチャで多重処理が可能になるヘテロジニアス無線通信プロセッサを実現できる点に学術的意義がある。これによって、将来的には、無線通信システムの設計・製造コストの低減や信頼性の向上にも寄与することが期待できる点に社会的意義がある。

研究成果の概要(英文): This research aimed to establish how to construct a heterogeneous wireless communication processor that can be adapted to multiple wireless communication systems, which will be essential for future wireless communication environments that integrate wide area, wireless LAN, and millimeter wave lines. In the research, we targeted modulation, error correction and MAC functions embedded in multi-mode receivers of multi-user MIMO system and studied (1) pipeline parallel algorithms of them, (2) stream signal processing architecture that can process them in parallel, and (3) low-power self-timed pipeline STP circuit implementation of dedicated engine to configure them. These basic techniques were revealed and published as several academic papers.

研究分野:計算機アーキテクチャ

キーワード: ヘテロジニアス無線通信 セルフタイム回路 データ駆動 ストリーム処理 変復調 FFT

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。

## 様 式 C-19、F-19-1、Z-19(共通)

## 1.研究開始当初の背景

利用者のロケーションや状況に応じて、安定した無線通信手段を利用可能にするために、広域の携帯電話系の IEEE802.16e や LTE-Advanced、無線 LAN 系の IEEE802.11ac、近距離系の IEEE802.15.3c や WiGig(802.11ad)等、より高速な無線通信規格の策定が国内外で進められている。これらの異なる無線通信方式を状況に応じて適応的に活用できるヘテロジニアス無線通信ネットワークシステムの構築が、大規模災害時の安定した通信手段確保や人口密集地域でのサービス確保の観点から、喫緊の課題となっている。さらに、3.11 のような大規模災害時には、無線キャリアの基地局が倒壊しても、近隣の無線通信可能な端末間で柔軟にアドホックメッシュネットワークを構成して、緊急警報や避難経路情報等を授受することは、将来の安全・安心な情報通信基盤技術には極めて重要である。

研究開発当初、研究代表者らは、複数の無線通信方式を利用環境や電波干渉状況に応じてシームレスに切り替えて、接続性・速度の向上を図るために、マルチバンドマルチモードスケーラブル受信機用の周波数領域等化器 FDE (frequency domain equalizer)の ASIC 化に世界に先駆けて成功し、高速で高品質な変復調システム実現の鍵となる要素技術を確立していた。しかしながら、現状の Qualcomm 社等の商用ベースバンドプロセッサでもそうであるが、異なる搬送周波数や帯域を前提とした複数の信号系列を同一の回路モジュール内で処理することができないため、個々の通信方式毎に専用 LSI を搭載した複数モジュール構成を採用せざるを得ず、ヘテロジニアス無線通信端末の実現上の障害となっていた。

また一方で、研究代表者らは、高い実時間多重処理能力を持つ通信処理向きデータ駆動チップマルチプロセッサの低消費電力化技術の研究プロジェクトにおいて、パイプライン段毎の細粒度パワーゲーティング機構と実行時電圧制御機構を備えた低消費電力化自己同期型エラスティックパイプライン回路 STP (self-timed elastic pipeline)を世界で初めて提案し、この回路を活用した ZigBee 無線通信システムを試作した結果、従来システムに比べて、1/100 程度の低消費電力化が可能な見通しを得ていた。

この STP は、大域クロックを用いないセルフタイム回路であるため、多重処理時等において 厳密なスケジューリングが困難な状況でも一時的な負荷変動を緩衝する能力(エラスティック 性)を生来的に有しており、この特質が異種・異速度の複数の無線通信信号系列を同時に多重に 処理できる単一 LSI モジュールの実現法の基礎として極めて有望であると着想した。

#### 2.研究の目的

本研究課題は、この着想の下に、広域系・無線 LAN 系・ミリ波系回線を統合した将来の無線通信環境に必須となる、複数の無線通信方式に適応可能なヘテロジニアス無線通信プロセッサの構成法を明らかにするものである。このため、マルチユーザ MIMO によるマルチモード受信機を想定し、変復調、誤り訂正、MAC を対象に、(1)パイプライン並列アルゴリズム、(2)それらを多重に処理可能なストリーム信号処理アーキテクチャ、および、(3)それを構成する高機能メモリ機構と専用エンジンを省電力 STP 回路により実現することを目的として、研究を実施してきた。

#### 3.研究の方法

平成 28 年度から 31 年度までの 4 年間で、(1)各共通処理 (FFT + DEMOD、FEC、MAC)のパイプライン並列処理アルゴリズムに基づくストリーム信号処理のモデル化を検討し、(2)それらの多重処理が可能なストリーム信号処理 LSI の基本アーキテクチャを設計すると同時に、(3)各共通処理における高負荷な処理を高機能メモリ型専用回路エンジンにより高速化する技法、を検討してきた。

#### (1)ストリーム信号処理のモデル化

無線通信における共通処理のパイプライン並列処理アルゴリズムを検討し、ストリームを単位として処理を駆動する水準のマクロな並列処理性と、ストリームを構成する要素データに対するプリミティブな細粒度の並列処理性を明示的に記述可能なストリーム駆動プログラムの表記法ならびにその解釈実行規則をストリーム駆動計算モデルとして定式化した。この表記法では、マクロなストリーム水準と細粒度データの境界を、プログラムモジュール階層のインタフェースとなる入出力ポートにより表現する。これによって、異なる水準の並列処理性がシームレスに明示されるため、ストリーム内の要素が部分的にでも利用可能になった段階で処理を駆動する(ノンストリクトな)実行を許容した性能向上が可能になった。さらに、この入出力ポートのセマンティクスを解釈実行するためのストリーム操作命令群(複製、並び替え、部分抽出操作等)に加えて、後述する(3)の無線通信処理専用の高速 STP ハードウェア機構を駆動するための命令群を統合して、命令セットとして体系化した。

## (2)ストリーム信号処理プロセッサアーキテクチャの検討

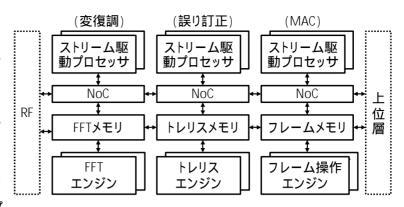

無線通信の受信機では一般に、変復調から誤り訂正 CODEC、MAC に至る処理は一方向のパイプラインにより構成される。また、送信機ではその逆方向になる。この性質を活用して、主要な共通処理単位でそれぞれを専用に担当するヘテロジニアスなクラスタを構成し、専用回路による高速化だけではなく、ストリーム水準でのマクロな並列処理をプログラム可能なプロセッサを

実現し、システム全体として 円滑なストリーム流を維持し て高速化を図った。各クラス タでは、プロセッサ間および エンジン間のオンチップネッ トワークを局所的に接続し て、いわゆるニアメモリ計算 機構を構成して、不必要なデ ータ移動を極小化し、電力当 りの性能向上を追究する。さ らに、クラスタ間では、各機 能メモリ間でデータを直接的 に授受することによって、プ ログラム実行制御のオーバへ ッドを極力低減する方法を検 討した。

図 1. ヘテロジニアス無線通信プロセッサの基本構成

## (3)共通処理用専用エンジンの STP 実現法の検討

無線通信処理における、変復調、誤り訂正 CODEC、および、MAC のそれぞれにおいて、以下の点が高負荷な機能となり、その高速化が鍵となる。したがって、これらの処理のうち、変復調エンジンにおける FFT を対象として、異速度のデータ流の揺らぎを緩衝できるエラスティック性を持つ STP を活用した実現法を検討した。FDE には一般に、\$2^{12}\$-point 数以上の超高速 FFT が複数必要になる。多様なブロック長に対する FFT エンジンを構成するために、基数 4~8 の小規模 FFT の縦続 / 並列接続によって、要求スループットやユーザ数に応じた同時並行・並列動作が可能な構成を検討した。

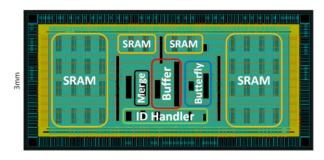

図 2. FFT コアの 65nmCMOS 回路レイアウト

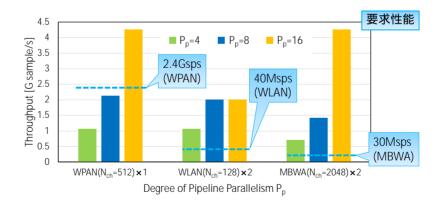

図3. FFT コア×4 構成の多重処理性能

提案 FFT コアの 65nmCMOS 回路レイアウトを図 2 に示す。このレイアウトでは、SRAM モジュールの最適化が施されていないが、最終的には、この 20%程度には集積化できる見通しを得た。また、ポストレイアウト評価として、この FFT コアを 4 つ接続した並列 FFT 構成の性能評価結果を図 3 に示す。この結果から、5 種類の異速度データを受理しながら、WPAN 用 512pointFFT×1、WLAN 用 128pointFFT×2、MBWA 用 2048pointFFT×2 を同時に多重処理できることが確認できた。

さらに、これらの基礎的検討に基づき、各共通処理のストリーム駆動プログラムのシミュレーション環境の構築、ならびに、昨年度に設計した専用エンジンを搭載したプロセッサを対象として、実時間タスクスケジュールが可能なハードウェアスケジューラを検討した。一般に OS に実装されるソフトウェアスケジューラは実行時オーバヘッドが大きい。これに対して、今年度に開

発したハードウェアスケジューラは、オーバヘッドを極小化して、かつ、STP 回路に基づくデータ駆動プロセッサ上での多重処理性能を最大限に引き出せる構成となっている。本スケジューラを搭載したプロセッサを 65nmCMOS ライブラリを用いて回路合成して、評価したところ、プロセッサ本来のスループット(op./sec.)の劣化を招かずにスケジュール可能なことを確認できた。

#### 4. 研究成果

本研究の最大の成果は、セルフタイム回路を基盤として、複数の異速度信号ストリームを多重に処理可能なプロセッサを構成することによって、WPAN、WLAN、MBWA 等の無線信号ストリームを円滑に多重処理可能なシステムを実現できる見通しを得られたことである。これによって、異種の無線に対応したチップ/回路モジュールを組み合わせた複雑なハードウェア構成ではなく、本提案のように均質なアーキテクチャで多重処理が可能になるヘテロジニアス無線通信プロセッサを実現することができる。

本研究課題を実施中に見通しが得られた基礎技術によって、システムの設計・製造コストの低減や信頼性の向上も期待できる。一方で、ヘテロジニアス無線通信プロセッサ全体を実現する観点では、誤り訂正や MAC 等、個別の専用エンジンの最適化アルゴリズム等、残された技術的課題もある。また、実用化に向けては、PHY や AD/DA を含めたシステム全体の実装・検証も実施する必要がある。

末筆ながら、本研究課題に対する日本学術振興会のご支援に感謝申し上げます。

#### 5 . 主な発表論文等

【雑誌論文】 計1件(うち査読付論文 1件/うち国際共著 0件/うちオープンアクセス 0件)

| 「一根認識又」 allft(フら直説引調又 lff/フら国際共者 Uff/フらオーノファクセス Uff/ |                        |  |

|------------------------------------------------------|------------------------|--|

| 1.著者名 植田 和憲、岩田 誠、馬場 健一、下條 真司                         | 4.巻                    |  |

| 2 . 論文標題<br>mesh STAの移動特性を考慮した自律無線メッシュネットワーク構成法      | 5.発行年<br>2020年         |  |

| 3.雑誌名 情報処理学会論文誌                                      | 6.最初と最後の頁<br>297 - 305 |  |

| 掲載論文のDOI(デジタルオブジェクト識別子)<br>なし                        | 査読の有無<br>有             |  |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難               | 国際共著                   |  |

## 〔学会発表〕 計5件(うち招待講演 0件/うち国際学会 5件)

## 1.発表者名

Kanji Nagano and Makoto Iwata

## 2 . 発表標題

Area-Efficient FPGA Implementation of Self-Timed Data-Driven Processor

#### 3 . 学会等名

The 7th International Symposium on Frontier Technology (国際学会)

# 4 . 発表年

2019年

#### 1.発表者名

Kazuma Fukuda, Yushin Wada, and Makoto Iwata

#### 2 . 発表標題

Decentralized Hardware Scheduler for Self-Timed Data-Driven Multiprocessor

## 3 . 学会等名

2018 International Conference on Parallel and Distributed Processing Techniques and Applications (PDPTA'18)(国際学会)

#### 4 . 発表年

2018年

## 1.発表者名

Yushin Wada, Kazuma Fukuda, and Makoto Iwata

## 2 . 発表標題

Least Slack Time Hardware Scheduler Based on Self-Timed Data-Driven Processor

## 3 . 学会等名

2018 International Conference on Parallel and Distributed Processing Techniques and Applications (PDPTA'18)(国際学会)

## 4 . 発表年

2018年

| 1   | <b> </b> |

|-----|----------|

| - 1 | ,光衣有石    |

Kazuma FUKUDA, Hiroki SHIBUTA, and Makoto IWATA

## 2 . 発表標題

Priority-Based Hardware Scheduler for Self-Timed Data-Driven Processor

#### 3 . 学会等名

International Conference on Parallel and Dstributed Processing Techniques and Applications (国際学会)

#### 4.発表年

2017年

## 1.発表者名

Masahiro TABARA, Hiroki SHIBUTA, and Makoto IWATA

## 2 . 発表標題

Pipelined FP Array for Stream-Driven Image Processor

## 3 . 学会等名

International Conference on Parallel and Dstributed Processing Techniques and Applications (国際学会)

## 4.発表年

2017年

## 〔図書〕 計0件

## 〔産業財産権〕

〔その他〕

\_

6 . 研究組織

| <br>J ・ W   プロボロ 声戦       |                       |    |  |

|---------------------------|-----------------------|----|--|

| 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |  |