# 科学研究費助成事業研究成果報告書

令和 元年 5月22日現在

機関番号: 82118

研究種目: 基盤研究(C)(一般)

研究期間: 2016~2018

課題番号: 16K05387

研究課題名(和文)次世代型論理素子を全面展開する衝突型加速器実験トリガーシステムの構築

研究課題名(英文)Development and performance studies of SoC FPGA module for high energy experiment application

研究代表者

佐々木 修(Sasaki, Osamu)

大学共同利用機関法人高エネルギー加速器研究機構・素粒子原子核研究所・教授

研究者番号:30178636

交付決定額(研究期間全体):(直接経費) 3,600,000円

研究成果の概要(和文):次世代型論理素子(SoC FPGA)の高エネルギー実験測定器の制御システムやトリガーシステムへの導入可能性について検証を行った。

SoC素子としてXilinx社のZynq-7000シリーズを採用し、評価ボードによる基本性能の確認や開発環境の整備を行った。SoCのCPUには基本ソフトであるLinuxを実装し、カーネルやデバイスドライバーの整備を進めた。この結果を踏まえ、SoC素子を実装した汎用VMEモジュールの開発・製造を行うことが出来た。本モジュールを用いて、ATLAS実験への導入を目指した基本性能評価を進める予定である。

研究成果の学術的意義や社会的意義開発・製造されたSoC FPGA搭載VMEモジュール及び基本ソフトウエアは、高エネルギー実験への導入を前提に開発されたものであり、このモジュールの試験を通して得られる知見は、他の素粒子実験用測定器のみならず加速器制御等への広範な応用に大きく役立つものである。開発されたハードウエア、ソフトウエアは汎用性を持つものであり、モジュール開発を通して習得した高速電子回路等のノウハウも、OpenITと呼ばれるプロジェクトの公開サーバなどを通して一般に公開する予定である。また、同様の開発を目指す若手研究者への技術移転や助言などを行っていく予定である。

研究成果の概要(英文): We have evaluated the possibility of introducing next-generation logic devices: SoC FPGA into control system and trigger system for high-energy experiments. We adopted the Xilinx Zynq-7000 series as an SoC FPGA, and confirmed the basic performance with the evaluation board and maintained the development environment. We implemented Linux, which is the basic software, on the SoC CPU, and worked on the development of the kernel and device drivers. Based on the result, we were able to develop and manufacture a general-purpose VME module mounting the Zynq FPGA. Using the module, we plan to promote basic performance evaluation aiming at SoC FPGA introduction to the ATLAS experiment.

研究分野: 素粒子実験

キーワード: SoC FPGA トリガー ギガビット高速通信 Zyng Xilinx LHC ATLAS

## 様 式 C-19、F-19-1、Z-19、CK-19 (共通)

## 1. 研究開始当初の背景

我々はLHC加速器ATLAS実験の前後方ミューオン測定器のトリガー及びデータ読み出しシステムの構築運用に長年にわたり参画してきた。本実験はヒッグス粒子の発見や広い範囲の新物理探索などで成功を収めてきた。LHC加速器は、HL(High Luminosity)LHCとしてエネルギー及びルミノシティの増強を行う計画である。HL-LHCでは衝突頻度とルミノシティの増強による膨大なデータ量の増加が予測される。そのため、より高精度かつ複雑なトリガー判定論理の導入やより大容量・高速なデータ読み出しが必要になる。

書き換え可能なデジタル集積回路 FPGA は柔軟性の高いシステム構成を可能にすることが出来、実験の色々な局面で広く使用されてきた。また、近年の素子資源の増大、高速化、10Gbps を超えるシリアル通信の導入などには目覚ましい発展がある。しかし、次第に規模が大きくなるにつれて問題も見えてきた。論理回路が巨大で複雑になると問題が発生したときの原因究明が非常に困難になる。最初から必要な診断機能をすべて組み込んでしまうことは不可能に近い。そこで、最近着目されているのが次世代型論理素子である SoC(System on Chip)である。SoC ではマイクロプロセッサ CPU と大規模 FPGA が密結合されている。FPGA 上に構成されたトリガー判定回路の様々な情報をソフトウエアから直接読み書きできる。ハードウエアによる高速並列処理とソフトウエアによる柔軟なシステム運用をチップ上に統合することができる。HL-LHC ATLAS 実験の次期トリガー・読み出し・制御システムへの SoC FPGA 全面採用を目指し、その性能検証を行いたい。

### 2. 研究の目的

LHC 加速器 ATLAS 実験の前後方ミューオントリガーシステムのアップグレード計画では、検出器上の電子回路を極小にしてすべての信号情報を測定室へ転送しトリガー判定等を行う。そこでは大規模なプログラム可能論理素子 FPGA が使われるが、高速性とともに高い柔軟性が要求される。それを実現する技術として次世代型の論理素子 SoC を検討する。SoC は FPGA とそれに強く結合した CPU からなっており、FPGA 上の論理モジュールを直接ソフトウエアで制御可能になる。SoC の基本性能を確認し、次に実際の ALTAS 実験データを元にトリガーシステム構築の構成要素としての有効性を検証する。開発の手法や成果物は種々の実験に応用可能であり、広く公開し利用者のコミュニティ形成を目指す。

#### 3. 研究の方法

SoC FPGA 素子として Xilinx 社の Zynq-7000 シリーズを採用し、評価ボードによる基本性能の確認や開発環境の整備を行った後、汎用モジュールを作成する。汎用モジュールは計算機インターフェースと高速シリアル通信を搭載しており、トリガー・データ読み出しシステムのプロトタイプを構築できる。また、システム制御のプラットホームとしての使い方の可能性についても検証する。SoC の CPU には基本ソフトである Linux を実装し、カーネルやデバイスドライバーの整備を進める。ATLAS 実験の実際のデータを用いて様々なトリガー判定論理の検証を行い、結果を用いてアップグレードの提案書としてまとめる。開発されたハードウエアとソフトウエアの情報はレポジトリに集積し一般に公開する。

## 4. 研究成果

Soc FPGA 素子として Xilinx 社の Zynq-7000 シリーズを候補として、当 FPGA を搭載した評価キット ZC706 と子ボード搭載用 FMC 接続ボードを購入し性能試験を行った。基本ロジック部及び CPU 部の基本動作周波数や入出力などの性能評価をした。合わせて、高速シリアル通信、Gigabit Ethernet や USB、DDR 等の外部メモリインターフェースの性能も確認された。平行して開発ツールソフトウエア等の開発環境の整備も行われた。Linux OS を用いたソフトウエア環境を構築し今後の汎用モジュール設計のベースとすることが出来た。ロジック部と CPU 部を接続する部分に関しては、標準的な CPU インターフェースを実装し Linux 上のソフトウエアからのアクセス性能について各種実測データを取得することが出来た。また、Linux カーネルやデバイスドライバー

の開発、種々の実験用ソフトウエアライブラリの移植作業も行われた。

評価キットでの試験結果をもとに汎用モジュールの仕様を決定した。汎用モジュールは VME 規格に準拠したもので、ネットワークや USB、SD カード等の計算機インターフェースに加えて 12.5 Gbps で動作する高速シリアル通信のレーンを装備する。また、潤沢なソフトウエア作業領域を確保するための DDR3 メモリーを搭載する。加えて、アトラス測定器用 SoC FPGA モジュール設計に向けての各種試験ができるように子ボード搭載用 FMC コネクタを置き FPGA 間通信や JTAG 通信等も実装した。回路部品の選定、回路デザイン及び基板レイアウトには、非常に長時間を費やすことになったが、設計を通して多くのことを学びノウハウを蓄積することが出来た。完成モジュールの写真を添付する。完成したモジュールの試験はまだ始まったばかりではあるが、入出力関連の基本動作は確認された。

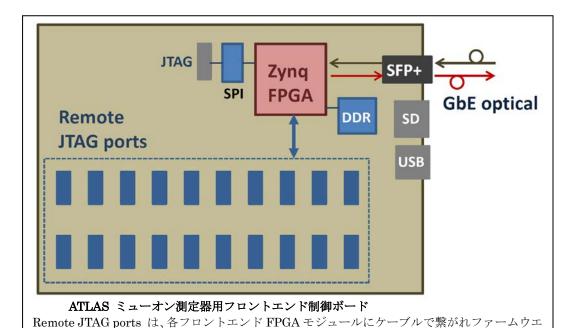

ATLAS 実験の前後方ミューオン測定器では、当初 SoC FPGA をトリガーシステムの中心に据えよ うと考えていたが、今回の我々の試験によりロジック部と CPU 部間での通信に予想以上の時間を 要することが判明し、レベル0/1トリガーシステムへの全面的な SoC FPGA の使用には多くの問 題を有することが明らかとなった。しかし、Zynq FPGA は、多様なインターフェースをサポート しており、それらの機能を Linux ベースのソフトウエアで作動させることが可能であり、測定器 フロントエンドシステムの制御・モニターのプラットホームとして利用することが出来る。我々 の ATLAS ミューオン測定器システムでは HL-LHC に対応するため測定器系の大幅なアップグレー ドを計画している。測定器に直付の ASD ボードを除き全てのエレクトロニクスシステムが更新さ れる。ASD ボードからのデジタル信号は FPGA を搭載したフロントエンドボードに一旦集められ ボード当たり 16 Gbps の高速通信によって測定室へと転送される。このボードは約 1500 枚導入 される。このボードの制御、ファームウエアの更新や放射線によるファームウエアの書き換わり のモニター・再書き込みなどの手順の確立が重要となる。この目的のために、Zynq FPGA を用い た測定器フロントエンド制御モジュールを開発し効率よくフロントエンド FPGA ボードの制御を 行う計画である。それに必要な遠隔での Zynq FPGA 搭載制御モジュールのシステム起動手順の確 立や本モジュール経由でのフロントエンド FPGA モジュールへのファームウエアダウンロードな どを実証検証する計画である。また、この制御モジュールは放射線環境下に置かれるものである ため、放射線耐性についても今後今回開発されたモジュールを用いて試験を行っていく予定であ る。フロントエンド制御モジュールのブロック図を下に示す。

今までの研究結果及び今後の検証結果は、下記ホームページなどで広く公開していく予定である。

# 5. 主な発表論文等

〔学会発表〕(計 3 件)

アのダウンロードや制御に使われる。

- ① 堀口楠日、藏重久弥、前田順平、奥村恭幸、<u>坂本宏</u>、東田旺大、池野正弘、<u>佐々木修</u>、Zynq ベース汎用モジュール PT-Z の開発、日本物理学会 2018 年春季大会(東京理科大学・野田)

- ② <u>坂本宏</u> 他、SoC(System on Chip)デバイスによる汎用 VME モジュール開発、日本物理学会 2017 年秋季大会(宇都宮大学・宇都宮)

- ③ <u>坂本宏</u> 他、SoC(System on Chip)デバイスによるフロントエンドエレクトロニクス開発、 日本物理学会 2016 年秋季大会(宮崎大学・宮崎)

[その他]

ホームページ等

$\frac{\text{http://www.icepp. s. u-tokyo. ac. jp/}^{\text{sakamoto/research/atlas/tgcelex/vivado/index. html}}{\text{http://openit. kek. jp/project/ptz/ptz}}$

# 6. 研究組織

(1)研究分担者

研究分担者氏名: 坂本 宏

ローマ字氏名: (SAKAMOTO, Hiroshi)

所属研究機関名:東京大学

部局名:素粒子物理国際研究センター

職名:名誉教授

研究者番号 (8 桁): 80178574

(2)研究協力者

研究協力者氏名:池野 正弘 ローマ字氏名:(IKENO, Masahiro) 研究協力者氏名:前田 順平 ローマ字氏名:(MAEDA, Junpei) 研究協力者氏名:奥村 恭幸

ローマ字氏名: (OKUMURA, Yasuyuki)

%科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等については、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。