# 科学研究費助成事業 研究成果報告書

令和 元年 6月14日現在

機関番号: 84431

研究種目: 基盤研究(C)(一般)

研究期間: 2016~2018

課題番号: 16K06288

研究課題名(和文)高性能レアメタルフリーフレキシブル酸化物トランジスタおよび論理回路の開発

研究課題名(英文)Development of rare metal free high performance flexible oxide transistors and logic circuits

### 研究代表者

佐藤 和郎 (SATOH, Kazuo)

地方独立行政法人大阪産業技術研究所・和泉センター・主幹研究員

研究者番号:30315163

交付決定額(研究期間全体):(直接経費) 3,700,000円

研究成果の概要(和文):本研究の目的は、ディスプレイやバイオセンサーへの応用を目指し、安価で毒性の無いZn2Sn04(ZTO)を用いて、フレキシブル基板上に高性能薄膜トランジスタ(TFT)を作製する事である。本研究の成果としては、ZTO成膜時の酸素流量比やゲート絶縁膜の厚さがTFT特性に対して大きな影響を与える事を明らかにした事である。また、ZTOウェットエッチング時の特性劣化に対しては、ポストアニールが有効である事を見出した。その結果、フレキシブル基板であるポリイミドフィルム及び超薄板無アルカリガラス上に電界効果移動度が10 cm2/Vsを超える高性能なTFTを作製できた。さらには、インバーター等の試作も行った。

研究成果の学術的意義や社会的意義 本研究の学術的成果は、ZTO材料を用いたTFTの特性に対し、成膜時の酸素流量比やゲート絶縁膜及びポストアニールが大きな影響を与えることを明らかにした事である。また、インバーターの試作にも成功した。本研究の成果により、レアメタルフリーで環境にも調和するZTO材料を用いて、フレキシブルディスプレイ駆動用TFTやバイオセンサーへの応用可能性を見出す事に成功した。この事は、環境に優しく持続可能な社会の実現に貢献するものであり、社会的意義も大きい。

研究成果の概要(英文): The purpose of this study is to fabricate Zn2Sn04 (ZT0) based high performance thin film transistors (TFTs) on flexible substrates for applying to display and biosensors. ZT0 thin films have attracted much attention as a new channel material due to low cost and non-toxicity. In this study, it became clear that oxygen flow ratio during sputtering and gate insulator film thickness significantly affect the properties of ZT0 based TFTs. In addition, the drain source current does not modulate with the gate voltage after the ZT0 films are patterned by wet etching for fabricating TFTs. However, it is found that post annealing in air is effective in improving the electrical properties of the ZT0 based TFTs. From these results, we have succeeded in fabricating ZT0 based TFTs on polyimide film substrates and ultra-thin glass substrates. The electrical field effect mobility was more than 10 cm2/Vs. Furthermore, we have tried to make ZT0 inverters and ring oscillators.

研究分野: 半導体物性

キーワード: 酸化物薄膜 フレキシブル 薄膜トランジスタ レアメタルフリー

# 様 式 C-19、F-19-1、Z-19、CK-19(共通)

# 1.研究開始当初の背景

軽量なスマートフォンやウェアラブルコンピュータを実現するために、フレキシブルディスプレイの開発が望まれている。また、少子高齢化社会の到来に伴い、バイオセンサを用いた生体診断技術の向上が求められている。これらの実現には、フレキシブル基板上に高い電界効果移動度を有する薄膜トランジスタ(TFT)を作製する事が重要となる。高電界効果移動度を有するTFTをフレキシブル基板に作製する事ができれば、高精細なフレキシブルディスプレイの実現が可能となる。また、フレキシブル基板上の高性能 TFT を有するバイオセンサを使用すれば、生体に直接貼り付ける事が可能な生体親和性の良い高感度バイオセンサの開発が可能となる。

この実現のため、低温プロセスで作製しても 10 cm²/Vs 程度の電界効果移動度を有する InGaZnO (IGZO) の研究が進められている。しかし、IGZO は、レアメタルである In や Ga を含み、安定供給に課題がある。また、In は、その毒性により一部の In 化合物が厳重な管理が必要な特定化学物質に指定されている。このため、レアメタルを含まず環境に優しい材料を用いた高性能 TFT の開発が望まれている。

我々は、レアメタルフリーで環境に負荷をかけない材料である  $Zn_2SnO_4$  (ZTO) が、室温成膜でも  $10~cm^2/Vs$  という高い Hall 移動度を示す事及び ZTO が新規の TFT チャネル材料として有望である事を見出していた。

## 2.研究の目的

高精細フレキシブルディスプレイや高感度バイオセンサに使用する薄膜トランジスタ(TFT)の開発が必要とされている。本研究では、スパッタリング法により成膜したレアメタルを含まず環境にも調和する ZTO 薄膜を用いて、高性能な TFT をフレキシブル基板上に作製する事を目的とする。

### 3.研究の方法

ZTO 及びゲート絶縁膜の成膜方法には、工業的に優れたスパッタリング法を用いる。TFT を作製する基板としては、プラスチック基板及びフレキシブルガラス基板を用いる。まず、プラスチック基板に対しては、プラスチックを変性させない低温プロセスの条件化で、ゲート電極、ゲート絶縁膜及び界面の状態が TFT 特性に与える影響を明らかにし、高性能 TFT を作製する。次に、加熱可能なフレキシブルガラス基板を使用して、ポストアニール処理が TFT 特性に与える影響を解明し、TFT のさらなる高性能化を図る予定であった。しかしながら、事前の Si 基板及び通常のガラス基板を用いた TFT の作製とその評価により、200 以上のポストアニールが重要である事がわかった。そこで、フレキシブル基板としてポリイミドと超薄板無アルカリガラスを用いて、いずれもポストアニール処理を行う事とした。

また、TFT の周波数応答特性の評価及びチャネル長が TFT 特性に与える影響を調べ、これに

より得られた結果をもとにZTOを用いたTFTによる論理 回路の設計、作製及び評価を行う予定としていた。しか し、アナログシミュレータを用いる事により、これらの 特性評価を行う事無く、論理回路を設計できる事がわか った。このため、アナログシミュレータを用いて論理回 路の設計を行い、インバーターの作製を行った。

#### 4. 研究成果

# (1) TFT 特性のゲート絶縁膜依存性

スパッタリング法により作製した ZTO を用いた TFT の特性については、不明な点が多い。そこで、ゲート電極やゲート絶縁膜の材料や膜厚、チャネル層である ZTO 膜厚等が TFT 特性に与える影響を調べた。その結果、特に、ゲート絶縁膜の膜厚が TFT 特性に大きな影響を与える事がわかった。

$p^+Si$  基板上にボトムゲート・トップコンタクト型 ZTO を用いた TFT を作製した。 $p^+Si$  基板は、ゲート電極として使用した。この  $p^+Si$  基板上に、RF マグネトロンスパッタリング法を用いて、 $SiO_2$  焼結体をターゲットとし、非加熱条件で、 $SiO_2$  ゲート絶縁膜を  $100\,$  nm から  $400\,$  nm 成膜した。その後、 $SiO_2$  ゲート絶縁膜上に RF マグネトロンスパッタリング法により、ZTO 焼結体を用い、非加熱条件で  $50\,$  nm の ZTO を成膜した。続いて、電子線蒸着法とリフトオフプロセスにより、Au/Ti によるドレインソース電極を作製した。これらの TFT 作製プロセスにおいて最高温度は  $110\,$  であった。

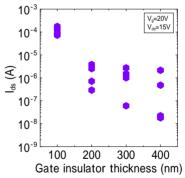

図1にドレインソース電流とゲート絶縁膜厚の関係を示す。ドレインソース電流は、理論的にはゲート絶縁膜の膜

図 1 ドレインソース電流と ゲート絶縁膜厚の関係

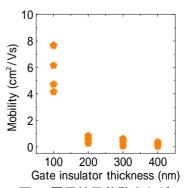

図 2 電界効果移動度とゲー ト絶縁膜厚の関係

厚に反比例するが、理論とは異なり、ゲート絶縁膜が減少すると急速に増大する事がわかった。図 2 に電界効果移動度とゲート絶縁膜厚の関係を示す。電界効果移動度もゲート絶縁膜が減少すると、急激に増加する事がわかった。この現象は、原子間力顕微鏡によるゲート絶縁膜表面の粗さや膜界面の捕獲準位の密度評価等から、ゲート絶縁膜とチャネル膜間の界面準位の存在が主たる原因である事がわかった。

ゲート絶縁膜は、その膜厚を薄くしすぎると、絶縁破壊が生じる。この事から、ZTO を用いた TFT のゲート絶縁膜は、100 nm 程度が適当である事がわかった。これらの結果を用いて、ガラス基板上に TFT を作製する際の適切な設計パラメータを決定した。

### (2) ポストアニール処理が TFT 特性に与える影響

ZTO を用いた TFT を作製する際に、チャネル層のパターンを形成するためにウェットエッチングを行うと、TFT が正常に動作しなくなるという課題があった。また、as-depo 条件では、電界効果移動度の値が大きく揺らぐという課題があった。これらの課題の解決を目的として、水蒸気等の影響を避けるため、大気組成のガスをフローする事により、厳密に温度及び雰囲気を制御した条件下で、アニール処理を行った。

作製した TFT に対し、150 、200 、250 、300 の各温度で熱処理を 60 分間行った。また、温度 200 に関しては、20 分及び 40 分のアニール処理も施した。

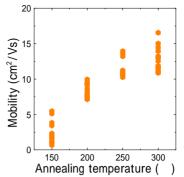

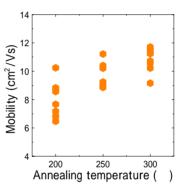

図 3 は、電界効果移動度とアニール処理温度の関係である。実験結果より、TFT 特性の改善には、アニール処理が有効である事がわかった。また、200という低温アニールでも TFT 特性は改善し、電界効果移動度は 8±2 cm²/Vs 程度と高い値を示した。アニール時間による実験から、S 値の改善のためには、60分のアニール処理時間が必要である事が判明した。さらには、窒素雰囲気や真空雰囲気のアニール実験より、TFT 特性の改善には、空気中のアニール処理が最も有効である事がわかった。

### (3) フレキシブル基板上への TFT の作製

(1)及び(2)の実験結果より、TFT 作製のための適切なパラメータやアニール処理温度等を解明した。これらの結果を基にフレキシブル基板上に TFT の作製し、その特性を評価した。

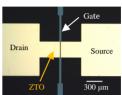

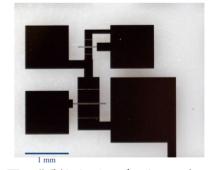

実験に用いた基板は、ポリイミド(厚さ:  $125 \mu m$ )と超薄板無アルカリガラス(厚さ:  $100 \mu m$ )である。参照試料として、厚さ 0.7 mm の無アルカリガラスにも TFT を作製した。基板上に Ti のゲート電極を作製後、RF マグネトロンスパッタリング法により、 $SiO_2$  ゲート絶縁膜及びチャネル材料である ZTO を成膜した。その後、Au/Ti のドレインソース電極を形成した。さらに、空気中で 250 、300 の条件で 1 時間熱処理を行った。図 4 にポリイミド基板上に作製したTFT の全体写真と光学顕微鏡写真を示す。図 4 より、良好に TFT が作製できている事が認められる。

図 5 にポリイミド基板上に作製した TFT の電界効

図 3 電界効果移動度と アニール温度の関係

図 4 ポリイミド基板上に作製した TFT

図 5 ポリイミド基板上に 作製した TFT の電界効果 移動度とアニール温度の 関係

図6 作製したインバーターの光 学顕微鏡写真

果移動度とアニール温度の関係を示す。ポリイミド基板上にも高い電界効果移動度を示す TFT が作製できている事がわかる。ポリイミド基板上に作製した TFT は通常のガラス基板上に作製した TFT と同程度の特性を示した。また、超薄板無アルカリガラス基板上に作製した TFT も良好に動作し、その特性はガラス基板上に作製した TFT と同程度であった。 (4) 論理回路の試作

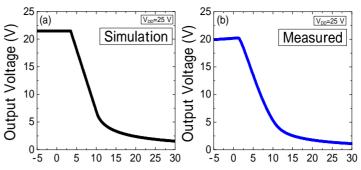

これまでの結果を基に、ZTO を用いた TFT による論理回路としてインバーター及びリングオシレーターの試作を行った。これらの論理回路の設計には、アナログシミュレータである LTspice を使用した。図 6 に作製したインバーターの光学顕微鏡写真を示す。図 6 より、インバーターは、良好に作製できている事が認められる。

図7にLTspiceを用いたインバーターのシミュレーション結果と実際に測定した特性を示す。シミュレーションは、TFT 単体のパラメータを用いて行った。図7より、インバーターはほりに動作している事がわかる。この事より、ZTOを用いたTFTを使用して、最も簡単な論理回路ではあるが、インバーターを作製できる事が認められた。

以上のように、本研究により、 レアメタルを含まず、環境に調

図 7 (a) LTspice によるインバーター特性のシミュレーション結果 (b)実際に測定したインバーターの 特性

和するZTOをチャネル材料として用いたTFTをフレキシブルエレクトロニクスに応用する際に必要な基礎データを得る事ができた。また、この結果は、より複雑な論理回路作製の一助となるものである。

# 5 . 主な発表論文等

### [雑誌論文](計3件)

- (1) Effect of post annealing on properties of ZnO-SnO<sub>2</sub> thin film transistors, <u>Kazuo Satoh</u>, <u>Shuichi Murakami</u>, <u>Yusuke Kanaoka</u>, Yoshiharu Yamada, Yoshiharu Kakehi and <u>Yoshiaki Sakurai</u>, Proceedings of the Fourteenth International Symposium on Sputtering and Plasma Processes, 查読無, 221-223 (2017).

- (2) Effect of post annealing on properties of ZnO-SnO<sub>2</sub> thin film transistors, <u>Kazuo Satoh</u>, <u>Shuichi Murakami</u>, <u>Yusuke Kanaoka</u>, Yoshiharu Yamada, Yoshiharu Kakehi and <u>Yoshiaki Sakurai</u>, J. Vac. Sci. Technol., A, 查読有, 36, 02C105 (2018). DOI: 10.1116/1.5003283

- (3) Investigation on the gate insulator thickness dependence of ZnO-SnO<sub>2</sub> thin film Transistors, <u>Kazuo Satoh</u>, Yoshiharu Yamada, <u>Yusuke Kanaoka</u>, <u>Shuichi Murakami</u>, Yoshiharu Kakehi and <u>Yoshiaki Sakurai</u>, Jpn. J. Appl. Phys., 查読有, 58, 038004 (2019). DOI: 10.7567/1347-4065/ab01f7

### [学会発表](計 10件)

- (1) 熱処理が ZnO-SnO<sub>2</sub> を用いた薄膜トランジスタ特性に与える影響,<u>佐藤 和郎</u>,<u>村上 修</u> 一,<u>金岡 祐介</u>,山田 義春,筧 芳治,<u>櫻井 芳昭</u>,応用物理学会,第77 回応用物理学 会学術講演会,14p-P10-18 (2016年9月13-16日,朱鷺メッセ,新潟県).

- (2) 熱処理が ZnO-SnO<sub>2</sub>を用いた薄膜トランジスタ特性に与える影響(II), <u>佐藤 和郎</u>, <u>村上 修一</u>, <u>金岡 祐介</u>, 中山 健吾, 山田 義春, 筧 芳治, <u>櫻井 芳昭</u>, 応用物理学会,第64回応用物理学会春季学術講演会,16p-P8-10(2017年3月14-17日,パシフィコ横浜,神奈川県).

- (3) Effect of post annealing on properties of ZnO-SnO<sub>2</sub> thin film transistors, <u>Kazuo Satoh</u>, <u>Shuichi Murakami</u>, <u>Yusuke Kanaoka</u>, Yoshiharu Yamada, Yoshiharu Kakehi and <u>Yoshiaki Sakurai</u>, The 14<sup>th</sup> International Symposium on Sputtering and Plasma Processes (ISSP2017), TF2-21p (July 5-7, 2017, Kanazawa Institute of Technology, 石川県).

- (4) 熱処理が ZnO-SnO<sub>2</sub> を用いた薄膜トランジスタ特性に与える影響(III), 佐藤 和郎, 村 上 修一, 金岡 祐介, 山田 義春, 筧 芳治, 近藤 裕佑, 櫻井 芳昭, 応用物理学会, 第 78 回応用物理学会学術講演会、&a-PA4-19(2017年3月17-20日,早稲田大学, 東京都).

- (5) Low temperature fabrication of ZnO-SnO<sub>2</sub> thin film transistors, <u>Kazuo Satoh</u>, <u>Shuichi Murakami</u>, <u>Yusuke Kanaoka</u>, Yoshiharu Yamada, Yusuke Kondo, Yoshiharu Kakehi, <u>Yoshiaki Sakurai</u> and Satoru Kaneko, 5th Nano Today Conference, P2.79 (December 6-10, 2017, Hawaii, アメリカ).

- (6) Investigation on the Gate Insulator Thickness Dependence of ZnO-SnO<sub>2</sub> Thin Film Transistors, <u>Kazuo Satoh</u>, Yoshiharu Yamada, <u>Yusuke Kanaoka</u>, <u>Shuichi Murakami</u>, Yoshiharu Kakehi, and <u>Yoshiaki Sakurai</u>, 10<sup>th</sup> Anniversary International Symposium on Advanced Plasma Science and its Applications for Nitrides and Nanomaterials (ISPlasma2018), 05P19 (March 4-8, 2018, Meijo University, 愛知県).

- (7) フレキシブル基板上に作製した  $ZnO-SnO_2$  薄膜トランジスタの特性, <u>佐藤</u> 和郎, <u>村上修一</u>, <u>金岡 祐介</u>, 山田 義春, 筧 芳治, 近藤 裕佑, <u>櫻井 芳昭</u>, 応用物理学会, 第 79回応用物理学会学術講演会, 19p-PB8-6(2018 年 9 月 18-21 日, 名古屋国際会議場, 愛知県).

- (8) レアメタルフリー材料 ZnO-SnO<sub>2</sub> を用いた薄膜トランジスタ, <u>佐藤 和郎</u>, センサエキ スポジャパン 2018 (2018 年 9 月 26-29, 東京ビッグサイト, 東京都)

- (9) スパッタリング法により作製した ZnO-SnO<sub>2</sub> を用いた薄膜トランジスタの熱処理効果, 佐藤 和郎,村上修一,金岡 祐介,山田 義春,筧 芳治,近藤 裕佑,<u>櫻井 芳昭</u>,2018 年日本表面真空学会学術講演会,1P39(2018年11月19-21日,神戸国際会議場,兵庫 県).

- (10) Characteristics of ZnO-SnO<sub>2</sub> Thin Film Transistors on Flexible Substrates, <u>Kazuo Satoh</u>, <u>Shuichi Murakami</u>, <u>Yusuke Kanaoka</u>, Yoshiharu Yamada, Yoshiharu Kakehi, Yusuke Kondo and <u>Yoshiaki Sakurai</u>, 11<sup>th</sup> International Symposium on Advanced Plasma Science and its Applications for Nitrides and Nanomaterials (ISPlasma2019), 18P1-38 (March 17-21, 2019, Nagoya Institute of Technology, 愛知県).

### [その他]

ホームページ等

https://orist.jp/kenkyu-bu/denshi-kikai/

6 . 研究組織

(1)研究分担者

研究分担者氏名: 櫻井 芳昭

ローマ字氏名: SAKURAI, Yoshiaki

所属研究機関名:地方独立行政法人大阪産業技術研究所

職名:総括研究員

研究者番号(8桁):50359387

研究分担者氏名:村上 修一

ローマ字氏名: MURAKAMI, Shuichi

所属研究機関名:地方独立行政法人大阪産業技術研究所

部局名:電子・機械システム研究部

職名:主幹研究員

研究者番号(8桁):70359420

研究分担者氏名:金岡 祐介

ローマ字氏名: KANAOKA, Yusuke

所属研究機関名:地方独立行政法人大阪産業技術研究所

部局名:電子・機械システム研究部

職名:主任研究員

研究者番号(8桁):60443537

(2)研究協力者

研究協力者氏名: 筧 芳治

ローマ字氏名: KAKEHI, Yoshiharu

所属研究機関名:地方独立行政法人大阪産業技術研究所

部局名:電子・機械システム研究部

職名:主任研究員

研究者番号(8桁):90359406

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等については、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。