#### 研究成果報告書 科学研究費助成事業

今和 3 年 1 0 月 1 8 日現在

機関番号: 17102

研究種目: 挑戦的萌芽研究 研究期間: 2016~2018

課題番号: 16K13720

研究課題名(和文)革新的塗布型新太陽電池の研究

研究課題名(英文) Innovative paste-type solar cell

研究代表者

加藤 喜峰 (Kato, Yoshimine)

九州大学・工学研究院・准教授

研究者番号:60380573

交付決定額(研究期間全体):(直接経費) 2.900.000円

研究成果の概要(和文): シリコン(Si)微結晶粒子ペーストの作製し、塗布することで安価な太陽電池を製造するための基礎プロセスの構築を行った。Si酸化を防ぐために還元性溶媒中と不活性ガス中でミリングを行うことにより、購入したFTIR装置で酸化を抑えられることが確認できた。高純度Si原料を遊星ボールミリングによりナノサイズ化しペースト状にした後、安価な金属基板などにp型、n型Siペーストをそれぞれ塗布し、不活性ガス中で熱処理後、pn接合太陽電池を製作した。良好なダイオード特性が得られ、わずかではあるが光起電力も得られた。本研究により、Siペースト塗布法でも電子デバイスを製作できる可能性があることが示唆された。

研究成果の学術的意義や社会的意義 Siペースト塗布法によるpn-接合の製作に成功し、Si塗布型太陽電池を作成できる可能性を示すことが出来た。Siは非常に酸化しやすい物質であり、Siペースト塗布によるデバイスの製造は半導体では常識はずれであり困難なプロセスである。本研究でSi粒子などの酸化防止手法を見出し、デバイスとしての応用が見出せる結果が得られた。まだ、効率の高い太陽電池は出来ていないが、今後、塗布法でSiなどの安価な材料でSCが製造できるようになれば、価格が劇的に安くなり、固定価格買取制度無しでも未来のエネルギー源としての SCが世の中に普及することは間違いない。

研究成果の概要(英文): Single crystalline-Si based solar cell is still expensive due to cost of growing Si crystal and considerable waste during sawing Si ingots. In order to reduce the cost of Si crystal growth, we propose a method of making Si pastes from Si ploly-crstalline chips.

p- and n-type Si pastes were prepared in a way by utilizing a planetary ball miller to pulverize

Si source material. pn homojunction was formed by coating Si pastes onto metal substrates,

followed by annealing under Ar atmosphere. The optimal annealing temperature was found to be around

1050 °C that exhibits the lowest resistivity. A typical rectifying property of diode with small

photovoltaic was observed for the device fabricated. It is anticipated that Si pastes could have potential for low cost device fabrication such as solar cells. All Cz Si ingot growth procedures could be skipped, consequently it is expected that the manufacturing cost for solar cell can be greatly reduced.

研究分野: 自然科学、半導体デバイス・物性、超音波ガス検知

キーワード: 太陽電池 シリコン微結晶 ペースト 遊星ボールミル

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

# 1.研究開始当初の背景

太陽光発電(SC)の固定価格買取制度の価格は年々下がっており、SC 普及にブレーキがかかって来ている。原発事故以来、我が国は新しいエネルギーの道を切り開く必要性が出てきた。国内のエネルギー問題の解決手段の一つとして SC の普及が最も近道であると考えるが、日本の国際的シェアが 6%まで下がってきている。日本が再びSCのシェアを勝ち取るためには、コストを劇的に下げる革新的プロセス技術の研究開発が急務である。SCの製造工程で最も安く作れる例の一つは、CdS / CdTe SC(7万円/kW)などに代表されるように材料をペースト状にして塗布する方法である。シリコン(Si)単結晶インゴットを作る前工程の安価な高純度多結晶Si原材料を微結晶粒化し、ペースト状にしてSC製造に応用できれば、 $1m^2$ 当たり、Si原料はわずか約 10 C C で足りることになる。また、真空装置等に比べるとミリング装置等はその 20 ~ 30 分の 1 のコストで済み、少な目に見積もっても、現在のSiSСの 10 分の 1 以下のコストで製造できると考えられる。

#### 2.研究の目的

将来、固定価格買取制度が無くても太陽光発電(SC)を普及させるため、製造コストを劇的に下げることを目的とする。Si単結晶製造プロセスや高価な真空装置などを用いずに、CdS/CdTe 塗布型 SC などに代表されるように安価なSi原料などのペーストを安価な基板に塗布してSCを製造する方法の研究開発を行う。本研究では第一歩として塗布型 SiSC製造プロセスに関する基礎研究を行う。具体的には、高純度多結晶Si原料をミリングなどにより微細化しペースト状にした後、安価な基板などにSiペーストを塗布し、pn接合薄膜 SiSCを製作する。Siは酸化しやすい材料であり、粉砕後に塗布して熱焼成処理を行う際に、Siの酸化を防ぐようにすることが最重要課題である。

#### 3. 研究の方法

<u>Si酸化防止手法の確立</u> Siミリング中の還元性溶媒やアニール温度・ガス雰囲気など 最適化を行う。プロセスを脱酸素・脱水分のグローブボックス内で行えるように準備し、 最も酸化されやすいプロセス工程をフーリエ変換赤外分光光度計(FTIR)や表面分析などで 定量・解析し改善する。

<u>密着性、基板コーティングの最適化</u> プレス法を用いてペーストの密着性向上を図る。 また、金属基板の金属原子がSi微結晶粒子ペーストに拡散して、悪影響を与えないよう にコーティング材料の最適化や電気特性の向上図る。

<u>SCの製作</u>整流特性・光起電力特性などを計測し、温度や還元処理法、SC製造方法の 最適化を目指す。

# 4. 研究成果

# 1. Si微結晶粒子ペーストの固着法

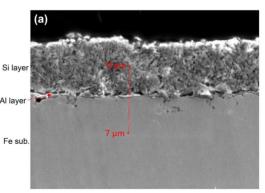

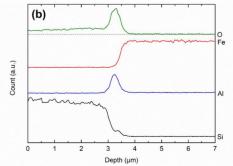

Si微結晶粒子ペーストを基板に塗布するだけだと、密着性に問題が生じる。そこで、本研究ではプレス法を用いて、Si微結晶粒子を金属基板に固着させる手法を試みた。その結果、528 MPa の圧力にてスコッチテープ法等でもはがれない膜が製作できた。図1(a)はプレス後のSi膜の断面SEM写真であり、膜が40%までに押しつぶされ緻密になっている様子が分かる。また、超音波を用いて、プレスしながら粒子を金属基板に固着させる手法は意外に難しく、振動の方向では逆に剥がれてしまうことが分かり、現在、装置の改良を行っている。

# 2. 金属基板・コーティング材の最適化

安く頑強に作るために例えば鋼板などの基板 を選択できるが、通常、金属基板からは不純物 となる金属イオンが半導体に拡散して、デバイ スを作ることが困難である。そこで、基板の高 純度化や基板からの不純物拡散を防止する障壁 層などが必要となる。基板の高純度化にはコス トがかかることから、本研究では安価な鉄板な どに高純度金属のコーティングを試みた。拡散

図 1. (a) AI コーティングした鉄基 板上に塗布した Si ペースト膜の断面 SEM 写真。(b) (a)に示した赤線上の EDX 線分析結果。

の少ない金属材料として高純度のA1(99.999%)のスパッタコーティングを試みた。A1はSiに対してp型のドーピング材料となる上、Siに対して還元作用を持つことから選択した。図1(b)のEDX線分析から分かるように、FeはSi膜には拡散していなく、またSi層とFe基板の境界にはAIがと酸素が存在し、酸化アルミとなっており、Siの酸化が抑えられている事が分かった。

# 3. 還元熱処理プロセスと太陽電池の製作

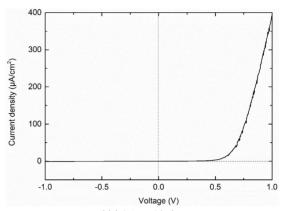

p型、n型Siペーストをそれぞれ Mo 基板に塗布し、脱酸素・脱水分した高純度Arガスを 0.5L/min 流した電気炉内で熱処理した。1050 、30分加熱において Si 膜の抵抗が5 と最も低くなり、その条件で pn 接合を製作した。図 2 に示すように、良好なダイオード特性が得られた。理論曲線とフィティングさせた結果、整流比が 440、理想因子が 3.45、直列抵抗が100 と言う値が得られた。また、わずかであるが光起電力も確認できた。

図2. Mo基板上に塗布したSiペース ト pn 接合の I-V 特性。

# [今後の展開]

- 1. FTIR で観測すると脱酸素・脱水分した高純度 A r ガス中でアニールしても Si 微粒子 は時間と共に酸化してしまう。しかし、極短時間で加熱すれば酸化を最小限に抑える ことができるかどうかを確認する。

- 2. 金属基板を用いると Si との熱膨張率の違いが大きいため膜が剥がれやすくなる。室温で Si の膨張係数は 2.4x10<sup>-6</sup> /K であるのに対して、それに近い導電性基板材料としてはグラファイト、タングステン、モリブテンなどが 4x10<sup>-6</sup> /K 台で有る。コスト面から考えるとグラファイトが安価なので、今後この基板を使用して検討していきたい。

- 3. Ti 等の金属は酸化 Si 等を還元できる特性を有しているため、Ti を用いた熱処理法なども今後試す予定である。

# 5. 主な発表論文等

### [雑誌論文](計6件)

- ( $\mathcal{P}$ ) Yan Li, Hiroshi Inokuchi, Takahiro Orita, Kunihiko Maejima, Kensuke Nakashima, Satoshi Ooue, Hiroshige Matsumoto, <u>Yoshimine Kato</u>, "pn junction formation by Si paste coated on metal substrates", J. Materials Science: Materials in Electronics, 2019, pp. 1-8. DOI: 10.1007/s10854-019-00980-3.

- (1) Yan Li and Y. Kato, "Removal of oxides and surface texturization of crystalline Si wafer by ion beam etching", DEStech Transactions on Computer Science and Engineering, 2019, pp.510-515. DOI: 10.12783/dtcse/ccme2018/28659.

- (ウ) Huan Zhu, Morihiro Sakamoto, Ting Pan, Takaya Fujisaki, Hiroshige Matsumoto, Kungen Teii, <u>Yoshimine Kato</u>, "Rapid Thermal Annealing of Si paste film and pn-junction formation", Nanotechnology **31**, p.385202(10pp) (2020). DOI: 10.1088/1361-6528/ab9aed, 38,

- (工) Yusuke Kuboki, Huan Zhu, Morihiro Sakamoto, Hiroshige Matsumoto, Kungen Teii, <u>Yoshimine Kato</u>, "Low temperature annealing of Si micro-crystal paste for pn junction formation", Materials Science in Semiconductor Processing **135**, pp.106093-7 (2021). DOI: 10.1016/j.mssp.2021.106093

- (才) Huan Zhu, Yusuke Kuboki, Morihiro Sakamoto, <u>Yoshimine Kato</u>, "Effect of Low Temperature Annealing on pn Junction Formation using Si Paste", Proc. of 2021 5<sup>th</sup> IEEE Electron Devices Technology and Manufacturing (EDTM 2021), pp.10-12, IEEE Xplore (2021). DOI: 10.1109/EDTM50988.2021.9420845.

- (力) Huan Zhu, Ting Pan, Ryo Sato, Lusato Majula, Kwati Leonard, Hiroshige Matsumoto, <u>Yoshimine Kato</u>, TiO2/p-Si Paste Heterojunction Fabricated by Rapid Thermal Annealing, Applied Surface Science **569**, 151003, pp.1-9 (2021). DOI: 10.1016/j.apsusc.2021.151003

# [学会発表](計6件)

Yan Li, <u>Yoshimine Kato</u>, "Removal of oxides and surface texturization of crystalline Si wafer by ion beam etching", 2018 International Conference on

Power, Energy and Materials Engineering (PEME2018), 2018.

Yan Li, <u>Yoshimine Kato</u>, "pn junction formation by Si paste coated on metal substrates", 九州大学エネルギーウィーク 2019, 2019.1.

Huan Zhu, Yusuke Kuboki, Morihiro Sakamoto, Hiroshige Matsumoto, <u>Yoshimine Kato</u>, "Low temperature annealing of Si paste and fabrication of pn junction", TACT 2019 International Thin Films Conference, 2019.11. (優秀ポスター章受章) Ting Pan, Zhu Huan, Morihiro Sakamoto, Hiroshige Matsumoto, <u>Yoshimine Kato</u>, Effect of rapid thermal annealing on fabricating pn-junction device by Si paste, 九州大学エネルギーウィーク 2020, 2020.1.

Ting Pan, Huan Zhu, 佐藤 凌, <u>加藤</u> 喜峰, 熱処理中の Ti 膜の Si ペースト酸化に及ぼす影響, 令和 2 年度 応用物理学会九州支部学術講演会, 2020.11.

Huan Zhu, Yusuke Kuboki, Morihiro Sakamoto, <u>Yoshimine Kato</u>, "Effect of Low Temperature Annealing on pn Junction Formation Using Si Paste", 2021 5<sup>th</sup> IEEE Electron Devices Technology and Manufacturing (EDTM) Conference, 2021.4.

# [図書](計0件)

# [産業財産権]

出願状況(計0件)

名称: 発明者: 種類: 種号: 番頭内外の別:

取得状況(計0件)

名称: 発明者: 権利者: 種類: 番号: ま得の別:

〔その他〕

ホームページ等

http://www.kato-lab.org/content

- 6.研究組織

- (1)研究分担者

研究分担者氏名:

ローマ字氏名:

所属研究機関名:

部局名:

職名:

研究者番号(8桁):

(2)研究協力者

研究協力者氏名:松本広重、田中悟、堤井君元、大上悟、中野博昭

ローマ字氏名: Hiroshige Matsumoto, Satoru Tanaka, Kungen Teii, Satoru Ooue, Hiroaki Nakano

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等については、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。