# 科学研究費助成事業 研究成果報告書

令和 元年 5月24日現在

機関番号: 11301

研究種目: 基盤研究(C)(特設分野研究)

研究期間: 2016~2018 課題番号: 16KT0187

研究課題名(和文)完全自律誤り訂正VLSI設計技術の構築と脳型LSIシステムへの応用展開

研究課題名(英文)Development of fully autonomous error-correctable VLSI design technology and its application to brain-inspired LSI system

### 研究代表者

夏井 雅典(NATSUI, Masanori)

東北大学・電気通信研究所・准教授

研究者番号:10402661

交付決定額(研究期間全体):(直接経費) 3,600,000円

研究成果の概要(和文):本研究では,従来のように「設計時に動作マージンを確保」するのではなく,「設計後における特性バラつきに応じて回路動作点を調整」することを前提としたポストプロセス指向設計技術の実現を目的とし,半導体素子技術とスピントロニクス技術の融合によって上記機能をコンパクトに実装する高性能・高信頼次世代VLSIについて検討した.具体的には,従来の静的な補償だけでなく,時々刻々と変わる環境に応じて動的かつ自律的にその構造および動作を変化する性質,すなわち生物の脳における「知的環境適応性(可塑性)」を有する次世代VLSI実現のための基盤技術の確立に向けた研究を推進した.

研究成果の学術的意義や社会的意義本研究成果を基盤とする設計技術により,高い性能が得られる可能性を有しつつも微細プロセスの高バラつき条件下においては実用に耐えないとされてきた様々な回路設計技術を,高性能VLSI実現の手段の一つとして再び活用できるようになる.これは設計における適用技術の選択肢を広げ,高性能VLSIの実現をより容易にすることにもつながる.すなわち,本技術は,単にバラつきの影響を抑え,回路性能を保証するためだけの技術ではなく,最先端プロセスが有する性能を設計者が最大限に活用できる環境を与え,従来技術では成し得ない十分な柔軟性・信頼性を有するVLSIをより容易に設計可能にする重要な技術といえる.

研究成果の概要(英文): In this research, we conducted the research toward the realization of post-process oriented design technology which is based on the concept of adjusting the circuit operating point according to the process variation effect occurred after fabrication, instead of the conventional approach of assigning sufficient operation margin. As a concrete approach, we conducted the design of high-performance and highly-reliable next-generation VLSI that implements the above functions compactly by combining semiconductor device technology and spintronics device technology. Specifically, we promoted research toward establishing a design technology for the realization of next-generation VLSI with plasticity, which has the property of changing its structure and operation dynamically and autonomously in response to the operation environment.

研究分野: 集積回路設計技術

キーワード: 集積回路 LSI設計技術 ディペンダブルコンピューティング 誤り訂正技術 最適化アルゴリズム

# 様 式 C-19、F-19-1、Z-19、CK-19(共通)

## 1.研究開始当初の背景

CMOS 素子の極限的微細化にともない,動作時の信頼性を如何に確保するかが集積回路設計における主要なボトルネックになりつつある。ムーアの法則に基づくスケーリングによる性能向上を継続するために,Ge あるいは III-V 属化合物半導体のようなポスト Si 材料・素子技術,およびそれらを用いたメモリ・論理回路技術の導入等が進んでいるが,それらが信頼性に与える影響はいまだ未知数であるだけでなく,新たな故障メカニズムを発生させてしまう可能性も示唆されている。信頼性に関する検討がまだ十分とはいえないまま,これら新技術の市場への導入が着々と進められている一方,市場においては常に高い信頼性が求められる。

航空宇宙システムや自動車,医療機器といった高い信頼性を要求される分野においては,最先端のプロセス技術ではなく,信頼性のデータが充実している熟成したプロセス技術を使用して半導体チップを製造する場合が多い.一方,スパコンなどに代表される高性能コンピューティング分野においては,最先端プロセス技術による最高性能の半導体チップを用いつつ,非常に高い信頼性を要求するシステムの実現が求められる.その結果,信頼性が未知の素子を組み合わせて高信頼なシステムを構築するという難題を設計者に課すこととなり,その信頼性確保は今後ますます困難になっていくと予想される.

以上述べたように,近年の技術動向をふまえると,従来のいわゆるワーストケース設計,すなわち,想定されるあらゆる動作条件における信頼性を設計時に保証しようとする設計手法に基づいて十分な性能を有するシステムを構築することが事実上不可能になることは想像に難くなく,概念そのものを根本から変えた新しい設計手法の確立が急務となる.

### 2.研究の目的

以上に示したような集積回路設計の分野全体に広がるある種の閉塞感を打破するためには,従来の CMOS ベース技術に囚われない回路アーキテクチャ,ならびにデバイス・回路・システムレベルからの総合的なアプローチによる高信頼化技術を組み合わせることによる,高性能・高信頼 VLSI の可能性を探求することが重要である.これをふまえ,本研究では,従来のように「設計時に動作マージンを確保」するのではなく,「設計後における特性バラつきに応じて回路動作点を調整」することを前提としたポストプロセス指向設計技術の実現を目的とし,半導体素子技術とスピントロニクス技術の融合によって上記機能をコンパクトに実装する高性能・高信頼次世代 VLSI について検討する.具体的には,設計対象を「時々刻々と変化する複雑系システム」と見なし,以下の2項目について研究を行う:

- (1)動作点補正機能を有する半導体/スピントロニクス素子混載回路システム

- (2)最適な動作点を探索する最適化アルゴリズム

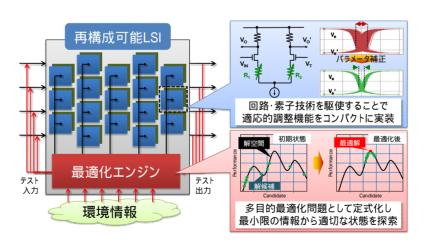

これらの技術を統合し,内乱・外乱の影響を設計後に全て許容・吸収可能なシステムを構築するというアプローチにより,従来の静的な補償だけでなく,時々刻々と変わる環境に応じて動的かつ自律的にその構造および動作を変化する性質,すなわち生物の脳における「知的環境適応性(可塑性)」を有する次世代 VLSI 実現のための基盤技術を確立する.本研究が目標とする知的環境適応型次世代 LSI の基本アーキテクチャを図 1 に示す.

図1.本研究が目標とする知的環境適応型次世代 LSI の基本アーキテクチャ

### 3.研究の方法

研究の第一段階として,小規模回路ブロックを用いた基礎実験を行い,その結果に基づき,本研究の目標である環境適応型新概念 LSI 設計技術の基本仕様を検討する.加えて,本研究者がこれまで研究を進めてきた不揮発記憶素子ベース低電力論理集積回路技術ならびにポストプロセスバラつき補正技術を元に,センサからの時系列入力情報を内部に蓄積することで,動作環境に即した適切な処理へと機能を変化させる環境適応型 LSI の基本アーキテクチャを策定す

る、研究の第二段階では、策定した基本仕様を元に、そのさらなる高度化とハードウェアへの 実装について検討を行う、計算機シミュレーションを元に提案アーキテクチャの改善を施した 上で、プログラマブル LSI (FPGA)上への実装を前提とした設計とその動作検証を行う、その 検証結果から得られる知見をもとに問題点の洗出しおよび高度化の検討を行った上で、最終年 度にハードウェア実装を行い、その有効性実証、ならびに全体成果の取りまとめを行う、

各研究項目の具体的な進め方について,以下に示す.

### · 再構成可能 LSI 設計技術

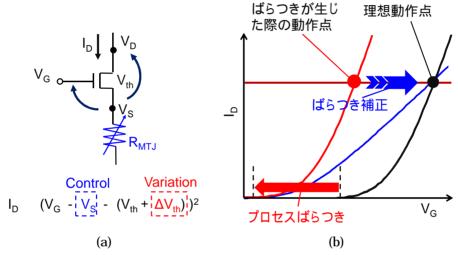

本研究者は、LSI に不揮発性可変抵抗素子を内蔵することにより、LSI の高信頼性と回路本来の高性能性・低消費電力性の両立を実現する設計技術について研究を進めてきた 本研究では、まず、より柔軟な再構成を可能とする回路設計技術について検討を行う、提案する基本回路構造(図2)の特性を評価するとともに、本構造を基本要素とする再構成可能 LSI について性能評価を行う、これに加え、提案する再構成回路構造の状態変化および状態保持に要する消費電力の削減技術についても検討を行う。

以上の初期検討を通して得られた知見を元に,再構成可能 LSI の性能向上を目的とした高度化を図る.提案する回路アーキテクチャに基づき,脳の情報処理過程における学習・記憶,超並列,自律分散といった様々な原理に基づく柔軟かつ複雑な処理をハードウェアアルゴリズムとして実装することにより,高次の環境適応処理を極めてコンパクトなシステム構成で実現することを目指す.特に本研究においては,脳の可塑性(環境適応性)と呼ばれる機能にヒントを得 従来の延長上にない環境適応型新概念 LSI 設計技術の基盤技術の確立を到達目標とする.

図 2.可変抵抗素子を用いたバラつき補正技術:(a) 基本回路構造,(b)バラつき補正の様子.本来の理想的な特性( )がプロセスバラつきによってシフト( )し,動作点が変化してしまった際,抵抗素子の抵抗値を調整することで動作点を理想の値に補正( )することが可能.

# ・最適化アルゴリズム

上記技術によって実現される再構 可能 LSI において,入出力仕様および環境情報を元に適切ためのアルズムに適けためのアルズムについて検討する.オンチップ可したり,アルゴリズムの実装価を行ったもに,アルゴリズムの実評価を行ったもに,ニューラルネットワークをよび表達に内包することで,入力をよにのと代路環がによいで検討を行う.

# 常にストライクゾーンで動作 良 条件C 条件B 条件A

条件に応じた最適値を適応的に選択

**従来** 全条件を保証する固定値を設計時に選択 条件によって性能ロス

設計値

図3.内部状態の調整によるパフォーマンス向上

・研究を遂行するための研究体制につ いて 本申請者が主体的に研究の遂行および全体の統括を行うとともに,1~2名の大学院生とともに具体的なシステムの実装,データ整理,検討等を行う.評価環境は,本研究費で整備する評価用 WS上に構築する.また,集積回路設計とその性能評価に関しては,東京大学大規模集積システム設計教育研究センター(VDEC)より提供される EDA ツールを使用して実施する.

### 4. 研究成果

## ・素子の確率的動作を考慮した LSI 設計技術

LSI に内蔵された不揮発性可変抵抗素子の確率的動作を考慮することで LSI の高信頼性と回路本来の高性能性・低消費電力性の両立を実現する設計技術について研究を行った.可変抵抗素子に対する書込が成功したか否かではなく,LSI として所望の演算が行われるかどうかを判断基準としたエラーマスキング処理を採用することにより,可変抵抗素子に要求する歩留まりを大きく緩和でき,結果としてLSI の低電力動作が達成できることを証明した.

また,メモリ〜プロセッサ間のボトルネックを緩和する回路技術の導入により,不揮発性可変抵抗素子の確率的動作がLSI全体の性能に与える影響を緩和し,結果としてLSIの低電力・高性能動作が達成できることを証明した.

### ・時系列特徴を活用した高信頼化アルゴリズム

マイクロプロセッサ内のデータ転送におけるソフトエラーを対象とした,脳型計算に基づく 訂正技術について検討を行い,その有効性を確認した.従来型のデータ表現に基づくボトムア ップ手法(BCH 符号など)に対し,転送データの時系列特徴に基づき,トップダウンでエラー 訂正を行う手法を提案し,集積回路におけるメモリ・プロセッサ間のデータ転送に対して本手 法を適用することにより,冗長化に伴う転送データ量の増加をもたらすことなく訂正性能の向 上が可能であることを示した.さらに,従来手法とのハイブリッド構造を新たに提案すること で,訂正性能のさらなる向上に成功した.

本手法の応用として,車載ネットワーク向け不正侵入検出技術の実現に向けた基本アルゴリズムについても研究を行った.不正侵入による攻撃の代表例であるパケット飽和攻撃及びパケット改変攻撃の双方に対して,従来手法を超える識別性能が達成可能であることを確認した.車載ネットワークにおける代表的な攻撃シナリオを設定し,実車から得られたネットワークデータに攻撃パターンを付加したものを対象として,複数の攻撃パターンを単一のアルゴリズムで検出可能であることを示した.

## ・LSI 設計

不揮発記憶素子の活用により,対象とする演算処理に応じて動作を変化させるアクセラレータを組み込むことによるセンサノード向け低消費電力 LSI の実現可能性について示した。また,量子化ニューラルネットワークアルゴリズムのハードウェア実装のための要素回路についても合わせて検討を行うなど,具体的応用例の開発を通して,本研究がもたらすインパクトを実証した.

### 5 . 主な発表論文等

[雑誌論文](計 5 件)

- 1. <u>M. Natsui</u>, T. Chiba and T. Hanyu, "Design of an Energy-Efficient XNOR Gate Based on MTJ-Based Nonvolatile Logic-in-Memory Architecture for Binary Neural Network Hardware," Japanese Journal of Applied Physics, Vol.58, No.SB, pp.SBBB01-1-SBBB01-7, 2019. DOI: 10.7567/1347-4065/aafb4d(查読有)

- 2. <u>M. Natsui</u>, T. Chiba and T. Hanyu, "Design of MTJ-Based Nonvolatile Logic Gates for Quantized Neural Networks," Microelectronics Journal, Vol.82, pp.13-21, 2018. DOI: 10.1016/j.mejo.2018.10.005(査読有)

- 3. M. Natsui and T. Hanyu, "Design of a memory-access controller with 3.71-times-enhanced energy efficiency for Internet-of-Things-oriented nonvolatile microcontroller unit," Japanese Journal of Applied Physics, Vol.57, No.4s, pp.04FN03-1-04FN03-5, 2018. DOI: 10.7567/JJAP.57.04FN03(査読有)

- 4. D. Suzuki, <u>M. Natsui</u>, A. Mochizuki, S. Ikeda, T. Endoh, H. Ohno, and T. Hanyu, "Design of a Variation-Resilient Single-Ended Nonvolatile 6-Input Lookup Table Circuit with a Redundant-MTJ-Based Active Load for Smart IoT Applications," IET Electronics Letters, Vol.53, No.7, pp.456-458, 2017. DOI: 10.1049/el.2016.4233(査読有)

- 5. M. Natsui, A. Tamakoshi, T. Endoh, H. Ohno, and T. Hanyu, "Fabrication of an MTJ-Based

Nonvolatile Logic-in-Memory LSI with Content-Aware Write Error Masking Scheme Achieving 92% Storage Capacity and 79% Power Reduction, "Japanese Journal of Applied Physics, Vol.56, No.4S, pp.04CN01-1-04CN01-5, 2017. DOI: 10.7567/JJAP.56.04CN01 (査読有)

## [学会発表](計 26 件)

- 1. <u>M. Natsui</u>, D. Suzuki, A. Tamakoshi, H. Sato, S. Ikeda, T. Endoh, and T. Hanyu, "Impact of MTJ-Based Nonvolatile Microcontroller LSI for IoT Applications," 5th CIES Technology Forum / DAY 1 International Symposium March 2019. (invited)

- 2. <u>M. Natsui</u>, T. Chiba and T. Hanyu, "MTJ-Based Nonvolatile Logic Gates for Quantized Neural Network Hardware," The 6th International Symposium on Brainware LSI March 2019.

- 3. <u>M. Natsui</u>, "An FPGA-Accelerated Fully Nonvolatile Microcontroller Unit for Sensor-Node Applications in 40nm CMOS/MTJHybrid Technology Achieving 47.14 μ W Operation at 200MHz," IEEE SSCS Kansai Chapter Technical Seminar 2019年3月. (招待)

- 4. M. Natsui, D. Suzuki, A. Tamakoshi, T. Watanabe, H. Honjo, H. Koike, T. Nasuno, Y. Ma, T. Tanigawa, Y. Noguchi, M. Yasuhira, H. Sato, S. Ikeda, H. Ohno, T. Endoh, and T. Hanyu, "An FPGA-Accelerated Fully Nonvolatile Microcontroller Unit for Sensor-Node Applications in 40nm CMOS/MTJHybrid Technology Achieving 47.14 μ W Operation at 200MHz," 2019 IEEE International Solid-State Circuits Conference (ISSCC2019), pp.202-203, February 2019.

- 5. 千葉智貴,<u>夏井雅典</u>,羽生貴弘,"MTJベースばらつき補正機能を用いた2値化ニューラルネットワーク向け低消費電力・省面積 bitcount 回路の構成," 第 32 回多値論理とその応用研究会,pp.100-105,2019年1月.

- 6. <u>M. Natsui</u>, T. Chiba and T. Hanyu, "MTJ-Based Nonvolatile Ternary Logic Gate for Quantized Convolutional Neural Networks," IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference, 2 pages, October 2018.

- 7. M. Natsui, T. Chiba and T. Hanyu, "MTJ-Based Nonvolatile Logic Gate for Binarized Convolutional Neural Networks and Its Impact," Extended Abstracts of 2018 International Conference on Solid State Devices and Materials (SSDM2018), pp.109-110, September 2018.

- 8. 千葉智貴,<u>夏井雅典</u>,羽生貴弘,"不揮発量子化ニューラルネットワーク構造に基づく小型・超低消費電力 XNOR 回路の構成,"平成30年度電気関係学会東北支部連合大会,p. 1E17,2018年8月.

- 9. H. Suda, M. Natsui, and T. Hanyu, "Systematic Intrusion Detection Technique for In-Vehicle Network Based on Time-Series Feature Extraction," 48th IEEE International Symposium on Multiple-Valued Logic (ISMVL2018), pp.56-61, May 2018.

- 10. <u>夏井雅典</u>, 羽生貴弘, "次世代 IoT 社会に向けた脳型 LSI 設計技術," 2018 年電子情報通信 学会総合大会 2018 年 3 月. (招待)

- 11. <u>M. Natsui</u>, T. Endoh, H. Ohno, and T. Hanyu, "MTJ-Based Nonvolatile Logic LSI for Ultra Low-Power and Highly Dependable Computing," China Semiconductor Technology International Conference (CSTIC), p. 1-54, March 2018. (invited)

- 12. <u>M. Natsui</u>, H. Suda and T. Hanyu, "Data-Stream-Aware Computing for Highly Dependable VLSI Systems," The 5th International Symposium on Brainware LSI, p. 8, February 2018.

- 13. 須田拓樹,<u>夏井雅典</u>,羽生貴弘,"脳型計算に基づく非シグネチャ不正侵入検出手法,"第 31回多値論理とその応用研究会,pp.51-56,2018年1月.

- 14. 加藤健太郎, <u>夏井雅典</u>, 羽生貴弘, "時系列特徴を用いたチップ内データ転送エラー訂正手法とその可能性," デザインガイア 2017 -VLSI 設計の新しい大地- 2017 年 11 月.

- 15. <u>M. Natsui</u> and T. Hanyu, "Energy-Efficient Data-Access Technique for an Ultra Low-Power Nonvolatile Microcontroller Unit," 3rd ImPACT International Symposium on Spintronic Memory, Circuit and Storage, p. 57, September 2017.

- 16. M. Natsui and T. Hanyu, "Energy-Efficient High-Performance Nonvolatile VLSI Processor with a Temporary-Data Reuse Technique," Extended Abstracts of 2017 International Conference on Solid State Devices and Materials (SSDM2017), pp.977-978, September 2017.

- 17. <u>夏井雅典</u>,須田拓樹,羽生貴弘,"時系列特徴を用いた脳型計算ベース車載ネットワーク セキュリティ技術,"多値論理研究ノート,pp.12-1-12-5,2017年9月.

- 18. <u>夏井雅典</u>, "脳型 LSI を拓く集積回路・アーキテクチャの展望," VLSI 夏の学校「LSI 技術者のための人工知能基礎講座」 2017 年 8 月. (招待)

- 19. 須田拓樹, <u>夏井雅典</u>, 羽生貴弘, "脳型計算に基づく車載ネットワークの不正侵入検出法," 平成 29 年度電気関係学会東北支部連合大会, p. 1E02, 2017 年 8 月.

- 20. 須田拓樹,<u>夏井雅典</u>,羽生貴弘,"時系列特徴を考慮した脳型計算ベース車載ネットワークセキュリティ技術に関する基礎的検討,"LSIとシステムのワークショップ 2017 2017 年5月.

- 21. <u>M. Natsui</u>, N. Sugaya, and T.Hanyu, "Brain-Inspired Computing for Error-Resilient VLSI System," The 4th International Symposium on Brainware LSI, p. 2, February 2017.

- 22. <u>M. Natsui</u>, T. Endoh, H. Ohno, and T. Hanyu, "Towards Ultra Low-Power and Highly Dependable VLSI Computing Based on MTJ-Based Nonvolatile Logic-in-Memory Architecture," BIT's 6th Annual World Congress of Nano Science & Technology 2016, p. 358, October 2016. (invited)

- 23. 加藤健太郎,<u>夏井雅典</u>,羽生貴弘,"適切な通信ネットワークのトラフィックを考慮した 高機能・低コストエッジプロセッサの構成に関する一考察,"第 30 回多値論理とその応用 研究会,pp.72-76,2017年1月.

- 24. M. Natsui, A. Tamakoshi, T. Endoh, H. Ohno, and T. Hanyu, "Design of an MTJ-Based Nonvolatile LSI for Energy-Efficient Microcontroller Unit," 2nd ImPACT International Symposium on Spintronic Memory, Circuit and Storage, p. 68, September 2016.

- 25. M. Natsui, A. Tamakoshi, T. Endoh, H. Ohno, and T. Hanyu, "Highly Reliable MTJ-Based Nonvolatile Logic-in-Memory LSI with Content-Aware Write Error Masking Scheme," Extended Abstracts of 2016 International Conference on Solid State Devices and Materials (SSDM2016), pp.77-78, September 2016.

- 26. 加藤健太郎, <u>夏井雅典</u>, 羽生貴弘, "Approximate Computing に基づく脳型 LSI の高精度・ 省電力・省面積実装技術の一考察," 平成 28 年度電気関係学会東北支部連合大会, p. 1B03, 2016 年 8 月.

- 6. 研究組織

(1)研究協力者

研究協力者氏名:羽生 貴弘

ローマ字氏名: HANYU, Takahiro

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等については、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属されます。