# 科学研究費助成事業 研究成果報告書

令和 3 年 6 月 1 4 日現在

機関番号: 12608 研究種目: 若手研究(B) 研究期間: 2017~2020

課題番号: 17K14662

研究課題名(和文)2次元有機・無機材料を用いたMIS界面創出とノーマリオフMoS2 FETの実現

研究課題名(英文)Two Dimensional Inorganic/Organic Hetero Interface for Normally Off MoS2 FET

#### 研究代表者

川那子 高暢 (Kawanago, Takamasa)

東京工業大学・科学技術創成研究院・助教

研究者番号:30726633

交付決定額(研究期間全体):(直接経費) 3,400,000円

研究成果の概要(和文):本研究の目的は2次元有機/無機材料界面の制御による二硫化モリブデン(MoS2)電界効果トランジスタ(FET)の閾値電圧(Vth)調整と正のVth動作を実証する事である。ゲート電極に白金(Pt)金属を用い、酸化アルミニウム(AIOx)表面への自己組織化有機単分子膜(SAM)形成によって界面トラップを抑制し正のVth(0.15V)を実証した。Ptゲート電極はアルミニウム(AI)ゲート電極と比較して正の方向へ約1VのVthシフトを示し、PtとAIの仕事関数差を反映している。

研究成果の学術的意義や社会的意義 2次元半導体材料の二硫化モリブデン(MoS2)は移動度が高く、未結合手が無いため化学的、電気的に安定な材料である事から次世代低消費電力エレクトロニクスに向けたFETのチャネル材料として期待されている。本研究によって素子特性で最も重要な閾値電圧制御をMoS2 FETで確立し、正の閾値電圧を実証できた事は次世代低消費電力エレクトロニクスに向けた大きな一歩となり2次元半導体材料の可能性を示す事ができた考えている。

研究成果の概要(英文): Object of this study is to demonstrate the control of threshold voltage (Vth) by engineering a gate metal electrode in molybdenum disulfide (MoS2) field-effect transistors (FETs). The fabrication process for gate stacks involves the deposition of aluminum oxides (AlOx) on a high-work-function metal and the subsequent formation of a self-assembled monolayer (SAM) by an immersion method. A positive Vth of 0.15V was demonstrated using a platinum (Pt) metal as a gate electrode accompanied by a low density of traps at the interface owing to the close-packed SAM. The Pt gate electrode exhibits a Vth shift of about 1V in the positive direction compared with the aluminum (Al) gate electrode. This Vth shift is consistent with the difference in the work function of Pt and Al gate metal electrodes.

研究分野: 半導体ナノデバイス

キーワード: TMDC FET

# 様 式 C-19、F-19-1、Z-19(共通)

# 1.研究開始当初の背景

自己組織化単分子膜(Self-Assembled Monolayer:SAM)は有機分子が自発的に集合して形成され る、緻密かつ配向が揃った分子層 1 層分の結晶膜のことである[1]。この 2 次元有機分子膜は、 材料表面に粘着性、すべり性、濡れ性や耐食性といった様々な特性や機能を付加することができ る[1]。近年、有機半導体トランジスタ(FET)のゲート絶縁膜に SAM を用い、数 nm の極薄膜厚 領域において優れた FET 特性が報告されたことから、SAM のゲート絶縁膜技術という新しい 応用分野が開拓された[2]。しかし国内・国外を含め SAM ゲート絶縁膜および FET 応用に関す る報告は少数のグループに限定されている。この理由は多くの報告が半導体材料の合成及び物 性研究に注力しているためと考えられる。一方、電子デバイスの機能は界面で発現するためゲー ト絶縁膜に非常に高度な特性が要求される。これまでに申請者は、科研費研究活動スタート支援 によって SAM ゲート絶縁膜を用いた金属-絶縁膜-半導体ゲートスタックに関する研究を行って きた。特に、無機層状半導体である二硫化モリブデン(MoS2)をチャネル層に用いた FET を作製 し、2次元有機・無機界面の特性評価を行った[3]。2次元材料系で構成される有機・無機界面は、 電気的、化学的に活性な未結合手(ダングリングボンド)の無い" 閉じた界面 "を実現できるため、 構造欠陥が少なく、界面での化学反応や原子拡散が起こりにくいと考えられる。作製した MoS₂ FET の  $I_d$ - $V_g$  特性は、サブスレッショルドスロープ(SS)が 69mV/dec と低い値を示し、ヒステリ シスも認められないことから良好な界面が実現できた。また断面 TEM から急峻で平坦な MoS<sub>2</sub>/SAM 界面を確認した。これまでの研究によって 2 次元有機・無機界面に関する基礎的な データを取得することができた。また素子作製プロセスの土台を構築することができた。本研究 はこれまでに得られた知見をもとに MoS2 FET の最重要かつ最難関の課題である閾値電圧制御 及びノーマリオフ動作の実現に取り組むものである。2 次元材有機・無機料系で構成される MIS ゲート構造に独自の工夫を加えることで、ノーマリオフ MoS2 FET の動作実証を行う事が本研 究最大の動機である。

#### <引用文献>

- [1] J. Christopher Love, Lara A. Estroff, Jennah K. Kriebel, Ralph G. Nuzzo, and George M. Whitesides, Chem. Rev. 105, 1103–1169, (2005).

- [2] H. Klauk, U. Zschieschang, J. Pflaum and M. Halik, Nature, 445, 15, 745–748, (2007).

- [3] T. Kawanago, and S. Oda, Applied Physics Letters, vol. 108, no. 4, p. 041605, (2016).

# 2.研究の目的

本研究の目的は、二硫化モリブデン( $MoS_2$ )を用いた電界効果トランジスタ(FET)のノーマリオフ動作を実現することである。結晶表面に未結合手が無い層状構造の  $MoS_2$  は、FET への応用が期待されているが、n 型半導体のため閾値電圧が負の値になる。FET 応用に向けてノーマリオフ動作は必須であり、解決すべき重要な課題である。本研究では、 ゲート電極に仕事関数の大きな金属を用いる、 自己組織化単分子膜(SAM)の電気双極子を用いる、 反応性スパッタによる酸化アルミニウムをゲート絶縁膜に用いるという 3 つのアプローチによりノーマリオフ $MoS_2$  FET の動作実証を目指す。特に 2 次元有機・無機材料系は未結合手が無いため、界面での化学反応や原子拡散は起こりにくく、急峻な金属-絶縁膜-半導体(MIS)界面構造の作製が可能になると期待される。

# 3.研究の方法

閾値電圧はトランジスタにおいて最も重要な素子パラメータである。トランジスタのソース-ドレイン電極間にドレイン電流が流れる ON 状態と電流が流れない OFF 状態を閾値電圧によって決定する。閾値電圧の制御技術を確立することは、電子デバイスの研究において最優先事項である。 $MoS_2$  は n 型半導体のため FET の閾値電圧が一般的に負の値になる。 $MoS_2$  FET のノーマリオフ動作を実現するために、本研究では 3 つの要素に関して研究を行う。以下にそれぞれの要素を述べる。

# 1).ゲート電極に用いる金属材料の仕事関数を利用

FET の閾値電圧は、ゲート電極の金属材料の仕事関数によって制御が可能である。仕事関数の小さい金属(例えばアルミニウム(Al):4.1eV)をゲート電極に用いた場合、FET の閾値電圧は負方向ヘシフトする。反対に、仕事関数の大きい金属(例えば白金(Pt):5.3eV)をゲート電極に用いたときには、FET の閾値電圧は正方向ヘシフトする。MoS2 FET は電子が電流のキャリアを担うn 型動作であるため、ノーマリオフ動作の実現には閾値電圧を正方向に移動させる必要がある。故に、本研究ではゲート電極に仕事関数の大きい金属を用いるアプローチを採用する。

# 2).自己組織化単分子ゲート絶縁膜の電気双極子を利用

FET のチャネル層はゲート絶縁膜と接触しているため、閾値電圧はゲート絶縁膜の帯電状態に大きく影響される。本研究では、2 次元有機結晶膜である自己組織化単分子膜(SAM)をゲート絶縁膜に用いるアプローチを採用する。その理由は、SAM 内に形成される電気双極子を利用することで  $MoS_2$  FET の閾値電圧を正方向に移動させるためである。電気陰性度が大きく異なる原子によって構成される SAM は、分子内の電荷分布が偏るために電気双極子を形成する。この電

気双極子によって内部電界が発生し、ゲート絶縁膜と接触している MoS2の界面近傍でバンドの曲がりが生じるため、閾値電圧が変化する。SAM ゲート絶縁膜を用いることで、高い絶縁性と 閾値電圧制御という2つの目的を同時に達成することができる。

3). スパッタによる酸化アルミニウム $(AlO_x)$ との積層  $SAM/AlO_x$ ゲート絶縁膜を利用本研究で用いる SAM は酸化物材料表面にのみ吸着するものである。また、仕事関数の大きな金属上に酸化物を体積する必要がある。本研究では、アルゴン(Ar)と酸素 $(O_2)$ の混合ガスを用いた反応性スパッタによって  $AlO_x$ を堆積するアプローチを採用する。スパッタによる堆積膜は被覆率が高いために、凹凸のある表面にも均一に  $AlO_x$ を堆積することができる。一方、スパッタによる  $AlO_x$  堆積膜は構造欠陥が多く含まれるため閾値電圧に影響を与える。故に、本研究では積層  $SAM/AlO_x$  構造をゲート絶縁膜に用いる。 $MoS_2$  は SAM と接触するため、 $AlO_x$  堆積膜に存在する構造欠陥の影響を抑制することができる。これら 3 つのアプローチを用いることで  $MoS_2$  FET のノーマリオフ動作を実現する。

#### 4.研究成果

本研究の目的は二硫化モリブデン( $MoS_2$ )電界効果トランジスタ(FET)の閾値電圧( $V_{th}$ )を金属ゲート電極によって制御する事である。2次元半導体である  $MoS_2$  は電子的、光学的そして化学的に興味深い性質を持っており、基礎と応用の両方の観点から注目されている。特に  $MoS_2$  は、2次元結晶のためダングリングボンドが無い層状構造を有する事から FET のチャネル材料として非常に期待されている。しかし  $MoS_2$  は通常 n 型半導体であるため、 $MoS_2$  FET での  $V_{th}$  は負の値となる。以前の研究で、アルミニウム(AI)ゲート電極の酸化を伴う自己組織化単分子膜(SAM)を用いた積層  $SAM/AIO_x$  ゲート絶縁膜が開発され、-0.6V の  $V_{th}$  が達成された。この積層  $SAM/AIO_x$  ゲート絶縁膜と仕事関数の大きい金属ゲート電極を組み合わせる事で  $MoS_2$  FET の  $V_{th}$  を制御し、正の  $V_{th}$  を実証する。

本研究ではゲート電極に用いる金属として仕事関数が大きい(5.3 eV)のプラチナ(Pt)を選択した。まず  $SiO_2/Si$  基板上に Pt のゲート電極をリフトオフによって作製した。Pt ゲート電極上に反応性 RF スパッタリングによって酸化アルミニウム( $AlO_*$ )を形成した。次に酸素プラズマを基板に照射し、溶液への浸漬プロセスによって  $AlO_*$ 表面に SAM を形成した。窒素雰囲気中で 100 度の熱処理によって SAM を安定化させた後、ソース/ドレイン金属を作製した。最後に PDMS スタンプによって  $MoS_2$  を転写した。作製した素子の電気特性を評価した。また物理分析を用いて作製した素子の構造を解析した。

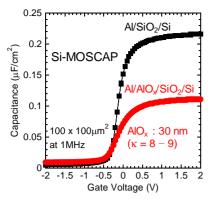

まず反応性 RF スパッタリングによって形成した  $AIO_x$ の膜厚を調べた。熱酸化によって形成した  $SiO_2/Si$  基板上に  $AIO_x$ を堆積し、ゲート電極を形成して  $AIO_x/SiO_2/Si$  構造の MOS キャパシタを作製した。また  $AIO_x$  を堆積していない  $SiO_2/Si$  基板上にもゲート電極を形成し  $SiO_2/Si$  構造の MOS キャパシタも作製した。この二つの MOS キャパシタの容量-電圧特性を測定し、差分を求める事で  $AIO_x$  の膜厚を見積もった(図 1)。その結果、堆積した  $AIO_x$  の膜厚は 30 nm と見積もる事ができた。

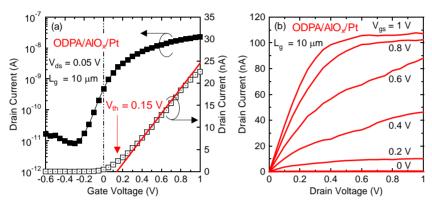

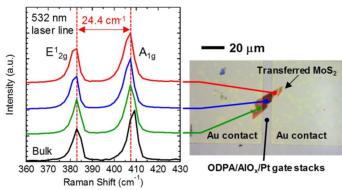

Pt ゲート電極と積層 SAM/AlO $_x$  ゲート絶縁膜を用いた  $MoS_2$  FET が正常にトランジスタ動作する事を確認した。加えて、ドレイン電流-ゲート電圧特性から閾値電圧が  $0.15\,V$  の  $MoS_2$  FET の動作実証に成功した(図 2)。これにより本研究最大の目的である正の閾値電圧を有する  $MoS_2$  FET の実現に成功した。ラマン分光の結果から、基板上に転写した  $MoS_2$  はバルクと全く同じ特性を示す事を確認した(図 3)。これは転写による結晶損傷が極めて低く抑えられている事を示している。当初計画していた SAM の電気双極子による閾値電圧制御は予想していたほどの効果が無い事が分かった。フッ素を含む SAM を用いて  $MoS_2$  FET を作製し実験を行ったが、正側への閾値電圧のシフトは予想していたよりも小さい結果となった。

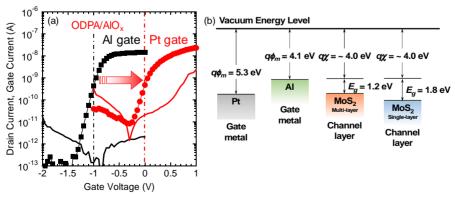

次にアルミニウム(AI)をゲート電極に用いた  $MoS_2$  FET を作製し、ゲート電極の仕事関数が閾値電圧に与える影響を実験的に調査した。作製プロセスは Pt ゲート電極を用いた場合と全く同じである。Pt ゲート電極を用いた  $MoS_2$  FET に比べて Al ゲート電極を用いた  $MoS_2$  FET では、閾値電圧が約 1V 程度負側へシフトする事が分かった(図 4)。 Pt と Al に対する  $MoS_2$  のバンドアライメントを考えると、Pt と Al の仕事関数がそれぞれ 5.3~eV と 4.1~eV である事から(図 4)、この閾値電圧の差はゲート電極に用いた Pt と Al の仕事関数差を反映している事が分かる。本研究によって素子特性で最も重要な閾値電圧制御を  $MoS_2$  FET で確立し、正の閾値電圧を実証できた事は次世代低消費電力エレクトロニクスに向けた大きな一歩となり 2 次元半導体材料の可能性を示す事ができた考えている。

図 1. AlOx/SiO2/Si 構造及び SiO2/Si 構造の MOS キャパシタの容量-電圧特性

図 2. Pt ゲート電極と積層 SAM/AlOx ゲート絶縁膜を用いた MoS2 FET の電流-電圧特性

図 3. ラマン分光測定と作製した MoS2 FET の光学顕微鏡像

図 4. Pt ゲート電極及び Al ゲート電極を用いた  $MoS_2$  FET のドレイン電流-ゲート電圧特性と バンドアライメント

# 5 . 主な発表論文等

3 . 学会等名

4 . 発表年 2019年

ECS 2019 (国際学会)

| . 著者名                                                                                                                                               | 4.巻                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Takamasa Kawanago, Tomoaki Oba, Shunri Oda                                                                                                          | 12                  |

| · · · · · · · · · · · · · · · · · · ·                                                                                                               | F 28/=/F            |

| !. 論文標題<br>Transfer printing of Al203 gate dielectric for fabrication of top-gate MoS2 FET                                                          | 5 . 発行年<br>2019年    |

| B.雑誌名                                                                                                                                               | 6.最初と最後の頁           |

| Applied Physics Express                                                                                                                             | 026501-1 ~ 4        |

| 『載論文のDOI(デジタルオブジェクト識別子)                                                                                                                             | 査読の有無               |

| 10.7567/1882-0786/aaf995                                                                                                                            | 有                   |

| tープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                              | 国際共著                |

| .著者名                                                                                                                                                | 4 . 巻               |

| Kawanago Takamasa、Oda Shunri                                                                                                                        | 110                 |

| 2.論文標題                                                                                                                                              | 5 . 発行年             |

| Control of threshold voltage by gate metal electrode in molybdenum disulfide field-effect transistors                                               | 2017年               |

| 3.雑誌名                                                                                                                                               | 6.最初と最後の頁           |

| Applied Physics Letters                                                                                                                             | 133507 ~ 133507     |

| 引載論文のDOI(デジタルオブジェクト識別子)                                                                                                                             | <br>  査読の有無         |

| 10.1063/1.4979610                                                                                                                                   | 有                   |

| t−プンアクセス                                                                                                                                            | 国際共著                |

| オープンアクセスではない、又はオープンアクセスが困難                                                                                                                          | -                   |

| .著者名                                                                                                                                                | 4 . 巻               |

| Kawanago Takamasa、Ikoma Ryo、Oba Tomoaki、Takagi Hiroyuki                                                                                             | 111                 |

| 2.論文標題                                                                                                                                              | 5 . 発行年             |

| Fabrication of hybrid self-assembled monolayer/hafnium oxide gate dielectric by radical oxidation for molybdenum disulfide field-effect transistors | 2017年               |

| 3.雑誌名                                                                                                                                               | 6.最初と最後の頁           |

| Applied Physics Letters                                                                                                                             | 202904 ~ 202904     |

| 引載論文のDOI(デジタルオブジェクト識別子)                                                                                                                             | <u>│</u><br>│ 査読の有無 |

| 10.1063/1.4998313                                                                                                                                   | 有                   |

| トープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                              | 国際共著                |

| オーノンテッ ヒヘ しはない、 又はオーノンテッ ヒヘル 凶無                                                                                                                     | <u> </u>            |

| 学会発表 〕 計21件(うち招待講演 4件 / うち国際学会 10件)                                                                                                                 |                     |

| . 発表者名<br>Takamasa Kawanago, Tomoaki Oba, Shunri Oda                                                                                                |                     |

| 2.発表標題                                                                                                                                              |                     |

| Fabrication of top-gate MoS2 FET with transferred AI203 gate dielectric                                                                             |                     |

| 1.発表者名<br>川那子高暢,松﨑貴広,小田俊理                                                                                              |

|------------------------------------------------------------------------------------------------------------------------|

| 2.発表標題<br>ゲート絶縁膜転写とPVAドーピングによるトップゲートMoS2 FET の作製                                                                       |

| 3.学会等名<br>第67回応用物理学会春季学術講演会                                                                                            |

| 4 . 発表年<br>2020年                                                                                                       |

| 1.発表者名<br>松崎貴広,大場智明,川那子高暢,小田俊理                                                                                         |

| 2.発表標題<br>PVA によるMoS2 FET へのキャリアドーピングと電気特性への影響                                                                         |

| 3.学会等名<br>第80回応用物理学会秋季学術講演会                                                                                            |

| 4 . 発表年 2019年                                                                                                          |

| 1.発表者名<br>Takamasa Kawanago                                                                                            |

| 2 . 発表標題<br>MoS2 FET fabricated by adhesion lithography                                                                |

| 3.学会等名<br>International Symposium 3RD Japan-EU Flagship Workshop on Graphene and Related 2D Materials 2018(招待講演)(国際学会) |

| 4 . 発表年 2018年                                                                                                          |

| 1.発表者名<br>Takamasa Kawanago                                                                                            |

| 2 . 発表標題<br>Two-dimensional inorganic/organic hetero interface for field-effect transistor applications                |

| 3 . 学会等名<br>Recent Progress Graphene Research (RPGR) 2018(招待講演)(国際学会)                                                  |

| 4 . 発表年<br>2018年                                                                                                       |

|                                                                                                                        |

| 1 . 発表者名<br>Takamasa Kawanago                                                                 |

|-----------------------------------------------------------------------------------------------|

|                                                                                               |

| 2.発表標題<br>Two-dimensional inorganic/organic interface for field-effect transistor application |

| 3.学会等名                                                                                        |

| 1st Workshop on Novel 2D Device & Materials Physics (2DMaP)(招待講演)                             |

| 4. 発表年                                                                                        |

| 2018年                                                                                         |

| 1 . 発表者名<br>Takamasa Kawanago, Tomoaki Oba, Ryo Ikoma, Hiroyuki Takagi, Shunri Oda            |

| 2 . 発表標題                                                                                      |

| Gated Four-Probe Method to Evaluate the Impact of SAM Gate Dielectric on Mobility in MoS2 FET |

| 3.学会等名                                                                                        |

| ESSDERC 2018 (国際学会)                                                                           |

| 4.発表年                                                                                         |

| 2018年                                                                                         |

|                                                                                               |

| 1.発表者名<br>川那子高暢,大場智明,小田俊理                                                                     |

| 2.発表標題                                                                                        |

| Al2O3ゲート絶縁膜転写法を用いたトップゲートMoS2 FETの作製                                                           |

|                                                                                               |

|                                                                                               |

| 3 . 学会等名<br>第66回応用物理学会春季学術講演会                                                                 |

| 4.発表年                                                                                         |

| 2019年                                                                                         |

| 1 . 発表者名                                                                                      |

| 川那子高暢,大場智明,小田俊理                                                                               |

|                                                                                               |

|                                                                                               |

| 2.発表標題                                                                                        |

| SAMゲート絶縁膜を用いたMoS2 FETのチャネル移動度への影響                                                             |

|                                                                                               |

|                                                                                               |

| 3 . 学会等名<br>第79回応用物理学会秋季学術講演                                                                  |

| 4.発表年                                                                                         |

| 2018年                                                                                         |

|                                                                                               |

|                                                                                               |

| 1.発表者名<br>Tomoaki Oba, Takamasa Kawanago, Shunri Oda                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------|

| 2 . 発表標題<br>Gated Four-Probe Method for Evaluation of Electrical Characteristics in MoS2 Field-Effect Transistors                     |

| 3.学会等名<br>Recent Progress Graphene Research (RPGR) 2018(国際学会)                                                                         |

| 4 . 発表年 2018年                                                                                                                         |

| 1.発表者名<br>Takamasa Kawanago, Ryo Ikoma, Tomoaki Oba, Hiroyuki Takagi                                                                  |

| 2 . 発表標題<br>Radical Oxidation Process for Hybrid SAM/HfOx Gate Dielectrics in MoS2 FETs                                               |

| 3.学会等名<br>47th European Solid-State Device Research Conference(国際学会)                                                                  |

| 4 . 発表年 2017年                                                                                                                         |

| 1.発表者名                                                                                                                                |

| Takamasa Kawanago, Wanjing Du, Ryo Ikoma, Tomoaki Oba, Hiroyuki Takagi and Shunri Oda                                                 |

| 2.発表標題 Transfer printing of nanostructured membrane with elastomeric stamp and its application to TMDC-based field-effect transistors |

| 3.学会等名<br>17th International Workshop on Junction Technology(招待講演)(国際学会)                                                              |

| 4 . 発表年 2017年                                                                                                                         |

|                                                                                                                                       |

| 1.発表者名 Ryo Ikoma, Takamasa Kawanago                                                                                                   |

| 2 ※幸福時                                                                                                                                |

Heavily-doped SOI Substrate and Transfer Printing for Charge Injection into

3 . 学会等名 17th International Workshop on Junction Technology(国際学会)

4 . 発表年 2017年

| 1.発表者名 川那子 高暢、居駒 遼、高木 寛之、小田 俊理                                                             |

|--------------------------------------------------------------------------------------------|

| 2 . 発表標題<br>高濃度SOI基板と転写法によるTMDC FETsの作製                                                    |

|                                                                                            |

| 4.発表年<br>2017年                                                                             |

| 1 . 発表者名<br>Ryo Ikoma, Takamasa Kawanago, Yukio Kawano                                     |

| 2 . 発表標題<br>Heavily-doped SOI with SAM-Based Gate Dielectrics in Application to TMDC FET   |

| 3 . 学会等名<br>232nd ECS MEETING(国際学会)                                                        |

| 4 . 発表年<br>2017年                                                                           |

| 1 . 発表者名<br>Hiroyuki Takagi, Ryo Ikoma, Tomoaki Oba, Takamasa Kawanago                     |

| 2. 発表標題<br>Polarity Control in WSe2 Field-Effect Transistors using Dual Gate Architecture  |

| 3. 学会等名<br>2nd Electron Devices Technology and Manufacturing (EDTM) Conference 2018 (国際学会) |

| 4 . 発表年<br>2018年                                                                           |

| 1.発表者名<br>居駒遼,川那子高暢,河野行雄                                                                   |

| 2 . 発表標題<br>剥離転写法による高濃度ドープSOI基板を用いたTMDC-FETの作製                                             |

| 3.学会等名<br>第78回応用物理学会秋季学術講演                                                                 |

| 4 . 発表年<br>2017年                                                                           |

|                                                                                            |

| 1.発表者名<br>高木寛之,居駒遼,大場智昭,川那子高暢               |

|---------------------------------------------|

|                                             |

|                                             |

| 2 . 発表標題<br>濃度SOI基板をゲート電極に用いたWSe2pFETの作製    |

|                                             |

| 3.学会等名<br>第78回応用物理学会秋季学術講演                  |

| 4 . 発表年                                     |

| 2017年                                       |

| 1.発表者名<br>大場智昭,居駒遼,川那子高暢                    |

|                                             |

| 2 . 発表標題<br>積層SAM/HfOxゲート絶縁膜を用いたMoS2 FETの作製 |

|                                             |

| 3.学会等名<br>第78回応用物理学会秋季学術講演                  |

| 4 . 発表年                                     |

| 2017年                                       |

| 1.発表者名<br>川那子高暢,居駒遼,大場智昭,高木寛之               |

| 2.発表標題                                      |

| 2 . 光表標題<br>積層SAM/HfOxゲート絶縁膜を用いたMoS2 FETの作製 |

| 3.学会等名                                      |

| 第65回応用物理学会春季学術講演会                           |

| 4 . 発表年<br>2018年                            |

| 1.発表者名                                      |

| 川那子高暢,高木寛之,居駒遼,大場智昭                         |

| 0 7X-14EPE                                  |

| 2.発表標題<br>基板バイアス構造を用いたキャリア注入制御とWSe2FETの作製   |

|                                             |

| 3.学会等名<br>第65回応用物理学会春季学術講演会                 |

| 4 . 発表年<br>2018年                            |

|                                             |

|                                             |

| 〔図書〕 計2件                             |                       |                |

|--------------------------------------|-----------------------|----------------|

| 1.著者名 川那子高暢(分担執筆)                    |                       | 4.発行年<br>2020年 |

| 2.出版社 エヌ・ティー・エス出版                    |                       | 5.総ページ数<br>479 |

| 3.書名 グラフェンから広がる二次元物質の                | 新技術と応用                |                |

|                                      |                       |                |

| 1 . 著者名<br>川那子 高暢                    |                       | 4.発行年<br>2018年 |

| 2 . 出版社<br>応用物理 第87巻 第7号 511         |                       | 5.総ページ数 5      |

| 3.書名<br>自己組織化有機単分子膜を用いた界面制御とゲート絶縁膜技術 |                       |                |

|                                      |                       |                |

| 〔産業財産権〕                              |                       |                |

| [その他]                                |                       |                |

| -                                    |                       |                |

| 6.研究組織                               |                       |                |

| 氏名<br>(ローマ字氏名)<br>(研究者番号)            | 所属研究機関・部局・職<br>(機関番号) | 備考             |

7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国相手方研究機関 |  |

|----------------|--|

|----------------|--|