# 科学研究費補助金研究成果報告書

平成21年5月26日現在

研究種目:基盤研究(B)研究期間:2006~2008課題番号:18360166

研究課題名(和文) 位相量子を用いたナノスケール超高速論理回路の研究

研究課題名(英文) A Study of Nano-Scale, High-Speed Logic Circuits using a Phase Quantum

### 研究代表者

吉川 信行 (YOSHIKAWA NOBUYUKI) 横浜国立大学・大学院工学研究院・教授

研究者番号:70202398

研究成果の概要:超伝導体中の量子化された磁束を情報担体とする単一磁束量子論理回路は、 高速性、低消費電力性に優れるが、超伝導インダクタンスを用いるためゲートサイズの微細化 が制限される。これに対して本研究で提案する位相量子論理回路は、ジョセフソン接合の位相 差を用いて磁束を保持するため、原理的にナノメータ寸法の論理ゲートを実現できる。本研究 では、ナノスケール集積化が可能な位相量子論理回路の原理実証と設計方法論の確立を行ない、 試作を通して本回路の基本特性を明らかにした。

#### 交付額

(金額単位:円)

|        | 直接経費         | 間接経費        | 合 計          |

|--------|--------------|-------------|--------------|

| 2006年度 | 7, 800, 000  | 2, 340, 000 | 10, 140, 000 |

| 2007年度 | 4, 100, 000  | 1, 230, 000 | 5, 330, 000  |

| 2008年度 | 2, 600, 000  | 780, 000    | 3, 380, 000  |

| 年度     |              |             |              |

| 年度     |              |             |              |

| 総計     | 14, 500, 000 | 4, 350, 000 | 18, 850, 000 |

研究分野:電子デバイス、集積回路

科研費の分科・細目:電気電子工学・電子デバイス・電子機器

キーワード:超伝導集積回路、単一磁束量子、ナノデバイス、ジョセフソン素子、超高速論理 回路、SFQ、インダクタンス、位相量子

### 1. 研究開始当初の背景

超伝導体中の量子化磁束を情報担体とする単一磁束量子回路は、従来の電圧レベルを情報の「0」「1」に対応させた論理回路とは異なり、粒子的性質を持つパルスを情報担体とする回路方式である。高速性、低消費電力性に優れ、次世代の高性能論理回路の有力候補にあげられている。本回路は、1990年代

前半に旧ソ連のグループにより体系化され、760GHz に達するフリップフロップの高速動作が実証された。その後、米国の HTMT プロジェクトにおいて、マイクロプロセッサの構成技術として研究が進められ、目標周波数を20GHz とした SFQ プロセッサが設計されている。日本においては、単一磁束量子回路における設計技術の重要性に着目し、回路最適化

手法の確立、セルベース設計法の導入、セルライブラリの標準化を進めてきた。これらの努力の結果、世界初の8ビットマイクロプロセッサの16GHz動作に成功するなど、現在では、世界で最も高い研究水準にまで達した。これらの研究において、申請者は、その主要な役割を果たして来た。

しかしながら、従来の方法では、超伝導ループから成るインダクタンスを用いて量子 化磁束を保持するため、原理的にゲートサイズは数 $\mu$ m 程度に制限される。申請者は、単一磁束量子論理回路の欠点である集積性に注目し、これを抜本的に解決し、さらにナノスケール高集積論理回路への展開を図るために、位相量子を情報担体とする新しい原理の論理回路を提案した。

#### 2. 研究の目的

本研究では、ナノスケール集積化が可能な 位相量子を情報担体とする超高速論理回路 を提案し、動作の原理実証、設計方法論を確 立する。

単一磁束量子論理回路は、超伝導ループから成るインダクタンスを用いて量子化磁束を保持するため、原理的にゲートサイズは数μm程度に制限される。これに対して本研究で提案する位相量子論理回路は、Josephson接合の位相差を用いて量子化磁束を保持する。そのために、論理ゲートの飛躍的な縮小化が可能であり、原理的に数十nm程度の論理ゲートが作製できる。これにより、動作周波数が数百GHz、消費電力が半導体回路の千分の1、論理ゲートサイズが数十nmという究極的な論理回路の実現が可能となる。更に、Josephsonインダクタンスの可変性を利用すれば新機能論理ゲートが構成できる。

本研究では、まず、既存の Nb 集積回路プロセスを用いて位相量子論理回路の原理を実証し、その設計方法論を確立する。また、プロトタイプシステムとしてメモリを試作し、回路の基本特性を明らかにする。

#### 3. 研究の方法

まず、電荷型デバイスと磁束型デバイスの 寸法について考える。それぞれのデバイスの 寸法を  $l_e$ ,  $l_F$  とすれば、電子と単一磁束量子を 蓄えるために必要なエネルギーは、それぞれ

> $U_{\rm e} = {\rm e}^2/2 C = {\rm e}^2/2 \epsilon_0 l_{\rm e},$  $U_{\rm F} = \Phi_0^2/2 L = \Phi_0^2/2 \mu_0 l_{\rm F}$

となる。両者のエネルギーを等しいと置けば、 それらの寸法比は、

> $l_{\rm F} / l_{\rm e} = (\epsilon_0/\mu_0)(\Phi_0/e)^2$ =  $[{\rm h}/(2{\rm e})^2]^2/Z_0^2$ =  $(6.45~{\rm k}\Omega/377~\Omega)^2$  $\sim~1000$

となる。すなわち、単一磁束量子デバイスの 寸法は、単電子デバイスに比べて原理的に約 1000 倍大きい。これは、空間のインピーダンスに対して量子抵抗が大きいためである。

単一磁束量子論理回路は、高速性、低消費電力性に優れており、単位エネルギー当りの演算能力が極めて高いことから、ポストCMOS 論理回路の有力候補に挙げられている。しかしながら、情報システムの処理能力は、集積度とクロック周波数の積で与えられ、集積度の低い単一磁束量子は、総合的な情報処理能力面で問題があった。

本研究で提案する、位相量子論理回路は、磁束量子を磁界ではなく位相として保持するため、デバイス寸法に関する上述の制限を本質的に無くすことができる。したがって、単一磁束量子論理回路の高性能性を維持しながら、その回路寸法をナノメータスケールまで縮小化させることができ、究極の情報処理能力を達成できる。

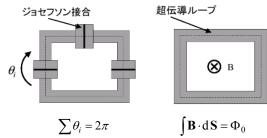

図 1 に位相量子(PQC)論理回路と単一磁束 量子(SFQ)論理回路を比較した。磁束の量子 化は超伝導ループ中の磁束が $\Phi_0 = h/2e$  に量 子化される現象である。一方、Josephson 接 合間には位相差θが生じるが、Josephson 接 合を複数含むループでは、位相差の和が 2π となるように位相が量子化される。本提案で はこれを位相量子と呼び、この位相量子を情 報担体に用いた論理回路を提案する。この位 相の量子化現象は、別の見方をすれば、 Josephson 接合が等価インダクタンス  $L_{\rm J}$  =  $\Phi_0$  /( $2\pi I_{\rm ccos}\theta$ )をもつ回路素子として振舞う として理解できる。磁束の量子化現象では、 超伝導ループのインダクタンスが磁気エネ ルギーを保持するのに対して、位相の量子化 では、Josephson の結合エネルギーが磁気エ ネルギーを保持するため、本質的に接合寸法 に関する制約が無くなる。

(a) 位相量子回路 (b) 単一磁束量子回路 図1 位相量子論理回路と単一磁束量子論理 回路の比較

### 4. 研究成果

### (1) Josephson インダクタンス

Josephson接合は電気回路的にインダクタンスとして働き、このときのインダクタンスを特に Josephson インダクタンスと呼ぶ。

大振幅動作時の Josephson インダクタンスは式(1)で表わされる。

$$L_J = L_k \frac{\phi}{\sin \phi} \tag{1}$$

$$\sum \sum \mathcal{C} \cdot L_k = \frac{\Phi_0}{2\pi I_c} \tag{2}$$

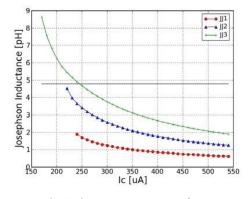

である。 $\phi$ は Josephson 接合の巨視的波動関数の位相差、 $\Phi_0$ は磁束量子、 $I_c$ は Josephson接合の臨界電流値である。 Josephson インダクタンスは非線形な性質を持ち、 $\phi=\pi/2$  で最大となる。

Josephson インダクタンスは非線形な性質をもつため、実際の回路の中でどの様にインダクタンスを決定するかが問題になる。そこで本検討では各回路素子において接合を流れる電流を求め、実効的な Josephson インダクタンスの大きさを評価した。

具体的には、超伝導回路シミュレータ Jsim を用いて Josephson インダクタンスを担う接合に流れる電流を解析した。それを、式(1) に代入することで Josephson インダクタンスの値を決定する。

#### (2) Josephson 伝送線路(JTL)の設計

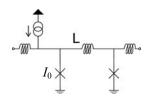

位相量子論理回路を用いた回路としてまず JTL を検討した。通常の SFQ 論理回路における JTL を図 2 (a) に示す。インダクタンス L は 4.8 pH、接合の臨界電流値  $I_0$  は 218  $\mu$  A である。このインダクタンス Lを Josephson インダクタンスで置き換えた位相量子論理回路の JTL を図 2 (b) に示す。Josephson インダクタンスを担う接合は n 個の直列接続された接合で構成されている。

(a) SFQ JTL.  $I_0$ =216 $\mu$ A, L=4.8 pH

(b) PQC JTL.  $I_0$ =216 $\mu$ A

図 2 SFQ 論理回路と位相量子論理回路の

# JTL の回路図

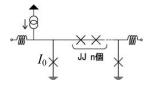

最初に、SFQパルスが伝搬する際に、 Josephson インダクタンスを含むループに流れる電流の解析を行った。SFQパルスが伝搬 する際、電流値は時間的に変化するが本検討ではその最大値を用いることとした。これは、電流の最大値から算出したインダクタンスの最大値が、その回路が等価的に感じるインダクタンスとして適切だと考えたためである。Josephson インダクタンスを担う接合の臨界電流値  $I_c$ を変化させていった時の接合電流をシミュレーションで求めた結果を、図3に示す。図において接合の臨界電流値  $I_c$ が小さい場合、接合には $I_c$ よりも大きな電流が流れ、接合は電圧状態にスイッチしてしまう。一方、 $I_c$ が大きい場合は接合数 $I_c$ に寄らずほぼ一定の電流が流れることがわかる。これは JTL を構成する接合  $I_c$ により電流が制限されるためである。

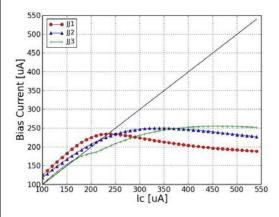

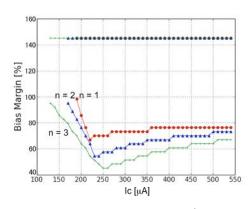

図 3 で得た接合電流と式(2) を用いて、実効 Josephson インダクタンスを算出した。結果を図 4 に示す。横線が L=4.8pH となる値である。これと Josephson インダクタンスの曲線との交点より、接合数 3 個で臨界電流値246  $\mu$ A の接合を用いれば良いことが分かる。図 5 には n=1, 2, 3 に対する JTL のバイアスマージンの臨界電流値依存性を示す。図よりn=3 で  $I_c$ =250  $\mu$ A の時に-53~+43%と最も大きなバイアスマージンが得られていることがわかる。

図3 PQC JTLの Josephson インダクタンス 用接合に流れる電流と接合臨界電流の関係

図 4 実効ジョセフソンインダクタンスの 臨界電流値依存性.  $(I_0=216 \mu A)$

### (3) 位相量子論理回路の試作

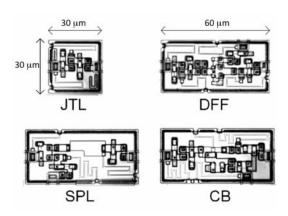

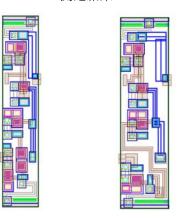

位相量子論理回路の動作を実証するため に JTL、DFF、 splitter、 confluence buffer の各セルの試作を行った。試作には SRL 標準 プロセスを用いた。これらの顕微鏡写真を図 6 に示す。

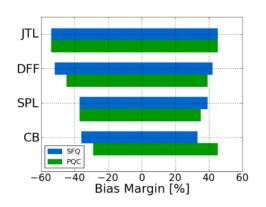

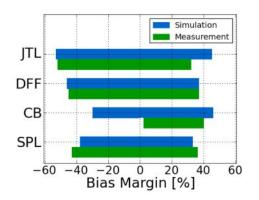

これらについてシミュレーションの結果を図7に示す。シミュレーション結果より位相量子論理回路はSFQ論理回路とほぼ同等のバイアスマージンを有することがわかる。各セルについて測定結果を図8に示す。CBを除き全体としてシミュレーションと同等の十分なバイアスマージンを示していることがわかる。

SRL 標準プロセスを用いて磁気シールドされたシフトレジスタを作成した。シールドされた PQC シフトレジスタを図 9(a) に、SFQ シフトレジスタを図 9(b) に示す。図 9(a) において Josephson インダクタンスは 2 つの接合より形成されている。これは接合の浮遊インダクタンスを考慮した結果である。それぞれのセル面積は、PQC シフトレジスタが  $15\times40$   $\mu$  m、SFQ シフトレジスタが  $20\times40$   $\mu$  m である。SFQ 論理回路ではフリップフロップ部で

図 5 PQC JTL のバイアスマージンの 臨界電流値依存性.  $(I_0=216~\mu A)$

図6 位相量子論理回路の顕微鏡写真

磁束を保持するため大きなインダクタンス L。 が必要であり、回路面積もそれに伴って大き くなっている。しかし位相量子論理回路では 磁束保持用のインダクタンスの面積が小さ くなっており、全体として回路面積は小さく なっている。

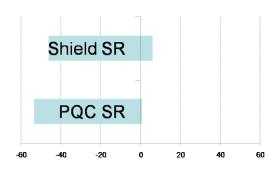

これらのシフトレジスタを SRL 標準プロセスで試作し、DC バイアスマージンの比較を行った。測定結果を図10に示すが、位相量子

図7 PQC回路とSFQ回路のDCバイアスマー ジンのシミュレーション結果

図8 **PQC** 回路の DC バイアスマージンの 測定結果

(a) 位相量子論理回路(b) SFQ 論理回路図 9 シフトレジスタのマスクレイアウト

論理回路のシフトレジスタも SFQ 論理回路と同等のバイアスマージンを持つことがわかる。

#### (4) まとめ

超伝導インダクタンスとジョセフソンインダクタンスの等価性について理論的、実験的検討を行なった。複数の直列ジョセフソン接合を含むジョセフソン等価インダクタンスの大きさを評価し、回路素子としての等価インダクタンスの計算方法を明らかにした。

これらの知見に基づき、位相量子論理回路 を提案し、回路シミュレーションを通して回 路動作の原理的実証を行なった。また、回路 の基本性能(動作機能、動作マージン、動作 周波数等)の理論的解析を行ない、それらの 基本特性を明らかにし、位相量子論理回路の 設計方法論を確立した。

超伝導ファウンドリープロセスを用いて それらの基本ゲートを試作し、動作検証を行 った。具体的には、伝送線路、パルス合流回 路、分岐回路、Dフリップフリップ等の基本 ゲートにおいて、大規模回路の作成のために 十分な DC 電源の動作マージンを得ることが できた。更に、大規模集積化メモリーの実現 を念頭に、位相量子基本ゲートを用いてシフ トレジスタを試作し、その動作実証を行った。 開発した位相量子論理回路に基づくシフト レジスタは、従来のシフトレジスタに対して 大幅な回路面積の低減を達成した。以上の様 に、位相量子論理回路の設計手法を確立し、 小規模回路の安定動作を示すことにより、高 密度集積化が可能な単一磁束量子回の実現 が可能であることを示すことができた。

図 1 0 SFQ シフトレジスタ (Shield SR) と 位相量子論理回路シフトレジスタ (PQC SR) の DC バイアスマージンの比較.

# 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に

#### は下線)

### 〔雑誌論文〕(計7件)

- (1) H. Park, Y. Yamanashi, K. Taketomi, <u>N. Yoshikawa</u>, A. Fujimaki, N. Takagi, "Novel serial–parallel converter using SFQ logic circuits" Physica C, vol.468, September 2008, pp. 1977-1982 (査読有).

- (2) K. Nakamiya, <u>N. Yoshikawa</u>, A. Fujimaki, H. Terai, Y. Hashimoto, "Direct measurements of propagation delay of single-flux-quantum circuits by time-to-digital converters", IEICE Electronics Express, Vol. 5 (2008), No. 9, pp.332-337 (查読有).

- (3) Y. Nobumori, T. Nishigai, K. Nakamiya, <u>N. Yoshikawa</u>, A. Fujimaki, H. Terai, S. Yorozu, "Design and Implementation of a Fully Asynchronous SFQ Microprocessor: SCRAM2," IEEE Trans. Applied Superconductivity. vol. 17, June 2007, pp. 478-481 (査読有).

- (4) T. Hikida, K. Fujiwara, N. Yoshikawa, A. Fujimaki, H. Terai, S. Yorozu, "Bit-Error-Rate Measurements of RSFQ Shift Register Memories," IEEE Trans. Applied Superconductivity. vol. 17, June 2007, pp. 512-515 (査読有).

- (5) Y. Yamanashi, T. Nishigai, N. Yoshikawa, "Study of LR-Loading Technique for Low-Power Single Flux Quantum Circuits," IEEE Trans. Applied Superconductivity. vol. 17, June 2007, pp. 150-153 (査読有).

- (6) Y. Yamanashi, T. Asano, <u>N. Yoshikawa</u>, "On-chip microwave generator for manipulation of superconductive quantum bits," Physica C, vol. 445-448, October 2006, pp. 967-970 (査読有).

- (7) T. Nishigai, S. Yamada, <u>N. Yoshikawa</u>, "Design and implementation of low-power SFQ circuits using LR-load biasing technique," Physica C, vol. 445-448, October 2006, pp. 1029-1033 (査読有).

### 〔学会発表〕(計3件)

- (1) Y. Natume, M. Igarashi, Y. Yamanashi, N. Yoshikawa, "High-density integration of single-flux-quantum circuits using Josephson inductance", Abstracts on 21th International Symposium on Superconductivity (ISS2008), Tsukuba, 27 29 October 2008, FDP-21.

- (2) 夏目侑紀,五十嵐正憲,中禮浩二,<u>吉川</u> 信行、"位相量子論理回路による SFQ シフト レジスタメモリの高密度化"、2008 年春季第 55 回応用物理学関係連合講演会、28p-NA-9、 日本大学理工学部、2008 年 3 月 28 日

- (3) Y. Natsume, M. Igarashi, K. Churei, <u>N. Yoshikawa</u>, "High Density Integration of SFQ Shift Register Memories using Phase Quantum Logic Circuits", Superconducting SFQ VLSI

Workshop 2008, P2-8, Yokohama National University, Japan, 17 March 2008.

〔学会発表〕 ホームページ等 http://www.yoshilab.dnj.ynu.ac.jp/jpn/index.html

### 6. 研究組織

(1)研究代表者

吉川 信行(YOSHIKAWA NOBUYUKI) 横浜国立大学・大学院工学研究院・教授 研究者番号:70202398

# (2)研究分担者

金田久善(KANEDA HISAYOSHI) 横浜国立大学・大学院工学研究院・助手 研究者番号:30242382

# (3)連携研究者