# 科学研究費補助金研究成果報告書

平成 21 年 6 月 12 日現在

研究種目:基盤研究(C) 研究期間:2006~2008 課題番号:18500017

研究課題名(和文) マルチコア、リコンフィギャラブルアーキテクチャ時代の

基盤ソフトウェアの研究

研究課題名(英文) Study on Systems Software for Muliticore and Reconfigurable

Computer Architecture

研究代表者 並木 美太郎(Namiki Mitaro)

東京農工大学・大学院共生科学技術研究院・教授

研究者番号: 10208077

#### 研究成果の概要:

単一チップ内の均質または異質な実行実体を持つマルチコアプロセッサを、また、動的に再構成可能なアーキテクチャを柔軟かつ効率良く利用して、応用ソフトウェアに提供するために、これらのアーキテクチャに適した資源管理を行う基盤ソフトウェアの構成原理を解明した。具体的には、OSによるリコンフィギャラブルプロセッサの制御方式、プログラミング環境の実装方式、Cellなどのマルチコアプロセッサ上の OSアーキテクチャとその実装方式を提案し、試作することにより、方式の有効性を確認した。本研究により、次世代の計算機システムで主流となる、マルチコア、リコンフィギャラブルアーキテクチャを有効利用するソフトウェアアーキテクチャを明らかにすることができた。

#### 交付額

(金額単位:円)

|         | 直接経費      | 間接経費    | 合 計       |

|---------|-----------|---------|-----------|

| 2006 年度 | 1,600,000 | 0       | 1,600,000 |

| 2007 年度 | 1,100,000 | 330,000 | 1,430,000 |

| 2008 年度 | 800,000   | 240,000 | 1,040,000 |

| 年度      |           |         |           |

| 年度      |           |         |           |

| 総計      | 3,500,000 | 570,000 | 4,070,000 |

研究分野:総合領域

科研費の分科・細目:情報学・ソフトウェア

キーワード:オペレーティングシステム、システムソフトウェア、マルチコアプロセッサ、

リコンフィギャラブルプロセッサ

#### 1.研究開始当初の背景

近年、計算機アーキテクチャとして、一つのプロセッサチップ内に複数のプロセッサテップ内に複数のプロセッサアーキテクチャが、また、チップ内の構造を動的に変更可能なリコンフィギャラブル・アーキテクチャでは、従来の固定的な計算機アーキテクチャでは不可能な柔軟かつ高性能な適応した計算機環境を提供できる可能性を秘めした計算機環境を提供できる可能性を秘め

ている。例えば、1 命令でチップ内の構成を 変更可能なマルチコアコンテキストを有す る FPGA が出現し、また、ゲーム機の CELL で は、一つのコア CPU と 8 エンジンのマルチコ ア構成を採用している。

現状では、マルチコア、リコンフィギャラブル・アーキテクチャによるハードウェア向けのソフトウェア開発では、組込みソフトウェア同様、応用ごとに個別の最適化技法を用いた、職人芸的なアドホックな手法に頼っている。近年の OS は、多様な計算機システム

上で動作するが、例えばプロセス切替えとほ ぼ同等の短時間に構成が動的に再構成され るハードウェアに対応できるような資源管 理や仮想化を行ってはいない。SMP(対称型マ ルチプロセッサ)向けやクラスタ向けの OS は 確立した技術になっている。しかし、マルチ コアのように単一チップ内で、均質なものだ けでなく、CPU と DSP、CPU や高機能メモリの 混載、CPU と画像エンジンなどのように異質 な資源を単一チップに搭載し、かつ各資源を 密に結合したハードウェアは従来の基盤ソ フトウェアは扱っていなかった。このような ハードウェアに対応する OS、特に、各資源の 適切な仮想化手法、資源管理方式は存在しな い。また、プログラミングシステムもマルチ コア、リコンフィギャブル向けに適材適所を 生かすプログラミング環境を提供するもの はない。

### 2.研究の目的

本研究では、単一チップ内の均質または異質な実行実体を持つマルチコアプロセッサを、また、動的に再構成可能なアーキテクチャを柔軟かつ効率良く利用して、応用ソフトウェアに提供するために、これらのアーキテクチャに適した資源管理を行う基盤ソフトウェアの構成原理を解明する。次の内容を本研究申請の目標とした。

- (1) チップ内部で極めて密に結合された均質 または異質な構成を持つマルチコアプロ セッサにおいて、軽量かつ高速な実行実体 を提供するプロセッサ・メモリ・入出力の 仮想化方式の解明と機構の確立

- (2) 実行時にシステム構成を変更可能なリコンフィギャラブルアーキテクチャに適した基盤ソフトウェア、具体的には OS が提供する各種仮想化機能の解明と機構の確立

- (3) マルチコア、リコンフィギャラブルプロセッサを活用するプログラミング環境の提案

以上を通じて、応用ソフトウェアに適応的でかつハードウェア独立な、マルチコア、リコンフィギャラブル・アーキテクチャ向けの基盤ソフトウェア、特に、OS、ランタイムルーチンの資源管理方式とプログラミング環境の機能と構成を明らかにする。

#### 3.研究の方法

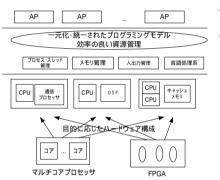

本研究では、マルチコア、リコンフィギャラブル・アーキテクチャに基づく計算機システムに対して、基盤ソフトウェアレベルで体系的で統一された資源管理の方式とプログラミングモデルを明らかにする点が学術的な特色・独創的な点であった。

本研究で解明・発案される方式に基づく OS・ランタイムライブラリ・言語処理系を実

現することで、組込みシステムからハイエン ド計算サーバシステム構築に適用可能なマ ルチコア、リコンフィギャラブル・アーキテ クチャトの応用ソフトウェアに効率の良い 実行環境の提供と開発が容易となるプログ ラミング環境を実現できる。近年、組込みシ ステムでは、マルチコアプロセッサによる性 能向上、リコンフィギャラブルアーキテクチ ャによる応用向け計算機システム構築が重 要なテーマとなっている。また、クラスタに よる高性能計算機などにおいても、演算プロ セッサと通信プロセッサを同一チップ内に 収納したプロセッサが登場している。本研究 申請で明らかになる方式と実装される基盤 ソフトウェアにより、組込みシステム構築や 高性能計算機構築において統一的で一貫性 のあるシステム開発環境を実現することが 可能になる。基本的なソフトウェアアーキテ クチャを次の図に示す。

具体的には、次の研究を行うこととした。

(1) チップ内部で極めて密に結合された均質または異質な構成を持つマルチコアプロセッサにおいて、軽量かつ高速な実行実体を提供するプロセッサ・メモリ・入出力の仮想化方式の解明と機構の確立

マルチコアプロセッサ内部では、一つのチ ップの中に、均質・異質なプロセッサのほか、 キャッシュなどのメモリ、高機能な入出力プ ロセッサを格納することができる。これらの 機能ブロックは、相互に高帯域なバスなどで 結合され、効率的な協調実行が可能となって いる。これらのマルチコアプロセッサを効率 よく実行できる仮想化方式を検討する。特に、 同一チップ内のプロセッサを論理化された スレッドなどの実行実体として提供する軽 量かつ高速なプロセス・スレッド管理の方式 を研究する。マルチコアプロセッサの内部は、 CPU と DSP のような異質な計算機構を有す ることもあるが、コアの構成ごとによって使 えるハードウェア資源が異なるため、要求さ れる機能をハードウェアによる実装も可能 な場合もあれば、ソフトウェアによるエミュ レーションを行う必要がある場合もある。本 研究では、これらマルチコアのプロセッサの

構成によって変化するソフトウェアの構成を、マルチコアプロセッサの実装を隠蔽するような仮想化方式を考察することにより、コア独立の一元化・統一された実行環境を提供する方式を明らかにする。

(2) 実行時にシステム構成を変更可能なリコンフィギャラブルアーキテクチャに適した基盤ソフトウェア、具体的には OS が提供する各種仮想化機能の解明と機構の確立

ハードウェア構成を実行時コンテキスト に含むことにより、動的に再構成可能なハー ドウェアを仮想化する方式を中心とする OS の研究を行う。通常、プロセスやスレッドは 伝統的な CPU・メモリ・入出力の管理情報を コンテキストに含み、コンテキストスイッチ と同時にこれら実行時情報をもとに実装置 を割り当てる。コンテキストは本質的な情報 である。 最新の FPGA には、100 命令程度で ハードウェア構成情報をスイッチできる機 能を持つものが現れている。本研究では、リ コンフィギャラブルなハードウェアの構成 情報を、リコンフィギャラブルコンテキスト として OS に導入することを最大の研究課題 とする。特に、コンテキストとして持つべき リコンフギャラブルな構成情報の解明、プロ セスやスレッドコンテキストブロックへの 格納方式と切替の方式を明らかにする。

(3) マルチコア、リコンフィギャラブルプロセッサに適合するプログラミング環境の検討

マルチコアプロセッサやリコンフィギャラブルアーキテクチャを利用する場合、プロセッサに固有な資源に応じたプログラミングが必要となるが、エミュレーション方式、VMを用いることにより仮想化された資源をプログラマに提供する。

#### 4. 研究成果

(1) マルチコアプロセッサ向けの資源管理方式とその機構の実装

Cell B.E.のような異質なコアを持つプロセッサについては、マイクロカーネル方式ののSアーキテクチャを採用し、全コアで透過的かつ高効率な資源管理方式を提案し、MINIX3を用いて実装を行った。この結果、Cell B.E.のPPEとSPEで同じ方式でカーネル処理から応用プロセスの実行が可能となり、一元かにマルチコアの利用が可能な方式を明らかにした。また、均質なコアを持つプロセッサについては、複数のOSが連携し協調して実しいては、複数のOSが連携し協調して実した。また、均質なコアを持つプロセッサについては、複数のOSが連携し協調して実した。また、均質の可能な方式を明らかにするの特質とOSの特質の両面に対し、適ファの特質とOSの特質の両面に対し、適フェースを持つ資源管理方式を明らかにする

ことができた。

(2) リコンフィギャラブルプロセッサを管理する OS の資源管理方式とのその試作リコンギャラブルプロセッサの制御方式をして、OS のデバイスドライバにより各種源を仮想化すると同時に応用プログラムを設定を損害を提案し、試作を行った。引いたリコンフィギャラブルプロセッサを制御定にないままプログラミングを持たないままプログラムから動した API を用いて、応用プログラミングした API を用いて、応用プログラミングもあ方式を提案できた。

(3) マルチコア、リコンフィギャラブルプロ セッサのプログラミング環境の構築

マルチコア、リコンフィギャラブルプロセッサは、ハードウェア依存性が高く、移植可能なソフトウェアアーキテクチャの構築は困難であった。本研究では、VM ベースのプログラミング環境、QEMU などを用いたハードウェアエミュレーション方式、ベアマシン上での言語処理系を直接実行する方式を提案、実装し、各方式の長短を検討することができた。

以上を通して、応用ソフトウェアに適応的でかつハードウェア独立な、マルチコア、リコンフィギャラブル・アーキテクチャ向けの基盤ソフトウェア、特に、OS、ランタイムルーチンの資源管理方式とプログラミング環境の機能と構成を明らかにすることができった。マルチコア、リコンギャラブルプロセシサは、現在も、そして、今後も方式をより、今回提案、検討した方式の有効性を明らかにすることが今後の課題である。

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## [雑誌論文](計15件)

磯部 泰徳,佐藤 未来子,並木 美太郎, ホモジニアスマルチコア CPU における異種 OS 間の連携機構の試作,情報処理学会「システムソフトウェアとオペレーティング・システム」第 111 回研究報告, Vol. 2009-OS-111, No. 17, pp. 1-8, 2009年,査読無

太田 篤志,並木 美太郎, Cell/B.E.の SPE 向け軽量カーネルの設計と試作,情報処理学会「システムソフトウェアとオペレーティング・システム」第 111 回研究報告,

Vol.2009-OS-111, No.37, pp.1-8, 2009年, 香読無

<u>並木 美太郎</u>, 久野 靖, 兼宗 進, 早川 栄一, ユビキタス・組込みシステムにおけ るオブジェクト指向言語 Dolittle の実装, 第 50 回プログラミングシンポジウム予稿 集, pp.61-72, 2009 年, 査読有

野尻 祐亮,<u>並木 美太郎</u>,マイクロカーネル方式による Cell/B.E. 向け OS 構成法の提案と MINIX 3 による実現,情報処理学会「システムソフトウェアとオペレーティング・システム」第 110 回研究報告,Vol.2009-OS-110,pp.91-98,2009 年,査読無

野尻 祐亮, 並木 美太郎, Cell/B.E. への MINIX 3 の 移植と SPE 管理方式の検討, JSASS(Summer Joint Symposium for Advanced System Software)2008 報告集, Vol.2, No.1, pp.25-pp.36, 2008 年, 査読無

浅野 一成,並木 美太郎, PerlMachine の設計と実装, JSASS(Summer Joint Symposium for Advanced System Software)2008 報告集, Vol.2, No.1, pp.91-pp.106, 2008年,査読無

松崎 泰裕,<u>並木 美太郎</u>,携帯向け Scheme 処理系の Sun SPOT への応用, JSASS(Summer Joint Symposium for Advanced System Software)2008 報告集, Vol.2, No.1, pp.107-pp.116, 2008年,査 読無

川口 直也,並木 美太郎, JavaVM による x86 ユーザーモードエミュレーション機構の実装と評価,情報処理学会第 109 回「システムソフトウェアとオペレーティング・システム」2008 年並列/分散/協調処理に関する『佐賀』サマー・ワークショップ(SWoPP 佐賀 2008), Vol.2008-0S-109,pp.77-pp.84,2008 年,査読無

野尻 祐亮, <u>並木 美太郎</u>, MINIX 3 の Cell B.E. への移植と SPE の管理方式の検討, 情報処理学会「システムソフトウェアとオペレーティング・システム」第 108 回研究報告, Vol.2008-OS-108, pp.83-90, 2008 年, 査読無

松崎 泰裕, 並木 美太郎, プログラムをマイグレーションできる携帯電話向けのScheme 言語処理系, 情報処理学会「コンピュータシステムシンポジウム 2007」論文集, Vol.2007, No.14, pp.59-68, 2007 年, 査 読有

笹田耕一,松本行弘,前田敦司,<u>並木美</u>太郎,Ruby 用仮想マシン YARV における並列実行スレッドの実装,情報処理学会論文誌,Vol.48,No.SIG10(PR033),pp.1-16,2007年,査読有

松尾 和弥, 佐藤 未来子, 並木 美太郎,

省電力システムのための QEMU を用いたシステム評価環境の実現, SACSIS(先進的計算基盤シンポジウム)2007, Vol.2007, No.5, pp.61-68, 2007年, 査読有

浅野 一成, 並木 美太郎, Per IOS の試作と評価, 情報処理学会「システムソフトウェアとオペレーティング・システム」研究会第 106 回研究報告, 2007 年並列/分散/協調処理に関する『旭川』サマー・ワークショッ プ (SWOPP 旭 川 2007), Vol. 2007-OS-106(12), pp.87-94, 2007年, 査読無

松崎泰裕,<u>並木美太郎</u>,携帯電話向けのマイグレーション可能な Scheme 言語処理系,情報処理学会「システムソフトウェアとオペレーティング・システム」研究会第106回研究報告,2007年並列/分散/協調処理に関する『旭川』サマー・ワークショップ (SWoPP 旭 川 2007), Vol.2007-OS-106(15), pp.111-118,2007年,査読無

松尾 和弥, 佐藤 未来子, <u>並木 美太郎</u>, QEMU を用いた命令, アドレストレーサの実現, 情報処理学会「システムソフトウェアとオペレーティング・システム」第 105 回研究報告, Vol. 2007-0S-105, pp. 39-46, 2007年, 査読無

## [学会発表](計9件)

高畠 和幸, 磯部 泰徳, 佐藤 未来子, 並 木美太郎, Linux における動的再構成可能 プロセッサの実行管理機構の試作, 情報 処理学会第 71 回全国大会, 6K-4, 2009 年 3月, 立命館大学(滋賀県)

盛合 智紀,並木 美太郎,小型組込み機器を対象とした分散システムの構築法とその言語処理系の試作,情報処理学会第71回全国大会,1L-5,2009年3月,立命館大学(滋賀県)

野尻祐亮,並木美太郎, Cell/B.E. への MINIX 3 の移植とヘテロジニアスマルチコ アプロセッサ上でのプロセス管理方式の 実現,情報処理学会第 71 回全国大会,6K-3,2009年3月,立命館大学(滋賀県) 浅野 一成,並木美太郎,プログラミング言語 Perlによるオペレーティングシステム構成法の研究,情報処理学会第 71 回全国大会,1K-7,2009年3月,立命館大学(滋賀県)

磯部 泰徳, 佐藤 未来子, 並木 美太郎, 汎用ホモジニアスマルチコアにおける異種 0S の連携機構, 情報処理学会第71回全国大会, 6K-5, 2009年3月, 立命館大学(滋賀県)

北原 悠, 佐藤 未来子, 磯部 泰徳, <u>並木</u> <u>美太郎</u>, マルチコアプロセッサにおける スクラッチパッドメモリを用いたメモリ 管理システムの試作,情報処理学会第 71 回全国大会,6K-6,2009年3月,立命館大学(滋賀県)

佐藤未来子他 6 名(7 番目), 汎用ホモジニアスコアプロセッサにおける 0S とスレッドライブラリ, 情報処理学会第 20 回コンピュータシステムシンポジウム, ポスター セッション ン, http://www.ipsj.or.jp/sig/os/index.php?plugin=attach&refer=ComSys2008%2Fposter&openfile=ComSys2008-P03.pdf, 2008年11月, 田町イノベーションセンター(東京都)

太田 篤志,並木 美太郎, Cell B.E.の SPE 向け OS の設計とスレッド管理の開発,情報処理学会第 70 回全国大会, 3P-8, 2008年3月,筑波大学(茨城県)

磯部 泰徳, 佐藤 未来子, 並木 美太郎, マルチコアプロセッサにおけるスレッド ライブラリと OS の連携方式の設計, 情報 処理学会第 70 回全国大会, 3P-9, 2008 年 3月, 筑波大学(茨城県)

#### 6.研究組織

## (1)研究代表者

並木 美太郎(Namiki Mitaro)

東京農工大学・大学院共生科学技術研究 院・教授

研究者番号:10208077

### (2)研究分担者

中條 拓伯(Nakajo Hironori)

東京農工大学・大学院共生科学技術研究院・助教授

研究者番号:80217736

品川 高廣(Shinagawa Takahiro)

東京農工大学・大学院共生科学技術研究院・助手

研究者番号:40361745

# (3)連携研究者

なし