# 科学研究費助成事業 研究成果報告書

令和 4年 5月24日現在

機関番号: 32407

研究種目: 基盤研究(C)(一般)

研究期間: 2018~2021

課題番号: 18K04177

研究課題名(和文)零サイドローブ特性を持つパルス圧縮符号の探求と応用

研究課題名(英文)Search and Application of Pulse Compression Codes with Zero or Small Sidelobe Characteristics

研究代表者

高瀬 浩史 (Takase, Hiroshi)

日本工業大学・基幹工学部・教授

研究者番号:80306266

交付決定額(研究期間全体):(直接経費) 3,300,000円

研究成果の概要(和文):本研究では,サイドローブが零または最小となる幅広パルス圧縮符号を探索するために,符号探索を高速で行う方法について検討を行った.高速な計算を実現するためにGPGPUやFPGA,最適化手法などを用いた.その結果,従来は探索できなかった符号長での探索を行うことができ,従来符号よりサイドローブの小さな符号を見出すことができた.また,それらの符号の特性評価について計算機シミュレーションを行い,有効性を確認した.

研究成果の学術的意義や社会的意義本研究で提案する幅広パルス圧縮符号は,従来符号に比べ符号長毎の符号の数が多いという特徴があることから,干渉がある状況での符号の切り替えなどによる対干渉性能にも優れていると考えられる.このような特徴を有する提案符号を探索,発見し,その特性を明らかにすることでレーダの探知性能向上が期待できる.そして,レーダを用いた計測によって,航空管制,環境計測,宇宙科学,気象学など多くの研究分野での派生的な効果が期待される.本研究では,レーダへの適用を想定しているが,符号自体は無線通信技術やセキュリティ技術などスペクトラム拡散技術の符号であることから,他分野における様々な応用システムでの性能向上も期待できる.

研究成果の概要(英文): In this study, we investigated a fast code search method to find proposed pulse compression codes with zero or small sidelobe. GPGPUs, FPGAs, and optimization methods were used to achieve high-speed computation. As a result, we were able to search for codes with code lengths that could not be searched so far, and to find proposed codes with smaller sidelobe than conventional codes. Computer simulations were performed to evaluate the characteristics of these codes, and their effectiveness was confirmed.

研究分野: 電気電子工学

キーワード: パルス圧縮 レーダ 符号 サイドローブ

#### 1.研究開始当初の背景

レーダに求められる重要な性能要件として,距離分解能の向上と探知距離の増大がある,レー ダは雑音などに埋もれた微弱な反射信号を検出しなければならないが,送信信号として狭帯域 パルスを使うことにより受信機雑音を減らすことができる.しかし,狭帯域パルスでは送信パル ス幅が大きくなるため十分な距離分解能を得ることができず, 距離分解能を向上させるために は送信パルス幅を狭くする必要がある.これは距離分解能がパルス幅により決まるためで,また 帯域幅とパルス幅には反比例の関係があることに基づいている .そして ,多くのレーダでは尖頭 送信電力には制約があるため、探知距離を増大させるためには送信パルス幅を広くする必要が ある、一方、距離分解能を向上させるためには送信パルス幅を狭くする必要があるが、平均送信 電力が小さくなり探知距離が短くなってしまう.これらは互いに相反する問題であるが,この問 題を解決する技術としてパルス圧縮がある.パルス圧縮はパルス幅の長い送信信号に変調を施 し 受信時に自己相関処理を行うことで 距離分解能と探知距離の向上を実現することができる. 数多くのレーダでパルス圧縮が用いられており,近年はレーダ信号処理のディジタル化が進み, 送信信号の変調に用いるパルス圧縮符号の重要性が増している.しかし,パルス圧縮後の受信信 号にはメインローブの他に探知には不要なサイドローブが発生する問題がある.このサイドロ ーブは変調に用いるパルス圧縮符号によりその大きさが決まるため,サイドローブの小さなパ ルス圧縮符号がいろいろと研究されている. 古くから知られている Barker 符号, 最適2値符号 および M 系列などはサイドローブの比較的小さな符号であるが,レーダの性能を向上させるた めには更なるサイドローブを低減できる符号が必要である.

## 2.研究の目的

本研究では,レーダの探知性能向上を実現するために,サイドローブが零または最小となる幅広パルス圧縮符号を符号探索により見出し,それらの符号の持つ特性を明らかにすることを目的とする.

パルス圧縮符号としては、現在のところ Barker 符号、最適2値符号および M 系列などがレーダや通信システムなどで用いられている状況である。研究代表者らが提案している幅広パルス圧縮符号は、パルス圧縮の原理を拡張することにより実現したものである。提案する幅広パルス圧縮符号は、従来符号に比べサイドローブが零、または小さいという優れたサイドローブ特性を有することがこれまでの研究から分かっている。近年高分解能レーダの要求が高いことから、圧縮比の大きな、すなわち符号長の長い幅広パルス圧縮符号が必要である。しかし、符号の探索には莫大な時間を要するため、高速で符号探索を行える仕組みを確立する必要がある。そこで、スパコンや GPGPU、FPGA(Field Programmable Gate Array)のような高性能なハードウェアを用いるほか、探索処理のアルゴリズムを工夫することで、従来符号には見られないサイドローブが零または最小となる極めて優れた特性を有する幅広パルス圧縮符号を見出すことができる可能性がある。

### 3.研究の方法

本研究では ,GPGPU や FPGA ,最適化アルゴリズム等を用いる符号探索方法について研究を遂行した.また,探索で見つかった符号の特性評価を行った.

## (1)幅広パルス圧縮符号の探索方法の開発

本研究では,幅広パルス圧縮符号を対象として符号探索を行う.2値符号の場合,符号の組合せは符号長をNとすると 2N-1個となり,指数関数オーダで組合せ数が増大する.本研究では,符号の全ての組合せについて,自己相関関数を計算しピークサイドローブレベルを求める.このとき,自己相関関数は積和演算となり,この演算量は符号長の長さに基づくことから,この処理においても符号長が長くなるにつれ計算時間が増大する.そこで,スパコンやGPGPU,FPGA,最適化アルゴリズム等を用いる方法により,この自己相関関数を含む符号探索プログラムの開発を行う.

## (2)符号の特性評価シミュレーション

探索により見つかった符号の特性評価として,自己相関特性やドップラー周波数特性について計算機シミュレーションを実施する.

#### 4. 研究成果

## (1)幅広パルス圧縮符号の探索方法の開発

当初はスパコンを用いた並列計算による符号探索アルゴリズムを検討したが,予想していた探索性能が得られなかった.そこで,GPGPUを搭載した計算機やクラウドコンピューティング環境を利用することにより符号探索アルゴリズムの改良を行い,探索の高速化を図れることを確認できた.

しかし,長い符号長の符号探索を行うには計算能力がまだ十分ではないことから,さらなる探

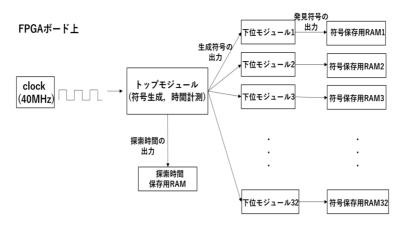

図1 FPGA の内部構成

索処理の高速化を図るため,組合せ最適化アルゴリズムの適用についても検討を行った.符号探索に分散遺伝的アルゴリズムを適用することにより新しい符号を発見することができた.

また、この最適化アルゴリズムの場合は、符号の全ての組合せを調べたことにはならず、全探索の方法として、FPGA を用いた符号探索処理を検討した。FPGA はハードウェア記述言語を用いて論理回路を構成するものであり、本研究においては符号探索処理をハードウェアとして実現することが可能となる。FPGA を用いるメリットとしては、ハードウェアとして探索処理を実行するため高速な計算処理が期待できる。本研究では FPGA を用いて符号探索処理をハードウェアとして実装することができた。FPGA の内部には論理回路の集合体であるモジュールを複数構成できる。本研究では、FPGA 1台にトップモジュールと下位モジュール 32 個を構成した。FPGA の内部構成を図 1 に示す。トップモジュールでは各符号長において符号生成をしてから探索範囲を分割し、各下位モジュールに符号を出力する。下位モジュールでは、トップモジュールから入力された符号に自己相関処理を施し、その後、メインローブおよびサイドローブのチェックを行い、見つかった符号を FPGA ボード上の RAM に出力する。これを実際には複数台で並列化を構成

し高速な符号探索を実現することが可能となった.

(a) 自己相関特性

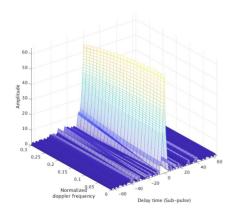

(b) ドップラー周波数特性

## 図2 提案符号の特性評価(符号長64)

### (2)符号の特性評価シミュレーション

# (a) 自己相関特性

自己相関特性は、発見された符号の自己相関関数を計算し、メインローブのピーク値とサイドローブのピーク値の比を評価する。図 2(a)は本研究で見つかった符号の自己相関特性を示したものである。メインローブとサイドローブの比を評価したところ、従来符号と比較して約8dBも低減できる符号であることを確認した。

## (b) ドップラー周波数特性

(a)の自己相関特性は静止目標の場合での性能であるが、レーダでは目標物が移動体の場合も考えられ、そのとき受信する反射信号にはドップラー偏移が含まれることから、ドップラー偏移の影響を考慮したサイドローブ特性にリステーにでも評価を行った。図2(b)は受信信号にドップラー偏移を加え、ドップラー周波数を変化させたシミュレーション結果の一例である、ドップラー偏移のある状況においても提案符の有する低サイドローブの特徴は維持されていることが確認できた。

本研究では,低サイドローブ特性を有する幅広パルス圧縮符号を探索するために,その探索方法の高速化について様々なアプローチで取り組んだ結果,特に FPGA を用いた探索方法で高速化の足掛かりとなる成果を得ることができた.

以上の成果を踏まえ、今後は FPGA の並列化 を増やし更なる高速化を目指すことを考えて いる.

#### 5 . 主な発表論文等

〔雑誌論文〕 計0件

| ( 当人 32 丰 ) | 計3件(うち切待議演 | 0件/シナ団欧当人 | 1 I/H > |

|-------------|------------|-----------|---------|

|             |            |           |         |

| 1 | 沯 | ٤ŧ | 耒 | 者 | 名 |

|---|---|----|---|---|---|

|   |   |    |   |   |   |

橋本尚樹,高瀬浩史,神力正宣

# 2 . 発表標題

分散遺伝的アルゴリズムを用いた幅広2値符号の探索

#### 3 . 学会等名

平成31年電気学会電子・情報・システム部門大会

#### 4.発表年

2019年

#### 1.発表者名

Hiroshi Takase, Masanori Shinriki

#### 2 . 発表標題

Search of Binary Codes Compressed to Several Sub-pulses

## 3 . 学会等名

IEEE International Conference on Microwave, Communication, Antennas & Electronic Systems 2019 (国際学会)

#### 4.発表年

2019年

## 1.発表者名

木村圭吾,神林龍,高瀬浩史

## 2 . 発表標題

複数のFPGAを用いた幅広2値符号の探索

# 3 . 学会等名

令和4年電気学会全国大会

## 4.発表年

2022年

#### 〔図書〕 計0件

〔産業財産権〕

〔その他〕

| _6 | . 研究組織                    |                       |    |

|----|---------------------------|-----------------------|----|

|    | 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |

## 7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

# 8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|