#### 研究成果報告書 科学研究費助成事業

今和 3 年 5 月 6 日現在

機関番号: 12612 研究種目: 若手研究 研究期間: 2018~2020

課題番号: 18K18022

研究課題名(和文)パケット処理キャッシュを用いたパケット予測処理に関する研究

研究課題名(英文) Response Prediction for Packet Processing Caches

#### 研究代表者

八巻 隼人 (Yamaki, Hayato)

電気通信大学・大学院情報理工学研究科・助教

研究者番号:20782197

交付決定額(研究期間全体):(直接経費) 2.800.000円

研究成果の概要(和文):本研究では,インターネットルータのテーブル検索を高速化・省電力化するパケット処理キャッシュ(PPC: Packet Processing Cache)において,近い将来に到着するパケットを予測して事前にテーブル検索を行い,その結果をキャッシュするパケット予測処理機構を提案した.研究成果として,近年研究が進められている多階層PPCに本機構を適用することで,従来の1.38倍のスループットを74%の消費電力で実現できることを明らかにした.また,提案機構のハードウェア実装にかかるオーバーヘッドはPPCの実装回路全体の1%程度であることを示した.

研究成果の学術的意義や社会的意義本研究成果により,これまで1Tbps程度の処理速度が限界と見込まれていたインターネットルータのテーブル検索において,同程度の消費電力で1.5Tbps程度の処理速度を実現できることが示された.また,提案機構をハードウェア実装する際のハードウェアコスト量についても明らかとなった.本研究成果が波及することで,1Tbps以上の処理速度を備えたルータをこれまでよりも低コストに実現することが期待できる.

研究成果の概要(英文): In this research, we proposed a packet prediction method for PPCs (Packet Processing Caches), which increased the table-lookup throughput of an Internet router and reduced its power consumption. The method predicts packets which may arrive in the near future and caches their table lookup results by executing the table lookups in advance. As a result of this research, it was shown that the proposed method can achieve 1.38x table-lookup throughput with 74% power consumption compared to the conventional PPCs when the proposed method was adopted to the multi-layer PPCs, which were recently studied. Furthermore, it was shown that the proposed method can be implemented with approximately 1% of the whole circuit of a PPC.

研究分野:計算機システム

キーワード: インターネットルータ パケット処理キャッシュ 省電力 高スループット パケット予測

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

## 1.研究開始当初の背景

IoT(Internet of Things)やクラウドアプリケーションの普及,動画や画像データの高品質化に伴う近年のインターネット通信量の急激な増加により,ルータ,特に通信が集約するコア網に設置されるコアルータに要求される通信データの処理スループットは増加の一途を辿っている.また,コアルータにおいては通信データの処理にかかる消費電力の増大も問題となっており,コアルータには,これまで以上の処理スループットをより省電力に実現する必要に迫られている.従来のコアルータは,Ternary Content Addressable Memory(TCAM)と呼ばれる,1サイクルでデータ検索を完了するメモリを用い,パケット処理を高速化してきた.ルータでは,パケットの次到達ノードやフィルタリングルールといった情報が各種テーブル(e.g.,ルーティングテーブル,ACL(Access Control List))としてメモリに格納されており,1パケットの処理にこれら複数テーブルへの検索を要する.100~400Gbpsの近年の広帯域ネットワークで求められる処理速度は 1~5ns/パケット程度であることから,近年のコアルータはこれらテーブルをDRAM(Dynamic Random Access Memory)ではなく TCAM に格納している.しかしながら,TCAM には以下の2つの欠点がある.

- 1. ルータ消費電力全体の 40%程度を占める高い消費電力

- 2. 数百 GHz 程度の現行 TCAM 製品では,数 ns/検索が限界

上記の欠点から,TCAM ベースのパケット処理技術はこれ以上のトラフィック増加に対応できない.

上述した問題点を改善しうる技術としてパケット処理キャッシュ(Packet Processing Cache: PPC)がある.PPC は、パケット処理におけるテーブル検索結果がフロー情報(送/受信 IP アドレス,送/受信ポート番号,プロトコル番号の 5 値)により決定されることに着目し,フローの初回パケットのテーブル検索結果を小規模だが高速かつ低消費電力なキャッシュメモリに保存する.以降の同一フローに属するパケットは,キャッシュ内に同一フローのエントリがあった場合(これをキャッシュヒットと呼ぶ),TCAM を介さずテーブル検索を完了できる.PPC は,TCAM ベースの既存手法に対し処理スループットを低下させることなく併用可能であり,TCAM に比ベキャッシュメモリのレイテンシは 1/10 程度,消費電力は 1/50 程度であることから,高いキャッシュヒット率を得るほど,パケット処理の高スループット化,省電力化が期待できる.

# 2.研究の目的

PPC では、レイテンシの観点から 32KB 程度の小規模なキャッシュメモリを用いることが望ましく、現状では 70%程度のヒット率しか得られない、そこで、本研究では PPC におけるキャッシュのヒット率向上を目的とし、後続するフローの予測を行い、先に当該フローのキャッシュエントリを用意しておくことで初期参照ミスを削減する手法を提案する、初期参照ミスはキャッシュデータの初回参照時に生じるミスであり、一般的なプロセッサキャッシュ等ではミス全体の 1%程度だが、PPC においては全体の半数を占める、これはすなわち、初期参照ミスの削減によりヒット率を 70%から 85%まで向上可能となることを示している。

## 3.研究の方法

本研究では目標 1,目標 2の 2つを明らかとすることを目標とし,以下の方法について研究を 進める.

(目標 1: PPC におけるキャッシュヒット率の向上) 具体的な数値として,現状の70%から80% までヒット率を向上させることを目標とする.なお,PPC を用いた処理性能はミス率により決定され(業績[2-1]で定式化),目標を達成できた場合には従来のPPCに対し,パケット処理スループットが1.50倍に,テーブル検索における消費電力が0.67倍に改善される.

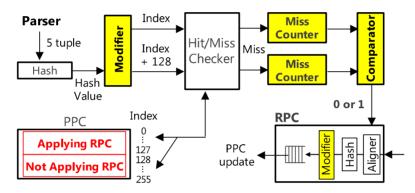

(方法1: 応答フロー予測手法の提案) インターネットアプリケーションの多くは,サーバ・クライアント間での双方向通信によりサービスを実現する.この際,PPC ではクライアントからサーバに向けた要求フローとサーバからクライアントに向けた応答フローにより 2 度の初期参照ミスが生じる.そこで,要求フローの送信元と宛先情報を入れ替えることで応答フローを予測し,予測フローの処理結果を事前にキャッシュしておくことで初期参照ミスの発生を防ぐ.

応答フローのテーブル検索結果は,例えば,ルーティングテーブルならば要求フローの送信元から,ACL ならば要求フローのフィルタリング結果から推測可能である.従って,予測フローの処理のために新たにTCAMを検索する必要はなく,消費電力は増大しない.

(目標2:提案機構を含めた PPC のハードウェアコストを評価)提案機構は処理遅延の観点からハードウェア実装されることが望ましい.そこで,提案機構や TCAM,各種キューを含めた PPC 全体の動作確認および回路規模,消費電力,最大動作遅延の測定を行う.

(方法2:ハードウェアシミュレーションによる回路規模評価)ハードウェア記述言語 Verilog-HDL や論理合成ツール Synopsys Design Compiler, メモリ評価ツール CACTI 等を用いて,提案機構を含む PPC をハードウェア実装し,その回路規模および最大動作遅延,消費電力を見積もる.

# 4. 研究成果

方法 1 に示した通り PPC にパケット予測処理機構を実装した.提案手法を含む PPC 全体のアーキテクチャを図 1 に示す.実ネットワークトレースを用いた評価により,従来の PPC において22.1%であった PPC ミス率を 19.5%に改善できることを示した.これは,従来の 1.14 倍のスループット向上,12.1%の消費電力削減となる.本研究では,当初計画していたこれらの評価に加え,近年研究が進められている多階層 PPC へのパケット予測処理機構の実装についても検討した.その結果,これまでの多階層 PPC における PPC ミス率 4.67%から 3.38%まで改善できることを示した.これにより,スループットを 1,090Gbps から 1,504Gbps へ 1.38 倍向上し,消費電力を2.62nJ/packet から 1.93nJ/packet へ 25.8%削減できることが明らかとなった.

方法2で予定したハードウェアコスト評価についても実施した.その結果,PPC全体の実装回路規模0.230 miに対する提案手法の実装回路規模は0.000427 mi(0.18%)であり,十分に小さい回路規模のオーバーヘッドによりパケット予測処理機構を実装できることが明らかとなった.

これらの研究成果は,査読付論文誌4件,国際会議発表2件,国内学会発表2件において発表された.

図1.パケット予測処理機構を含む PPC のアーキテクチャ

# 5 . 主な発表論文等

〔雑誌論文〕 計4件(うち査読付論文 4件/うち国際共著 0件/うちオープンアクセス 0件)

| [雑誌論文] 計4件(うち査読付論文 4件/うち国際共著 0件/うちオープンアクセス 0件)                                          |                     |

|-----------------------------------------------------------------------------------------|---------------------|

| 1 . 著者名                                                                                 | 4.巻                 |

| Yamaki Hayato、Nishi Hiroaki、Miwa Shinobu、Honda Hiroki                                   | E103.D              |

| 2 . 論文標題                                                                                | 5 . 発行年             |

| RPC: An Approach for Reducing Compulsory Misses in Packet Processing Cache              | 2020年               |

| 3.雑誌名<br>IEICE Transactions on Information and Systems                                  | 6.最初と最後の頁 2590~2599 |

| 掲載論文のDOI(デジタルオブジェクト識別子)                                                                 | 査読の有無               |

| 10.1587/transinf.2020EDP7035                                                            | 有                   |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                  | 国際共著                |

| 1 . 著者名                                                                                 | 4.巻                 |

| Yamaki Hayato                                                                           | 33                  |

| 2.論文標題                                                                                  | 5 . 発行年             |

| Effective cache replacement policy for packet processing cache                          | 2020年               |

| 3.雑誌名                                                                                   | 6 . 最初と最後の頁         |

| International Journal of Communication Systems                                          | e4526~e4526         |

| 掲載論文のDOI(デジタルオプジェクト識別子)<br>10.1002/dac.4526                                             | <br>査読の有無<br>有      |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                  | 国際共著                |

| 1 . 著者名<br>Yamaki Hayato                                                                | 4.巻                 |

| 2 . 論文標題                                                                                | 5 . 発行年             |

| Hybrid Memory Design for High-Throughput and Low-Power Table Lookup in Internet Routers | 2020年               |

| 3.雑誌名                                                                                   | 6.最初と最後の頁           |

| International Journal of Advanced Computer Science and Applications                     | 61~69               |

| 掲載論文のDOI(デジタルオブジェクト識別子)<br>10.14569/IJACSA.2020.0110608                                 | <br>  査読の有無<br>  有  |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                  | 国際共著                |

| 1 . 著者名                                                                                 | 4.巻                 |

| Yamaki Hayato                                                                           | 11                  |

| 2 . 論文標題                                                                                | 5 . 発行年             |

| Efficient Cache Architecture for Table Lookups in an Internet Router                    | 2020年               |

| 3.雑誌名                                                                                   | 6.最初と最後の頁           |

| International Journal of Advanced Computer Science and Applications                     | 664~672             |

| 掲載論文のDOI(デジタルオブジェクト識別子)                                                                 | 査読の有無               |

| 10.14569/IJACSA.2020.0110581                                                            | 有                   |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                  | 国際共著                |

| 〔学会発表〕 計4件(うち招待講演 0件/うち国際学会 2件)                                                       |

|---------------------------------------------------------------------------------------|

| 1.発表者名<br>長田大樹,田中京介,八巻隼人,三輪忍,本多弘樹,五島正裕                                                |

| 2 . 発表標題<br>Rout ing/ARP/ACL/QoSごとのテーブル分離パケット処理キャッシュ                                  |

| 3 . 学会等名<br>情報処理学会研究報告 2021-ARC-244                                                   |

| 4 . 発表年<br>2021年                                                                      |

| 1 . 発表者名<br>Hayato Yamaki                                                             |

| 2. 発表標題<br>Efficient Cache Architecture for Packet Processing in Internet Routers     |

| 3 . 学会等名<br>2020 Future of Information and Communication Conference (FICC 2020)(国際学会) |

| 4 . 発表年<br>2020年                                                                      |

| 1 . 発表者名<br>Kyosuke Tanaka, Hayato Yamaki, Shinobu Miwa and Hiroki Honda              |

| 2.発表標題<br>Multi-Level Packet Processing Caches                                        |

| 3 . 学会等名<br>IEEE Symposium on Low-Power and High-Speed Chips and Systems (国際学会)       |

| 4.発表年<br>2019年                                                                        |

| 1.発表者名<br>田中京介,八巻隼人,三輪忍,本多弘樹                                                          |

| 2.発表標題<br>1Tbps実現に向けたルータのメモリ階層の最適化                                                    |

| 3 . 学会等名<br>第225回システム・アーキテクチャ研究発表会                                                    |

| 4 . 発表年<br>2018年                                                                      |

|                                                                                       |

〔図書〕 計0件

〔産業財産権〕

〔その他〕

-

6.研究組織

| · K170/14/14/             |                       |    |

|---------------------------|-----------------------|----|

| 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |

7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|