### 科学研究費補助金研究成果報告書

平成21年 4月22日現在

研究種目:基盤研究(B)(一般) 研究期間:2007~2008年度

課題番号:19360132

研究課題名(和文) 薄平面形状に基づく高電力密度インバータの開発

研究課題名(英文) Development of a High Power Density Inverter based on Thin Plane Form. 研究代表者

清水 敏久 (SHIMIZU TOSHIHISA)

首都大学東京・大学院理工学研究科・教授

研究者番号:30254155

研究成果の概要:次世代半導体として期待されるシリコンカーバイド(SiC)スイッチング素子を用いた高性能インバータの普及を目指して、究極の高効率化と小型化の両立が期待できる薄平面形状のインバータの基盤技術研究を行った。成果は、(1)厳密な損失計算による高密度設計に必要な損失計算手法の開発(2)高電力密度化の障害となる受動デバイス(けインダクタ)の損失計算・計測法の開発(3)最適設計手順の開発(4)最適な変調法の探索(5)高電力密度時に深刻化するノイズ障害防止策(6)薄平面形インバータの試作・評価である。

### 交付額

(金額単位:円)

|        | 直接経費         | 間接経費        | 合 計          |

|--------|--------------|-------------|--------------|

| 2007年度 | 9, 300, 000  | 2, 790. 000 | 12, 090, 000 |

| 2008年度 | 5, 100, 000  | 1, 530, 000 | 6, 630, 000  |

| 年度     |              |             |              |

| 年度     |              |             |              |

| 年度     |              |             |              |

| 総計     | 14, 400, 000 | 4. 320, 000 | 18, 720, 000 |

研究分野:パワーエレクトロニクス

科研費の分科・細目:電気電子工学・電力工学・電気機器工学

キーワード:省エネルギー、電気機器工学、新エネルギー、電気自動車、インバータ

#### 1. 研究開始当初の背景

地球環境や化石燃料枯渇などに対応した サステナビリティーに世界的関心が寄せら れている。なかでも、電気エネルギーを利用 して、社会生活の基盤である交通流、情報流、 を効率的かつ効果的に制御することが期待 される。そのための基盤技術である半導体電 力変換技術(パワーエレクトロニクス)には 一層の高度化が求められている。

電力変換装置の小型・高効率・低価格化の 指標として、近年、変換装置の電力密度(出 力電力/装置容積)が定義され、究極的な高 電力密度化に向けた研究開発が世界的に進 められている。しかし、従来のパワーエレクトロニクス技術の適用だけでは限界があるため、新たなアプローチに基づく技術開発が求められている。

### 2. 研究の目的

本研究者らは、SiC等の次世代パワーデバイスの低損失性能や高周波スイッチング技術を活用した高電力変換装置の高電力密度化研究の成果に基づいて、変換器構造に薄平面形状を導入することにより、これまでの限界を超える電力密度を実現する基盤技術を開発することを目的とする。

### 3. 研究の方法

本研究では、薄平面形状の高集積化実現に向けた下記の主要4課題を設定し、各研究グループが連携して効率的に開発を行った。

課題 1) SiCおよびSiデバイス「限界損失モデル」と「インダクタ等の受動部品の損失モデルを錬成した総合損失算定手法の開発

課題 2) 総合的な発生損失を最小化する制御方式に関する研究。

課題 3) 回路部品の配置、EMI等を考慮した薄平面形状の検討。

課題 4) 薄平面形状による更なる高電力密度化のための課題の抽出。

#### 4. 研究成果

(1) 課題1の成果

①インダクタ損失モデルの研究

・インダクタ損失計測評価装置の高性能化の研究

岩通計測(株)の協力の下で開発したインダクタ損失アナライザ(略称:ILA、図1参照)を用いて、計測精度の向上のための研究を行った。

第一は、インバータスイッチング周期ごとの損失計測結果のなかで、低周波損失の測定結果の誤差が多いことを見いだした。原因究明の結果、計測データの高速サンプリング時の量子化誤差が原因と判明したため、高速サンプリングレコーダの分解能と計測精度について知見をまとめた。

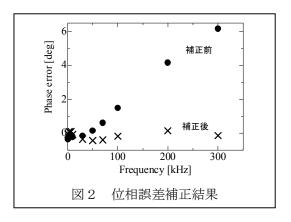

第二は、磁界強度と磁束密度の検出位相誤差の補正高精度検出の向上である。磁界強度と磁束密度の計測には、インダクタ電流波形と電圧波形の計測位相誤差を極小にすると電圧波形の計測位相誤差を極小に接出器と電圧検出器をで、広い周波数はに残存する位相特性の影響で、広い周波数はに変って位相誤差を減少させること株別であった。本研究では、岩通計測(株)がでの位相誤差を約1/10程度(6.0度IL和がでの位相誤差を約1/10程度(6.0度IL和の位相誤差を対1/10程度(6.0度IL和の位相誤差を対1/10程度(6.0度IL和の成果に基づいて具体的計測結果の評価検証を行った。本研究成果は学会発表(12)(17)(19)(22)として公表した。

### 低損失磁性体の損失評価

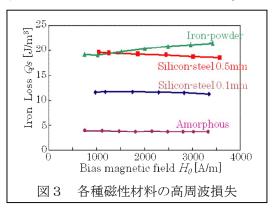

上記により向上した計測精度を活用して、これまで計測していた微細純鉄磁性体と比較して損失が少ないアモルファス磁性体およびパーマロイ磁性体の鉄損計測評価を行った。その結果、磁性体の種類に依存して次期バイアス条件下での磁界強度の変化に対する高周波損失の変化傾向いに違いが生じることを明らかにした(図3)。本研究成果は学会発表(11)(16)(21)として公表した。

# ・ヒステリシス損失とうず電流損失の分離計測

磁性体損失はヒステリシス損失とうず電 流損失に代表されるが、それぞれの損失配分 は励磁条件によって様々に変化する。とりわ けインバータ適用時の矩形波電圧励磁条件 での分離計測結果は報告されていなかった。 本研究では、本研究成果を応用して開発した ILA を用いて、矩形波励磁条件のマイナーヒ ステリシス曲線からうず電流損失とヒステ リシス損失、さらには、うず電流経路の等価 抵抗成分を分離計測する手法を開発し、珪素 鋼板を用いて分離計測を行い、その妥当性を 検証した。さらに、板圧形状の異なる珪素鋼 板のうず電流損失とヒステリシス損失の計 測評価を行った。その結果、ヒステリシス損 失は周波数に比例するというこれまでの通 説と同じ結果を得た(図4)。しかし、うず 電流損失は、通説は板厚の2乗に比例するが、 本計測の結果は通説とは異なる傾向を示す ことを見いだした(図5)。その詳細なメカニ

ズムの解明は今後の継続研究で明らかにする予定である。本研究成果は学会発表(1)(9)(10)として公表した。

### ・パワーデバイスの限界損失モデル

パワーデバイス損失のうち、とりわけスイ ッチング損失は主回路実装に伴って生じる 寄生配線インダクタンスや浮遊容量成分な どの寄生成分に依存して大きく変化するた め、正確な損失設計が困難であった。研究者 らは、寄生成分とスイッチング損失の関係を 定量化する限界損失モデル手法を既に考案 した。本研究では、この手法を用いて、3k W出力の絶縁型DC/ACコンバータにつ いて、インダクタ損失、回路配線構造に伴う 寄生成分、スイッチング周波数をふまえた最 適効率条件の探索計算を行った。その結果、 変換効率96%で電力密度7.8w/cc (従来の約2倍)を達成できることを示し、 本計算手法の有効性を立証した。本研究成果 は学会発表(8)(14)(18)として公表した。

### ②課題2の成果

課題1において、損失最小化計算のフレームが実現した。しかし、これを有効に活用するためには、各構成要素の損失モデルや制御方式と損失との関係などを明らかにする必要がある。そこで、以下の研究を行った。

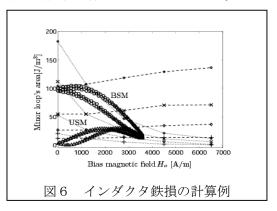

### ・<u>ロスマップと回路シミュレーションを連成</u>したインダクタ損失計算手法の開発

高電力密度化のために高周波スイッチングを行うと、インダクタ損失が相対的に増大する。課題1の成果としてインダクタ損失の計測評価は行えるようになったが、PWMインバータのフィルタインダクタのように、その損失が時間的に多様に変化する場合の損失の設計計算を行うことは困難であった。本研究では、基本的な磁性体損失(ロスマップ)と回路シミュレーションプログラムを連成して、フィルタインダクタの磁性体損失を厳密に計測する手法の開発を行った(図6)。本研究成果は論文(1)として発表した。

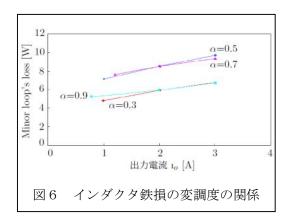

## ・<u>インバータの変調と動作状態に伴うインダ</u>クタ損失の変化

インバータで使用されるACフィルタインダクタ損失はPWM変調の方式や変調度、および負荷電流などのよって多様に変化することは知られていたが、その要因を詳細に分析した報告は行われていない。本研究で開発したインダクタの瞬時損失の計算と計測手法を利用して基本的な分析を行った。今回は単相インバータで変調方式をユニポーラ変調に限定し、変調度および負荷電流、負荷力率がインダクタ損失に与える影響について分析を行った。

その結果、(a) 直流電圧が一定の条件では変調度の変化に対するインダクタ損失は変調率が 0.5 近傍で最大になる。(b) 出力電圧一定の条件で変調度の変化(入力電圧が変化))にたいして、損失は入力電圧にほぼ比例して変化する。(c) 出力電流の変化にたいしては損失は若干増加するが、大幅な変化は見られない。

なお、この傾向は変調方式やインバータ相数 に依存して大きく変化することが見込まれ るので、今後継続して研究を行う予定である。 本研究成果は学会発表(2)として公表した。

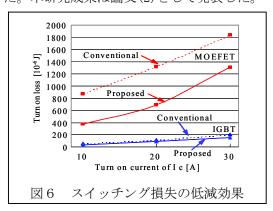

### ・CT帰還ゲート駆動回路の開発

高電力密度化を進めるには、インバータ主 回路の損失低減だけでなく、周辺回路の高効 率化も欠かせない。とりわけ、ゲート駆動回 路は主スイッチの高速スイッチング化と高 周波化に伴う消費電力の増加防止が望まれ ている。本研究では、主デバイスのスイッチ ング時のミラー効果に伴うミラーエネルギ 損失の増加とスイッチング損失の増加に着 目し、その両者を同時に改善する手法を提案 した。すなわち、ミラー容量と等価容量を持 つスナバコンデンサを主スイッチに並列に 接続し、主スイッチのターンオン時に生じる スナバコンデンサの放電電荷をCTを経由 してゲート駆動電力に回生することにより、 ミラー容量損失とスイッチング損失の低減 を実現している。本方式を適用することによ り、パワーMOSFETの場合、スイッチン グ損失(図6)とゲート駆動回路への供給電 力を約30%低減できることを明らかにし た。本研究成果は論文(2)として発表した。

### ③課題3の成果

課題1および2で開発した損失計算と制御方式に基づいて、具体的な装置構造を最適化手法を明らかにすることにより薄平面形の具体的形状のありかたについて研究を行った。

### ・回路部品の配置形状に伴う寄生成分の計測技術の開発

パワーデバイスのスイッチング時のサー ジ電圧とこれに伴う損失、あるいは次項で述 べるEMIノイズは、実際の部品配置と回路 配線パターンに起因する配線インダクタン スや寄生キャパシタンスの影響を強く受け るので、これら寄生成分の正確な把握に基づ いた装置設計が不可欠になる。また、高集積 装置では、回路配線パターンが短距離化・複 雑化するので、配線インダクタンスや寄生キ ャパシタンスの値を簡単な計算で求めるこ とは極めて困難である。そこで最近は3次元 電磁界解析を援用して回路配線パターンの 設計が導入されつつある。しかし、実際に製 作した回路基板の実効インダクタンスやキ ャパシタンスの値が設計値と一致している かを検証する術がなく、実動作試験で不具合 を発生する事例が発生している。

本研究では、具体的に製作したインバータ主回路基板を用いて、その配線パターンに伴う配線インダクタンスや寄生キャパシタンスをTDR(Time Domain Reflectometry)手法を応用して回路基板の接続端子から内部配線を計測する手法の研究を行った。今回は回路基板には降圧チョッパ回路について主スイッチにサージ電圧を生じさせる原因となる直流電源部と主スイッチ間の配線インダクタンスの計測を主体に実施した。

最初の課題は、計測精度の向上である。計測する配線インダクタンスに伴うインピーダンスがTDR測定に適した50Ωと比較して極めて小さく、測定精度が得られない。そこで、マイクロストリップ線路を用いたインピーダンス変換デバイスを開発し、これによって微少インダクタンスの正確な測定を実現した。

次の課題は、実際のチョッパ回路基板に複数分散した個々の配線インダクタンスを計測する手法の開発である。そこで、直流入力端子とその反対側のスイッチ出力端子の2カ所の外部端子からTDR計測を行うことにより、TDR反射波形の差分から複数の配線インダクタンスの分離計測を試みた。完全な分離には至っていないが、反射波形の解析精度を向上することにより、高精度化の目処が立った。本研究成果は学会発表(4)として公表した。

### EM I 抑制技術

SiC等のパワーデバイスの超高速スイッチング化に起因する電磁ノイズの増加とこれに伴う障害の深刻かが予測されている。また、これまでEMI対策技術はインバータ装置から外部機器に及ぼす障害の防止対策として研究されてきた。しかし本研究者らは、次世代半導体の超高速スイッチング化に伴い、これから発生する電磁ノイズがインバータ機器自身の誤動作に繋がることを指摘し

ている。そこで本研究では、EMIノイズを外部機器に影響を与える「外部ノイズ」とインバータ自身内部を流れる「内部ノイズ」の二種類のノイズ現象を定義し、その発生機構の解明を目指して、実験的解析を行った。

本研究では、実用を想定した筐体に収納した降圧チョッパ回路を用いて実験を行った。その結果、チョッパ回路の主デバイスのゲート駆動回路間を循環、あるいは制御回路内を通過する「内部ノイズ電流」の存在を明らかにするとともに、その等価回路モデルを導いた。

さらに、筐体の接地と非接地の状態の違いにより「内部ノイズ電流」と「外部ノイズ電流」の両方が変化する現象を見いだし、その原因として「内部ノイズ電流」の一部が「外部ノイズ電流」として装置から流出していることを明らかにした。

これらの知見は、高密度実装におけるEMI設計の重要性を示唆するとともに、高周波的絶縁の重要ポイントを指摘したことに大きな意義があると考える。本研究成果は学会発表(3)(5)(6)(12)(14)として公表した。

### ④課題4の成果

これまでの成果に基づいて、薄平面形状形のインバータを試作・評価して高電力密度化のための課題を抽出した。

### ・高電力密度単相インバータの試作

薄平面形状を取り入れた出力電力500 Wの単相PWMインバータの試作を行った (図7)。特長は、スイッチング周波数を100kHzとしてACフィルタ回路部を小型化するとともに、インダクタ巻線に多層基板を用いて大幅な薄型化を図っている。これにより、インバータの厚みを約15mmとして、放熱効果を高めている。基本動作試験により所期の性能を確認した。

一方、今回の試作の結果、放熱特性の改善が高電力密度化を行う上で重要であることも明らかとなった。さらに、プリント板配線の電流容量を高める必要があり、そのためには500ミクロン級の厚銅箔プリント板や厚み増加のための補助銅板貼り付けなどの技術開発が必要であることを示した。

図7 試作薄平面形インバータの外観

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

〔雑誌論文〕(計 2件)

- ①<u>T. Shimizu</u>, S. Iyasu, "A practical Iron Loss Calculation for AC Filter Inductors used in PWM Inverters," IEEE Trans. on Industrial Electronics, Accepted, 査読あり

- ②<u>T. Shimizu</u>, <u>K. Wada</u>, "A Gate Drive Circuit for Low Switching Losses and Snubber Energy Recovery," Journal of Power Electronics, vol.9, no.2 pp.259-266, 2009,9, 査読あり

〔学会発表〕(計22件)

- ① 前田 亮, 清水 敏久, 鳥羽 章夫, 丸山 宏 二「インダクタ用磁性体のうず電流損に関す る考察」H21 年電気学会全国大会, 4-045

- ② 山地 宏和, <u>清水 敏久</u>, 高野 耕至, 石井 仁「PWMインバータ用フィルタインダクタ鉄損 評価」H21年電気学会全国大会, 4-044

- ③ 望月 賢人, 和田 圭二, 清水 敏久, 佐藤 之 彦, 大橋 弘通「200kHz PWMインバータの相間 内部ノイズ電流の検討」H21年電気学会全国大会, 4-018

- ④ 橋野 哲, 清水 敏久「TDRを用いた高パワー密度電力変換回路パターンのインピーダンス測定」H21年電気学会全国大会, 4-048

- ⑤ 三谷 哲也, <u>和田 圭二</u>, <u>清水 敏久</u>「高周波チョッパ回路において発生する内部ノイズ電流の解析」H21電気学会研究会資料, SPC-09-42

- ⑥ T Mitani, <u>H. Ohashi</u>, <u>K. Wada</u>, <u>T. Shimizu</u>, "Discussion of Internal and External High-frequency Common Mode Noize Current on a Chopper Circuit," EPE-PEMC2008, 査読あり

- ⑦ Y. Hayashi, K. Takao, <u>T. Shimizu</u> and <u>H. Ohashi</u>, ``An Effective Design Method for High Power Density Converters, "EPE-PEMC2008、査読あり

- ⑧山地宏和,<u>清水敏久</u>「インダクタ用磁性体のヒステリシス損とうず電流損の分離に関する考察」平成20年電気学会全国大会,4-146

- ⑨山地 宏和, <u>清水 敏久</u>「磁性材料の異なる板厚による矩形波励磁でのうず電流損の評価」, 平成20年電気学会産業応用部門大会,

⑩寺島和仁,<u>和田圭二</u>,<u>清水敏久</u>,中澤知之, 石井謙市朗,林祐輔「動的マイナーループに 伴うインダクタの鉄損評価」平成20年電気学 会研究会,SPC-08-33

⑪金寛烈,<u>和田圭二</u>,<u>清水敏久</u>,高野耕至, 石井仁「PWMインバータ用フィルタインダクタ 鉄損の瞬時算出手法」平成20年電気学会研究 会,SPC-08-34

① <u>Keiji Wada</u>, Kazuhiro Shirakawa, <u>Toshihisa Shimizu</u>, ``Discussion of Internal Noise Crrents in a Control Circuit on a 200-kHz Switching PWM Inverter," IEEE/IEEJ Power Conversion Conference(PCC), pp. 423-428, 2007,査読あり

⑬Y. Hayashi, K. Takao, <u>T. Shimizu</u>, <u>H. Ohashi</u>, ``High Power Density Design Methodology," IEEE/IEEJ Power Conversion Conference(PCC), pp. 569-574, 2007,査読あり

(4) <u>Keiji Wada</u>, <u>Toshihisa Shimizu</u>, "Reduction Methods of Conducted EMI Noise on Parallel Operation for AC Module Inverters", Conference Proceedings of IEEE-PESC2007, pp3016-3021, 2007,査読 あり

⑮ Kazuhito Terashima, <u>Keiji Wada</u>, <u>Toshihisa Shimizu</u>, ``Evaluation of the Iron Loss of an Inductor Based on Dynamic Minor Characteristics," EPE 2007, 2007,査 読あり

低 Kwanryol Kim, <u>Toshihisa Shimizu</u> ``Dynamic Iron Loss Measurement Method for an AC Filter Inductor on a PWM Inverter," EPE 2007, 2007, 査読あり

① Yusuke Hayashi, Kazuto Takao, <u>Toshihisa Shimizu</u> and <u>Hiromichi Ohashi</u>, "Power Loss Desigin Platform for High Output Power Density Converters", Conference of EPE2007, 741, 2007, 査読あ

®金寛烈,<u>和田圭二</u>,<u>清水敏久</u>,高野耕至, 石井 仁「PWMインバータ回路用フィルタイン ダクタの瞬時鉄損算定法」H19年電気学会全国 大会,2-217

⑲三谷哲也, 和田圭二, 清水敏久 「高速スイ

ッチング動作に伴う電力変換器の内部ノイズ 電流の検討」H19年電気学会全国大会,4-040

⑩寺島和仁,<u>和田圭二</u>,<u>清水敏久</u>,中澤知之, 石井謙市朗,林祐輔「動的マイナーループに 伴うインダクタの鉄損評価」平成19年電気学 会産業応用部門大会,1-21

②金寛烈,<u>和田圭二</u>,<u>清水敏久</u>,高野耕至, 石井仁「PWMインバータ回路用フィルタインダ クタの鉄損低減の考察」平成19年電気学会産 業応用部門大会,1-82

⑩三谷哲也,<u>和田圭二</u>,<u>清水敏久</u>「電力変換器における内部ノイズ電流の発生要因の検討」平成19年電気学会産業応用部門大会, Y-28

### 6. 研究組織

(1)研究代表者

清水 敏久 (SHIMZU TOSHIHISA) 首都大学東京・大学院理工学研究科・教授 研究者番号:30254155

(2)研究分担者

大橋 弘道 (OHASHI HIROMICHI) 産業技術総合研究所・パワーエレクトロニ クス研究センター・副センター長 研究者番号: 60361763

和田 圭二(WADA KEIJI) 首都大学東京・大学院理工学研究科・准教 授

研究者番号:00326018

(3) 連携研究者

なし