# 科学研究費補助金研究成果報告書

平成21年 5月 13日現在

研究種目:基盤研究(C)研究期間:2007~2008 課題番号:19500038

研究課題名(和文)通信・信号処理技術支援による高速高効率情報伝送に基づく新概念の集

積回路システム

研究課題名 (英文) New-paradigm of LSI systems based on efficient data transmission using

communication and signal processing techniques.

研究代表者

弓仲 康史 (YUMINAKA YASUSHI)

群馬大学・大学院工学研究科・准教授

研究者番号:30272272

#### 研究成果の概要:

高速信号伝送時の問題点である信号の波形劣化の補正を目的とした「時間軸情報に着目した 波形強調・等化」に基づく新しい波形整形技術の考察とシミュレーション、LSI 試作による評価を行った。主な研究成果は以下の3点にまとめられる。(1) 位相情報に着目したイコライザとして、群遅延特性が平坦な特性を有するパッシブイコライザを検討した。(2) イコライザの集積回路化のための予備試作(0.18umCMOS)を行った。(3) 誘導結合を利用したチップ間無線通信とイコライザの融合技術を検討した。

## 交付額

(金額単位:円)

|        | 古拉奴弗        | 明拉奴弗     | A ∌I.       |

|--------|-------------|----------|-------------|

|        | 直接経費        | 間接経費     | 合 計         |

| 2007年度 | 2, 000, 000 | 600, 000 | 2,600,000   |

| 2008年度 | 1, 300, 000 | 390, 000 | 1, 690, 000 |

| 年度     |             |          |             |

| 年度     |             |          |             |

| 年度     |             |          |             |

| 総計     | 3, 300, 000 | 990, 000 | 4, 290, 000 |

研究分野:情報学

科研費の分科・細目:情報学・計算機システム・ネットワーク A

キーワード:集積回路、VLSIシステム、等化回路、多値情報処理、波形整形、プリエンファシス、高速インタフェース

#### 1. 研究開始当初の背景

近年、VLSI システムの極限微細化・高速化・低電圧化に伴い、GHz オーダの高速スイッチング動作が実現可能になる一方で、配線の激増、配線間クロストーク雑音等の諸問題が深刻となりつつある。これまでは、トランジスタ素子の微細化が集積回路の高性能化の原動力であったが、配線の寄生素子(抵抗、容量成分)に起因する波形劣化のため高速信

号が伝送できず、VLSIシステム全体の動作速度が配線に律速されているのが現状である。すなわち、素子の高速化に配線の情報伝送能力が追従できない配線問題が深刻化しており、「配線の高性能化に着目した集積回路の設計に関する研究」が急務となっている。

特に、高速信号伝送では、配線で信号の高 周波成分が失われることにより、伝送信号の 「振幅の低下」と「位相誤差」が問題となる。 これまで提案されている波形整形技術は失 われた振幅成分を補正・強調するものが主流であった。しかしながら、波形劣化のもう一つの要因である「位相誤差」の補正の考慮も必要である。すなわち、時間軸方向の位相誤差が多いと振幅方向の補正を施してもデータ検出タイミングがずれるため正しい情報の復元が困難になるという問題が存在する。

#### 2. 研究の目的

本研究では、「配線に着目した集積回路の 高性能化」のキーテクノロジーである波形整 形技術を再検討し、新視点の等化技術、通信 技術等の導入による通信情報処理融合型 VLSI システムの処理能力向上の検討を行う。 本課題で明らかにするのは、高速信号伝送で 問題となる信号の位相誤差の補正を目的と した「時間軸情報に着目した位相情報の波形 強調・等化」に基づく新しい波形整形技術の 考察とシミュレーション、原理実験による効 果の実証である。具体的には、波形整形イコ ライザの周波数特性の設計において、従来は 振幅の補正を目的として着目していた「振幅 特性」以外に位相誤差を決定する「群遅延特 性」に着目する。群遅延特性とは、周波数毎 の波形の遅延時間であり、これまであまり重 視されていなかった設計指標であるが、位相 のばらつき、誤差を引き起こす重要な特性と なる。

本研究では、まず、波形等化のアルゴリズムとコンパクトな回路実装を指向したに関係を種々検討し、群遅延特性に着目したたり、 群遅延特性に着目したにより、 大に、 提案回路を個別素子はよび集積回路により実現し、波形整形の別点をとれてより、 伝送路の問題域を関いた高速、 高効率な情報伝送が明して伝送がのにする。 さらに、 帯強調して伝影をあらかじめ強調して伝影をあらかじめ強調して伝影ででは、 帯強調して伝影でするプリエンファシス技術、およびチップによびチックタ (コイル)を用いて無線通信を波形を波形等化技術の融合を検討する。

#### 3. 研究の方法

高速信号伝送時の問題点である信号の位相誤差の補正を目的とした「時間軸情報に着目した位相情報の波形強調・等化」に基づく新しい波形整形技術の考察とシミュレーション、原理実験による評価を行う。次の4つのサブテーマを実施する。

(1) これまで各種提案されてきた振幅低下 を補正するイコライザを精査し、群遅延特性 が平坦な特性を有する回路構成を検討する。 その際、イコライザフィルタの種類(アクティブタイプ、パッシブタイプ、次数)の選択が補正能力、回路規模、補正可能な周波数の上限等の諸特性を決定するため、目的に応じた数種類のイコライザ構成の候補を検討する。

- (2) 伝送路をプリント基板とした場合のイコライザを実際に表面実装チップ部品等の汎用個別素子を用いて実装し、設計した回路の原理実験を行う。これにより、イコライザの位相誤差補正の性能を実証する。さらに、高速化を目的とし、イコライザの集積回路化の検討のための予備試作を行う。

- (3) 試作したイコライザ回路の測定を行う。 実測結果を元にイコライザ構成を再検討し、 新たに集積回路の試作を検討する。さらに、 次の試作においては、帯域制限の影響を考慮 し、波形をあらかじめ強調して伝送するプリ エンファシス技術、および1本の信号線に多 レベルのデータを伝送する多値通信技術等 のさらなる高効率データ伝送方式の導入も 検討する。

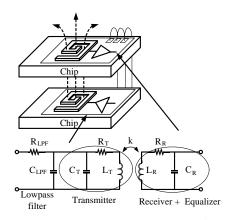

- (4)近年、チップ間をインダクタ (コイル) を用いて無線通信を可能とする技術が提案 されている。当該研究は隣接したインダクタ を用いてチップ間の通信のみを行っているが、チップ間に配置されたインダクタを波形整形のイコライザの一部として利用することを検討する。すなわち、チップ間無線通信の送受信と同時に波形整形のイコライズを行う回路の共有化を図り、チップ間高速無線通信の実現可能性を検討する。

## 4. 研究成果

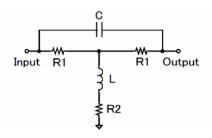

群遅延特性が平坦な特性を有する回路構成を種々検討し、補正能力、回路規模、補正可能な周波数の上限等の諸特性に優れた図1のようなパッシブタイプのイコライザが波形整形に有効であること明らかにした。

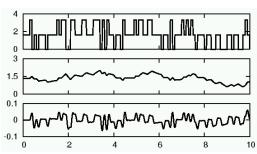

回路シミュレーションにより回路を設計した後、まず、伝送路をプリント基板とした場合のイコライザを実際に表面実装チップ部品等の汎用個別素子を用いて実装し、設計した回路の原理実験を行った。さらに、高速化を目的とし、イコライザの集積回路化のための予備試作(0.18umCMOS)を行った。図2に示した試作チップを測定した結果、所望の周波数特性が得られ、波形整形が可能であることを確認した。

また、誘導結合を利用したチップ間無線通信とイコライザの融合技術の検討を行った。 近年提案されているコイルを用いたチップ 間無線通信技術は、単にチップ間を無線通信

図1:パッシブフィルタタイプイコライザ

図2:試作したイコライザ回路

図3: コイル結合によるチップ間無線通信とイコライザ回路の一体化

図4: 多値信号(10Gbps)の伝送波形 原波形、劣化波形、コイル受信波形

## 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者には下線)

〔雑誌論文〕(計 5 件)

- ① Y. Yuminaka and Y. Takahashi、Time-Domain Pre-Emphasis Techniques for Multiple-Valued Data Transmission, Journal of Multiple-Valued Logic and Soft Computing、2009、(in press)、査読有

- ② <u>Y. Yuminaka</u> and Y. Takahashi、Time-Domain Pre-Emphasis Techniques for Equalization of Multiple-Valued Data, Proc. 38th Int. Symp. Multiple-Valued Logic、pp. 20-24、2008、查読有

- ③ Y. Yuminaka and Y. Tsubota、High-Speed Data Transmission Techniques using Raised Cosine Approximatino Signaling、17th International Workshop on Post-Binary ULSI Systems、pp. 1-4、2008、査読有

- ④ Y. Yuminaka and K. Yamamura、Equalization Techniques for Multiple-Valued Data Transmission and Their Application、Proc. 37rd Int. Symp. Multiple-Valued Logic、 CDROM、2007、査読有

- ⑤ Y. Yuminaka and K. Yamamura、Equalization Techniques for Multiple-Valued Data Transmission and Their Application、 Journal of Multiple-Valued Logic & Soft Computing、Vol. 11、pp. 569-582、2007、査読有

### 〔学会発表〕(計 6 件)

- ① 高橋靖典、逸見憲一、<u>弓仲康史</u>、パルス幅変調プリエンファシスを用いた高速多値信号伝送技術、多値論理とその応用研究会技術研究報告、2009年1月10日、桐生

- ② <u>弓仲康史</u>、信号処理と通信技術を用いた 高速インタフェース、東北大学電気情報系グ ローバルCOEプログラム、第 1 回超高速・高 精度ディジタル信号処理アルゴリズムとシ ステムに関するワークショップ、2008 年 10 月 29 日、仙台

- ③ 坪田雄介、<u>弓仲康史</u>、Raised Cosine波形を用いた高速信号伝送技術、平成19年度電子情報通信学会東京支部学生会発表会、2008年3月1日、東京

- ④ 高橋靖典、<u>弓仲康史</u>、パルス幅変調プリエンファシスを用いた多値波形等化技術[奨励賞]、平成19年度電子情報通信学会東京支部学生会発表会、2008年3月1日、東京

- ⑤ <u>弓仲康史</u>、時間軸情報に着目した波形整 形技術、東北大学電気通信研究所講演会第5 5回ニューパラダイムコンピューティング 研究会、2007 年 9 月 18 日、蔵王

- ⑥ 山村和義、<u>弓仲康史</u>、3次元積層チップ 間誘導結合無線インタフェースを用いた多 値信号伝送技術 [優秀発表賞]、第 30 回多 値論理Forum、2007 年 8 月 21 日、湘南

〔その他〕 ホームページアドレス http://cs3.el.gunma-u.ac.jp

- 6. 研究組織

- (1)研究代表者

弓仲 康史 (YUMINAKA YASUSHI) 群馬大学・大学院工学研究科・准教授 研究者番号:30272272