#### 研究成果報告書 科学研究費助成事業

今和 4 年 6 月 1 6 日現在

機関番号: 32660

研究種目: 基盤研究(C)(一般)

研究期間: 2019~2021

課題番号: 19K04930

研究課題名(和文)電子機器の静電気耐性改善に要するESD保護素子モデリング技術の確立

研究課題名(英文)Establishment of ESD Protection Device Modeling Technology for Immunity Improvement of Electronics Against ESD

#### 研究代表者

吉田 孝博 (Yoshida, Takahiro)

東京理科大学・工学部電気工学科・教授

研究者番号:10385544

交付決定額(研究期間全体):(直接経費) 2,700,000円

研究成果の概要(和文): 本研究では,これまでに我々が提案した,静電気放電から電子機器を保護するために電子回路上に多く実装されているESD保護素子の特性をより詳細に計測する方法と,その動的な特性を機器の電子回路設計で用いる高周波回路シミュレーションに反映させる方法の改良を行った.さらに,この計測方法を,保護素子の一種であるバリスタに対して新たに適用するための検討を行った.まだ途中段階ではあるが,同 等の仕様を持つ複数種のバリスタ間の僅かな特性差の計測ができたため、この手法を確立できる可能性が高いこ

研究成果の学術的意義や社会的意義本研究成果の学術的意義は、ESD保護素子にESDが印加された際の特性の解明につながる知見が得られたことと、これらの特性の計測・モデル化方法についてノウハウが蓄積できたことである。今後の研究を通じて本手法が確立されると、電子機器設計時のESD保護素子の選定をはじめとするESD対策設計が効率的に行えるようにな り,開発期間短縮・試作コスト削減,ESD対策の高度化や電子機器の信頼性向上に繋がる点において社会的意義がある。

研究成果の概要(英文): ESD protection devices are frequently used on electronic circuits to protect electronics from electrostatic discharge. In this research, we improved our previous proposed methods on detail measurement of ESD protection devices' characteristics and dynamic characteristic modeling of ESD protection devices for radio-frequency circuit simulations used in the electronic circuit design.

Furthermore, we investigated how to apply the measurement method to varistors, a kind of protection device. Although application to varistors measurement was still under development, the method could measure slight differences in the characteristics among multiple types of varistors with the same specifications. Therefore, it showed that the method could establish in the near future.

研究分野: 静電気放電、環境電磁工学、センシング信号処理

キーワード: ESD保護素子 静電気放電 回路シミュレーション

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

# 1.研究開始当初の背景

電子機器開発の 1 つの重要なプロセスである静電気放電 (ESD) 耐性の評価・改善プロセスでは,ESD 試験器により試作機に ESD を印加し,その結果をふまえて設計変更や ESD 保護素子の追加などの ESD 対策を施すサイクルを繰り返すため,試作コストの増加や設計期間の長期化が問題となっている.そのため,試作コスト削減,設計期間短縮につながるシミュレーション技術の実現が望まれており,これまで我々は,ESD が機器に加わった際に機器内部の半導体デバイスが受ける電気的ストレスをシステムレベルで算出する連成解析手法の研究を行ってきた.この提案手法の実用化に向けて,実際の電子機器に多用される ESD 保護素子の,ESD 印加時の動的応答特性のモデリング手法の確立が課題の一つとして残されていた.

#### 2.研究の目的

本研究は、電子機器の ESD 耐性改善のために機器内部に数多く用いられている ESD 保護素子に対して、開発現場で問題となっている、素子の仕様が同等であっても ESD 保護性能や特性が異なる現象への対応として、同一仕様の ESD 保護素子間の特性や保護性能の差も表現できる水準を備える ESD 保護素子の計測・評価技術、ならびに ESD ストレスシミュレーション技術の確立に向けた、ESD 保護素子の動的応答特性モデリング手法の改善を目的としている。

#### 3.研究の方法

本研究期間には,これまでに提案し研究を進めてきた ESD 保護素子の動的応答特性モデリング手法の精度改善と,本手法を他種の ESD 保護素子へ対応させるための計測手法の改良を進める実施計画に従い,(1) VNA のキャリブレーションの改善,(2) ESD 保護素子計測用プリント基板の精度改善,(3) 他種の ESD 保護素子(ESD サプレッサ,バリスタ)への提案手法の適用,(4)動的応答特性モデルにおける精度低下要因とその改善法の検討,の計 4 項目について研究を行った.

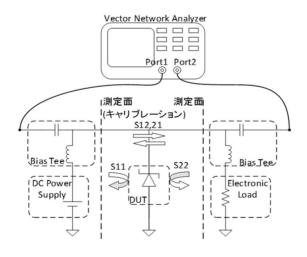

これらの検討項目のうち,項目(1)~(3)については,これまでに提案した,ESD 保護素子の動作状態(オーバーストレスが加わった際の導通状態)と非動作状態それぞれの周波数応答の S パラメータ(通過特性  $S_{21}$  ·  $S_{12}$ ,反射特性  $S_{11}$  ·  $S_{22}$ )を,図 1 に示すように,VNA とバイアスティ,直流安定化電源(DC 電源),電子負荷を用いて測定する方法をもとに,精度改善や他種の ESD 保護素子への適用を試みた.なお,動作状態の特性は,DC 電源から ESD 保護素子に印加する直流電圧と VNA の測定交流信号をバイアスティで合成した計測信号により,ESD 保護素子のプレークダウン電圧を超える状態で測定している.

図 1 ESD 保護素子の動作状態・非動作状態の応答特性の測定系

また,検討項目(4)については,これまでに提案した,Sパラメータとして測定した ESD 保護素子の応答特性を ESD ストレスシミュレーションに反映させるための高周波回路シミュレーションにおける回路構成に対して,精度低下要因の検討とその改善法の検討を行った.

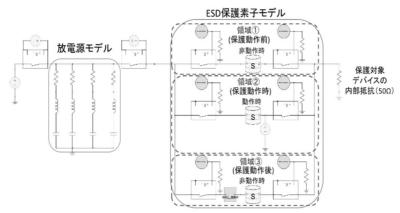

本手法では,図2に示す回路構成により ESD ストレス印加時の ESD 保護素子の時間的な応答を以下の3つの動作状態の時間的遷移とみなし,各領域のリレーを順次切り替えることで反映させている.

- ・領域 …ESD ストレスが印加されてから ESD 保護素子が動作するまでの保護動作前の非動作状態を, 非動作時の S パラメータで反映.

- ・領域 ...ESD 保護素子が動作状態となり, ESD ストレスがグラウンドにバイパスされ, クランプされている保護動作状態を,動作時のSパラメータと,クランプ電圧再現用の直流電圧源にて反映.

・領域 …ESD ストレスの印加電圧がクランプ電圧以下になった後(保護動作終了後)の非動作状態を,前段階(領域 )を通過した ESD ストレスを生成する,領域 と同等の特性を持つ回路網と非動作時のSパラメータを直列に接続して反映.

なお,領域 から領域 への切替は,領域 の電圧波形が ESD 保護素子のブレークダウン電圧を超えたタイミングとし,領域 から領域 への切替は,放電源モデルの電圧波形が ESD 保護素子のブレーク電圧以下になるタイミングとしている.

図 2 ESD 保護素子の動的特性を反映させた ESD ストレスシミュレーションの回路構成

#### 4. 研究成果

本研究期間には,前述の4項目について以下の研究成果を得た.

# 4.1.ポートエクステンションによる VNA のキャリブレーションの改善

2018 年度までの先行研究では,測定対象の ESD 保護素子 (DUT)を実装した計測用プリント基板に接続される同軸ケーブルの先端 (SMA コネクタ)にて, VNA のオープン・ショート・ロードのキャリブレーションを行っていた.今回は,計測精度の更なる改善のため, VNA のキャリブレーションにて計測用プリント基板を用いたポートエクステンションを行うことで,計測用基板の影響を低減し,より高精度に測定できるようにした.

# 4 . 2 . コプレーナ線路による ESD 保護素子計測用プリント基板の精度改善

ESD 保護素子計測用プリント基板の製作において,先行研究では基板表面のマイクロストリップラインのパターン直近に基板を貫通する穴をあけて基板裏面のベタグラウンドパターンとの間に素子を実装していたが,今回は,コプレーナ線路で基板を設計・製作することで,素子を基板表面に実装することが可能となり,基板の製作精度,インピーダンス整合精度が改善した.

図3 コプレーナ線路による ESD 保護素子計測用表面実装基板

# 4 . 3 . 他種の ESD 保護素子 (ESD サプレッサ, バリスタ) への提案手法の適用

先行研究では,ESD 保護素子のモデリング手法を,ブレークダウン電圧が低いTVS ダイオードに対して適用して有効性を示したが,今回は新たに ESD サプレッサとバリスタに対して適用を試みた.

### 4 . 3 . 1 . ESD サプレッサへの適用

モデリング対象の ESD サプレッサとして,ブレークアウト電圧が 500V-TLP 試験では 500V, IEC61000-4-2 ガン試験では 250V の仕様である素子を用いて,今回導入した高耐電圧のバイアスティ(周波数帯域 750kHz~10GHz,耐電圧 1.5kV,電流 20mA)を用いて,保護素子の保護動作状態であるブレークダウン状態(導通状態)の大電流による熱的破壊やバイアスティの過電流による破壊を防止するために,直流電源に 1M の無誘導抵抗を直列接続し,直流電圧 800V を印加したが,ESD サプレッサが動作状態にならず計測ができなかった.この失敗について,周波数帯域と耐電圧を最優先してバイアスティを選定してしまい,バイアスティの耐電流が不足した結果,抵抗による分圧で素子に加わる電圧が不足したことが要因であると考えた.

そこで,バイアスティと VNA を用いず,直流電圧源から DC100V~800V を ESD サプレッサに直接印加して,素子の両端を高電圧プローブとオシロスコープで計測することで原因の検討を行った.その結果,ESD サプレッサのブレークアウト電圧である 500V 以上で動作状態に至ったが,

ESD サプレッサの動作による過電流で高電圧電源の保護回路が瞬時に機能し, VNA による S パラメータ測定ができなかった.

そのため,2022 年度からの継続課題の遂行に向けて,電流供給能力のある高電圧電源の導入,耐電圧・耐電流・周波数帯域を満たすバイアスティの導入,ESD 保護素子の熱的破壊を防止するために測定周波数毎に短時間パルスでDC バイアスを印加する間欠VNA 測定のための装置の開発の構想を得た.

#### 4.3.2.バリスタへの適用

ESD サプレッサは,ある一定印加電圧(ブレークダウン電圧)以上になると内部の回路が導通状態となり急激に大電流が流れ,電流・電圧(IV)特性がスナップバック特性を持つ.一方,バリスタは ESD サプレッサとは性質が大きく異なり,一定印加電圧(バリスタ電圧)以上において,素子に加わる電圧の上昇と共に抵抗値が低下し導通状態に向かう特性がある.

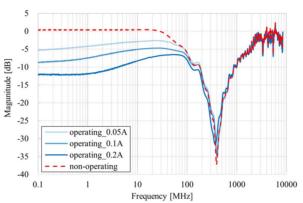

このような特性を持つバリスタに対して,提案手法による測定を試行したところ,バリスタの内部抵抗が十分に低下する電圧を印加するためには大電流を流す必要があるが,使用したバイアスティや電源の仕様の問題で,電流が0.2Aに制限されたことから,印加できる電圧が不足する問題が生じた.

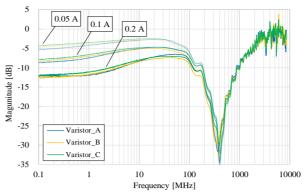

そこで,バリスタの低電圧・小電流時の特性依存性を確認するため,電流制限が50mA,100mA,200mAの3段階で計測を行い,特性を比較したところ,図4に示すように,特に100MHz以下の通過量が電流値に依存し,電流を大きく流すほどに導通状態に徐々に近づいてゆき,通過量が減少する傾向が見られた.そのため,バリスタの定格時の保護特性を測定するには,より多くの十分な電流を流すことが必要であることが分かった.

図 4 バリスタの動作状態に対する VNA 測定における電流制限による通過特性 S2 の変化

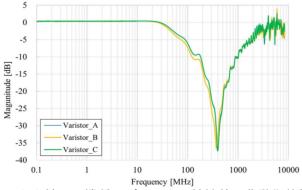

しかし,現状で保有する機器で研究目的の達成を目指し,類似したスペックを持つ3機種のバリスタの特性差の計測を,電流制限50mA,100mA,200mAの3段階においてVNAで周波数特性の計測を試みた.3機種のバリスタの仕様は,バリスタ電圧は3機種で同一の18V,クランプ電圧はほぼ同等の33~35V,ピーク電流は同一の30V,静電容量も同一の210VFである.

その結果,図5と図6に示すように,各電流値における特性差・傾向が測定時の電流に依存せず,どの電流値においても,バリスタの機種間で同様に差違が見られたため,本研究の提案手法がバリスタの評価にも適用できる可能性が高いことが確認できた.

図 5 類似したスペックを持つ3機種のバリスタの特性差(非動作状態・通過特性 S₂₁)

図 6 類似したスペックを持つ3機種のバリスタの特性差(動作状態・通過特性 Sal)

今後は,バリスタのより正確な計測・評価に向けて,ESD サプレッサにおける今後の方針と同様に,2022 年度からの継続課題において,電流供給能力のある電源の導入,耐電流・耐電圧・周波数帯域を満たすバイアスティの導入,DUTの熱的破壊を防止するための短時間のパルス印加による VNA 測定のための装置・回路・ソフトウェアの開発を進めてゆく.

# 4.4.ESD ストレスシミュレーションのための動的応答特性モデルにおける精度低下要因とその改善法の検討

ESD 保護素子の動作状態・非動作状態間の遷移で ESD 保護素子の動的特性をモデリングした図2 の提案回路構成を用いて高周波回路シミュレータ上で ESD ストレスシミュレーションを行う際,より高機能で高性能な高周波回路シミュレータソフトウェアへ変更し,その上で提案手法の回路構成やシミュレーション条件設定を試行錯誤し,移行を完了させた.そして,精度改善のために回路構成の見直しを行うために,回路素子値やモデリングされた s パラメータの特性を意図的に変更しながら ESD シミュレーションと実測との間の誤差の発生傾向を把握するアプローチで検討を進めた.

その結果,精度低下の一因が,3つの回路要素の切り替え時刻における各回路の波形の不連続性にあるとの仮説に至った.そのため,この問題の解決のために,回路要素間の切り替えにおいて不連続性を低減するための各回路要素の切り替えに使うリレーにおいて抵抗値を連続して変化させる手法を考案した.この手法の実現のため,Voltage Control Resistor ブロックを用いる方法や,ビヘイビア電源ブロックの製作による方法や,抵抗値のパラメータに電圧を変数として電圧源により抵抗値を可変させる方法などで試行したが,現有の高周波回路シミュレータでは所望の動作が実現できず,研究期間が終了した.

そのため,2022 年度からの継続課題で他機種の高周波回路シミュレータを導入し,改良アイディアを試行錯誤し,精度改善を目指す.

| 5 | 主 | な | 発 | 表 | 論 | 文 | 筡 |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

〔雑誌論文〕 計0件

| 〔学会発表〕 | 計1件 | (うち招待講演 | 0件/うち国際学会 | 1件) |

|--------|-----|---------|-----------|-----|

|        |     |         |           |     |

| 1 | 発表者名 |

|---|------|

|   |      |

Haruhiro Takemura, Takahiro Yoshida

# 2 . 発表標題

A Study on ESD Protection Characteristic Difference Measurement of Varistors by VNA

### 3.学会等名

2022 Asia-Pacific International Symposium on Electromagnetic Compatibility (APEMC2022)(国際学会)

#### 4.発表年

2022年

#### 〔図書〕 計0件

### 〔産業財産権〕

〔その他〕

\_

6. 研究組織

| _ |  |                           |                       |    |  |  |  |

|---|--|---------------------------|-----------------------|----|--|--|--|

|   |  | 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |  |  |  |

# 7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

8. 本研究に関連して実施した国際共同研究の実施状況

|  | 共同研究相手国 | 相手方研究機関 |  |

|--|---------|---------|--|

|--|---------|---------|--|