#### 研究成果報告書 科学研究費助成事業

今和 3 年 5 月 2 4 日現在

機関番号: 13901

研究種目: 研究活動スタート支援

研究期間: 2019~2020 課題番号: 19K24341

研究課題名(和文)近似コンピューティング効率を極限まで高める潜在性能活用型VLSIの研究

研究課題名(英文)Study on design optimization of VLSI circuits for efficient approximate computing

#### 研究代表者

增田 豊 (Masuda, Yutaka)

名古屋大学・情報学研究科・助教

研究者番号:60845527

交付決定額(研究期間全体):(直接経費) 2,200,000円

研究成果の概要(和文):本研究では、VLSI 自身が電源電圧を自律的に制御する設計技術である適応的電圧制御 (AVS) を 近似コンピューティング (AC) に応用することを見据えて、AVS の効果を高める被制御回路の設計手法を推進した。クリティカルパス・アイソレーション (CPI) とビット幅削減 (BWS) の協調設計手法を提案した。評価実験により、BWS とCPI は非常に親和性が高く、両者の協調が相乗的に省電力効果を高めることを確認 した。GPGPU プロセッサを用いた評価実験により、複数の PVTA コーナーにおいて、消費電力を大きく削減できることを実験的に確認した。

研究成果の学術的意義や社会的意義本研究は、「回路自身が計算品質を自律制御する」設計技術を見据えており、これは「最も悪い性能の回路に合わせる」従来設計技術とは本質的に異なるものである。本研究で構想する設計技術が完成した暁には、既存研究が抱える「性能ばらつきにより電力効率及び処理性能が大幅に低下する」問題を根本的に解決する。本研究では、計算品質を低電力動作下においても担保し、柔軟な自律制御を実現するための、集積回路の設計手法を提案した。評価実験により、提案設計が異なる動作環境(電源電圧、温度など)において省電力効果を発揮できることを実験的に確認し、自律性能制御 VLSI (超大規模集積回路) への応用に期待できる成果を得た。

研究成果の概要(英文): This work proposed a design methodology that saves the power dissipation under voltage over-scaling (VOS), which is one of the approximate computing techniques aiming at low-power design. The key idea of the proposed design methodology is to combine critical path isolation (CPI) and bit-width scaling (BWS) under the constraint of computational quality. Thanks to the co-design optimization, the proposed design dramatically reduces the supply voltage and power dissipation while satisfying the quality constraint. Evaluation result show that CPI and BWS are highly compatible, and they significantly enhance the efficacy of VOS. In a case study of GPGPU processor, the proposed design saves the proposed design saves

by 51.2% at most. This work also confirmed that the proposed design made the significant power savings even when operating at different PVTA corners.

Thus, such a variation-tolerant design can be useful for self-tuning design such as adaptive voltage scaling (AVS).

研究分野:集積回路の省電力設計

キーワード: 低消費電力設計 近似コンピューティング クリティカルパス・アイソレーション ビット幅削減

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

### 1.研究開始当初の背景

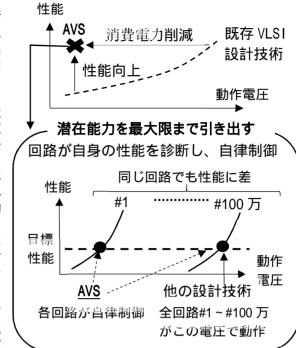

- (1) 省電力化と高性能化を両立する設計技術として、重要な計算を正確に実行し、他を近似する AC (近似コンピューティング) に期待が無まっている。一方、 半導体製造プロセスの微細化に伴い、回路性能のばらつきが顕在化しており、従来の VLSI (超大規模集積回路) 設計では、性能の悪い回路を正常に動作させるために、設計者が全ての回路に対している。しかし、この対策は性能の良い回路も高い電圧で動作させ、消費電力を増大させらことを克服する方策として、AVS (適応的電圧制御) が有望視されている (図1)。これは、VLSI が自身の性能を自律的に見積もり、動作電圧を調整する設計技術である。

- (2) AVS では、被制御回路に埋め込まれたセンサに基づき、電源電圧が制御される。報告者はこれまでの研究で、センサと被制御回路の一体最適設計手法とその性能評価手法を提案し、この設計手法による38.0% の省電力効果を確認した。ここで、AC では、計算品質の要求を満たす範囲で計算誤差を許容することにより、省電力化と高性能化を達成している。一方、従来型AVS は、計算誤差を許容せず、故障しない高い電源電圧を常に供給するため、AC が潜在的に持つ

図 1: AVS のコンセプト.

省電力効果と性能向上効果を十分に引き出すことはできない。このような背景から、「AC の潜在能力を最大限まで引き出す新コンピューティング技術をどのように創出していくか」という問題が、本研究課題の核心をなす学術的「問い」として存在する。

#### 2.研究の目的

VLSI 自身が電源電圧を自律的に制御する設計技術である適応的電圧制御 (AVS) を近似コンピューティング (AC) に応用することを見据えて、AVS の効果を高める AC 回路の設計手法を構築し、設計後回路の省電力効果を定量的に評価することを目指す。

### 3.研究の方法

- (1) AVS の効果を高めるためには、多様な PVTA (Process, Voltage, Temperature, and Aging) コーナーにおいて省電力効果を推進可能な、被制御回路の設計技術が有効である。本研究では、被制御回路のタイミング最適化技術として、クリティカルパス・アイソレーション (Critical Path Isolation; CPI) とビット幅削減 (Bit-Width Scaling; BWS) に着目し、両者の混合設計法を研究する。CPI は、活性化するクリティカルパス (CP) の遅延を削減することで、低電圧動作時にタイミング故障を起こす CP の数を削減する。BWS は、数値の表現に用いるビット幅を削減することで、データパスの実現に要する回路資源を低減する技術である。両者の併用により、回路中の CP を大幅に削減し、低電圧化と省電力化を大幅に推進できると期待される。

- (2)設計後回路の消費電力を評価する。SPICE シミュレーションベースのキャラクタライズを用いて、多様な PVTA コーナーにおける遅延ライブラリファイルを生成する。 さらに、これらの遅延情報に基づき、「(1) の設計の適用前後における性能と消費電力」をそれぞれ論理シミュレーションを利用して定量的に評価する。多様な PVTA コーナーでの評価結果を考察し、提案設計の性能ばらつきへの堅牢性を実験的に評価し、AVS との親和性を議論する。

## 4.研究成果

(1) CPI の適用にあたって、「CPI が本質的な CP の遅延を削減できない」という根本的な課題を発見した。本質的な CP は、しきい値電圧の低いセルやゲート幅の広いセルにより構成され、論理セルの置換や論理段数の変更による遅延削減が困難なパスである。従って、本質的な CP が活性化し、AC の計算品質に影響しうる場合は、CPI の電源電圧削減効果が大幅に低下する可能性がある。上記の CPI の課題を解決するために、本質的な CP を削減可能な対策技術として、CPI と BWS の混合設計コンセプトを考案した。提案設計では、BWS と CPI を組み合わせることで、本質的な CP と本質的でない CP の両方を削減する。CP を大幅に削減することで、例えば電源電圧を低減した際の計算品質の劣化特性を劇的に改善し、低電圧化と省電力化を大きく促進できる

## と期待される。

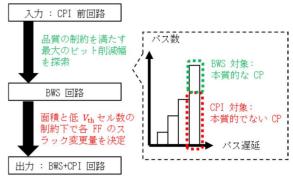

(2) (1)のコンセプトをベースとして、CPIとBWS の混合設計法を提案した (図 2)。BWS は ACの設計技術の一種であり、計算精度の低下に起因して、計算品質を劣化させ得る。従って、計算品質の制約を満足しつつ消費電力を最小化するためには、設計者はビット幅、CPI方法、電源電圧などの設計パラメータ組を注意深く設定する必要がある。一方、計算品質、回路構造および電源電圧などのパラメータ間の関係を表す関数は複雑である。また、VOS (Voltage Over Scaling) を前提とした最小動作電圧を評価するためには、回路のタイミング情報と想定するワークロードを用いて、計算時間の長い

図 2: CPI と BWS の提案混合設計法.

論理シミュレーションを実行する必要がある。これらの観点から、最適な設計パラメータ組を網羅的に探索することは、計算時間の観点で容易ではない。以上の考えに基づき、本研究では、BWSと CPI の設計探索空間を大幅に削減可能な手法を提案した。BWSと CPI の適用対象がタイミングクリティカルな FF もしくはパスであることに着目し、両適用対象の最小動作電圧が回路全体の最小動作電圧の良い下界となると仮定する。ここで、BWS は本質的な CP、CPI は本質的でない CPを対象としており、両者の遅延削減対象箇所は異なる。また、ビット幅は BWS の本質的な CPの遅延に影響し、CPI 方法は本質的でない CPの遅延に影響するとみなせる。これらの点に着目し、提案設計では、BWS のビット幅と CPI 方法を独立に設計する。両者を独立に設計することで、設計探索空間を大幅に縮小しつつ、電源電圧を最小化し、消費電力を大幅に削減する。

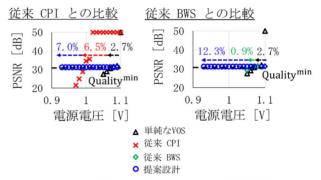

(3) 提案設計手法の省電力効果をVOS 論理シミュレーションに基づき、定量的に評価した。オープンソースのGPGPUプロセッサである、Nyuziプロセッサを対象回路として選択した。この回路を、商用ツールと45nmプロセスのNangate スタンダードセルライブラリを用いて論理合成した。ワークロードとして、Mandelbrot 集合の描画プログラムとニューラルネットワークの推論プログラム(Fourclass)の2種類を選択した。計算品質の制約として、Mandelbrot では 30dB の PSNR、

図3: 提案設計の電源電圧削減効果.

Fourclass では98%の推論精度をそれぞれ設定した。図3にMandelbrot ワークロードにおける、 電源電圧と計算品質のトレードオフ評価結果を示す。黒色のプロットは、タイミング最適化を行 わずに電源電圧を低減する、単純な VOS の結果を表す。また、赤色、緑色、青色はそれぞれ、従 来の CPI、従来の BWS、および提案設計の評価結果を示す。図3より、提案設計がより低い電源 電圧においても目標の計算品質を達成しており、低電圧効果を推進していることが読み取れる。 同様に、提案設計の省電力効果をシミュレーションにより評価したところ、Mandelbrot では 450.0mW から 257.8mW まで 42.7%、Fourclass では 567.5mW から 277.4mW まで 51.2%、消費電力 を削減できることを実験的に確認した。これらの評価結果から、BWS と CPI の親和性は非常に高 く、両者の協調設計最適化が VOS 時の省電力効果を相乗的に高めることを実験的に確認した。次 に、異なる PVTA コーナーにおける、提案設計の省電力効果を評価した。本実験では、遅延と電 力のライブラリファイル(liberty ファイル) の情報をワーストコーナーから typical コーナー に置換し、最小動作電圧をスイープした。なお、ゲートレベル・ネットリストとクロック周期は 変更せずに、コーナー情報のみ更新した。コーナー情報を変更することで、回路内の論理ゲート の遅延値や感度が大幅に変動する。従って、異なる PVTA コーナーにおいても、提案設計が同様 の省電力効果を発揮できるか評価することで、提案設計の PVTA ばらつきへの脆弱性を実験的に 評価できる。評価実験により、Typical コーナーにおいても、提案設計が消費電力を大きく削減 できることを確認した。例えば、Mandelbrot プログラムでは 218.1mW から 133.0mW まで 39.1%、 Fourclass では 273.7mW から 146.2mW まで 46.6% の省電力効果を達成した。以上より、提案設 計が遅延感度の大きく異なる PVTA コーナー群において、省電力効果を発揮できることを実験的 に確認した。今後の課題は、提案設計を AVS に応用し、多様な PVTA コーナーで自律的に VOS 動 作を実現する設計技術を実現することである。

#### 5 . 主な発表論文等

〔雑誌論文〕 計0件

| ( 学会発表 ) | 計⊿件(    | (うち招待護演     | 0件 / うち国際学会 | 2件 \  |

|----------|---------|-------------|-------------|-------|

| し十五九化」   | # TIP 1 | し ノンコロ 可明/宍 | 0斤/ ノン国际十五  | 2IT / |

| 4 | 3V. + +/ A |  |

|---|------------|--|

| 1 | 松夫老夕       |  |

|   |            |  |

Yutaka Masuda, Jun Nagayama, TaiYu Cheng, Tohru Ishihara, Yoichi Momiyama, and Masanori Hashimoto

## 2 . 発表標題

Critical Path Isolation and Bit-Width Scaling Are Highly Compatible for Voltage Over-Scalable Design

### 3 . 学会等名

IEEE Design, Automation and Test in Europe Conference (DATE) (国際学会)

4.発表年

2021年

#### 1.発表者名

Yutaka Masuda, Jun Nagayama, TaiYu Cheng, Tohru Ishihara, Yoichi Momiyama, and Masanori Hashimoto

## 2 . 発表標題

Variation-Tolerant Voltage Over-Scalable Design with Critical Path Isolation and Bit-Width Scaling

#### 3.学会等名

International Workshop on Logic & Synthesis (IWLS) (国際学会)

4.発表年

2020年

# 1.発表者名

增田豊,長山準,鄭泰禹,石原亨, 籾山陽一,橋本昌宜

### 2 . 発表標題

クリティカルパス・アイソレーションとビット幅削減を用いた過電圧スケーリング向け省電力設計手法

## 3 . 学会等名

情報処理学会DA シンポジウム

4.発表年

2020年

#### 1.発表者名

増田豊

## 2 . 発表標題

ポストムーア時代に向けた回路設計検証技術

#### 3.学会等名

第7回NCESシンポジウム

4.発表年

2020年

〔図書〕 計0件

〔産業財産権〕

〔その他〕

-

6.研究組織

| · K// 5 0/104/194         |                       |    |

|---------------------------|-----------------------|----|

| 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |

7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|