# 科学研究費補助金研究成果報告書

平成23年6月12日現在

機関番号: 13801

研究種目:新学術領域研究(研究課題提案型)

研究期間: 2008 ~ 2010 課題番号: 20200027 研究課題名(和文)

MEMS・レーザアレイによる高速動的光再構成型ゲートアレイの研究開発

研究課題名 (英文)

High-speed optically reconfigurable gate array exploiting a MEMS and a laser array 研究代表者

渡邊 実 (Watanabe Minoru) 静岡大学・工学部・准教授 研究者番号:30325576

#### 研究成果の概要(和文):

近年、日本の半導体産業は熾烈な国際競争の中で、日本固有の技術的優位を保てずに苦戦している。また、VLSI プロセスの微細化が難しくなり、ムーアの法則に従って急激に進歩してきた VLSI 技術の先行きが不透明になってきている。それらの理由から申請者らは既存の微細化に頼る半導体の進歩の流れとは一線を画する光電子融合半導体の研究を進めてきた。本研究では MEMS・レーザアレイ・ハイブリッド構造による高速動的光再構成型ゲートアレイを開発した。10 億ものコンテキストを数ナノ秒周期でゲートアレイに実装し続けることが可能で、これまでに無い超高速動的再構成技術を実現した。

#### 研究成果の概要(英文):

Optically reconfigurable gate arrays (ORGAs) were developed to realize next-generation large-virtual gate count programmable VLSIs. An ORGA consists of an ORGA-VLSI, a holographic memory, and a laser array. Although many configuration contexts can be stored on a volume-type holographic memory, the corresponding number of lasers must be implemented on an ORGA. However, a laser array with numerous lasers is always expensive. Therefore, to accommodate numerous configuration contexts with fewer lasers, this research has demonstrated a microelectromechanical system (MEMS) interleaving method for a holographic memory of optically reconfigurable gate arrays. This method can provide an addressing capability of a billion configuration contexts along with a nanosecond-order high-speed configuration capability.

#### 交付決定額

(金額単位:円)

|         | 直接経費         | 間接経費        | 合 計          |

|---------|--------------|-------------|--------------|

| 2008 年度 | 9, 000, 000  | 2, 700, 000 | 11, 700, 000 |

| 2009 年度 | 8, 500, 000  | 2, 550, 000 | 11, 050, 000 |

| 2010 年度 | 8, 500, 000  | 2, 550, 000 | 11, 050, 000 |

| 総計      | 26, 000, 000 | 7, 800, 000 | 33, 800, 000 |

研究分野:光情報処理、集積回路工学、宇宙デバイス

科研費の分科・細目:電気電子工学・電子デバイス・電子機器

キーワード: (1) 光再構成ゲートアレイ (2) プログラマブルデバイス (3) MEMS

(4) DLP (5) ホログラムメモリ (6) FPGA

#### 1. 研究開始当初の背景

近年、日本の半導体産業は熾烈な国際競争の中で、日本固有の技術的優位を保てずに苦戦している。また、VLSIプロセスの微細化が難しくなり、ムーアの法則に従って急激に進歩してきた VLSI 技術の先行きが不透明になってきている。それらの理由から申請者らは既存の微細化に頼る半導体の進歩の流気をは一線を画する光電子融合半導体の研究を進めてきた。VLSIゲート規模を超える情報を3次元ホログラムメモリ内に蓄え、それをVLSI部に動的に実装する事で、仮想的に超上大な VLSI を実現することと、VLSI上のゲートアレイの一部分の休止も無い、全エリア常時活性状態での運用を可能にする超高効率 VLSIを実現することがその開発目的である。

従来の光再構成型ゲートアレイはホログラムメモリのアドレッシングにレーザアレイを使用してきた。VCSEL(Vertical Cavity Surface Emitting LASER)を使用すれば、多数のレーザをアレイ状に実装できるので、その目的を達成することができるが、将来的に必要とされるコンテキスト数(回路情報数)は100万以上であり、仮に1000x1000のVCSELが実現できたとしても、そのコスト面で採算が取れるのかどうかが問題視されてきた。

#### 2. 研究の目的

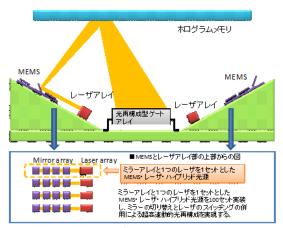

図1に示す MEMS・レーザアレイ・ハイブリ ッド構造による高速動的光再構成型ゲート アレイの開発を目指す。本デバイスはホログ ラムメモリ、MEMS(ミラー・アレイ・デバイ ス)、レーザアレイ、光書き込み型プログラ マブルゲートアレイ VLSI から構成される。 予めホログラムメモリ内に大量の回路情報 を記録しておき、MEMS とレーザアレイの併用 によりホログラムメモリから高速かつ連続 的に回路情報を読み出し、それら情報を VLSI 部に動的に書き込む。ホログラムメモリは非 常に大容量の記憶が可能であることから1兆 ゲートを超える超巨大な回路情報を記憶さ せることが可能である。また、スイッチング は低速であるが、大容量アドレッシングが得 意なミラーアレイデバイス(MEMS)と、高速な スイッチングを得意とするが高価となるレ ーザアレイをハイブリッドに実装すること で 100MHz 以上の周波数で 10 億を超えるコン テキストの定常的な再構成が実現できる。

#### 3. 研究の方法

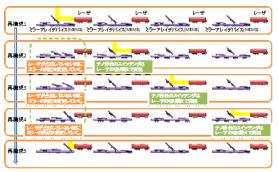

MEMS・レーザアレイを併用したホログラムメモリのアドレッシングのメカニズムを図2に示す。図では1つのレーザと3つのミラーを持つミラーアレイデバイスが4セット実装されている様子を示している。一番上から1回目の再構成、2回目の再構成と、5回分

図 1: MEMS・レーザアレイ・ハイブリッド構造による高速動的光再構成型ゲートアレイの構想図

図 2:ミラーアレイデバイス、レーザアレイ のハイブリッド構成を用いた光再構成

の連続した再構成の様子を示している。もし、 ミラーアレイデバイスのミラーの角度調整 が完了しているとすると、4つのレーザを順 に点灯させていけば、レーザのスイッチング 時間であるナノ秒台での高速再構成が実現 できる。もちろん、レーザ数を超える再構成 が続く場合には、ミラーデバイスのミラーを 再度動かす必要があり、Wait が発生するが、 十分な数のレーザがあればその Wait 発生は 無視できる。また、レーザ数が増せば増すほ ど、レーザが消灯している間に動かすミラー の応答速度は遅くても許容できる。例えば 1000 個のレーザを実装して 10ns での連続再 構成を行う場合、許容できるミラーの応答速 度は約10μsとなる。この速度はMEMSの1 種であるテキサス・インスツルメンツ社のマ イクロミラーデバイス(DMD: Digital Micro mirror Device)で実現できる速度である。ま た、この 1000 個のレーザモジュールに実装 されるミラーの数を増やせば、アドレッシン グの数はいかようにでも増やすことができ る。例えば、1000個のミラーを実装したレー

ザモジュールを 1000 個実装すれば、100 万個のコンテキストの 10ns 周期でのアドレッシングが可能になる。この実証のために、光再構成型ゲートアレイ VLSI 部、ホログラムメモリ部、レーザ・MEMS ハイブリッド光源部に分けてそれぞれを分担試作し、最終的にMEMS・レーザアレイによる高速動的光再構成型ゲートアレイとして組み合わせ、試験的にその性能を明らかにした。

## 4. 研究成果

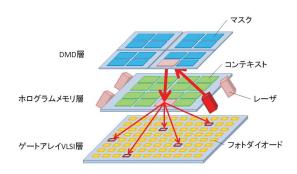

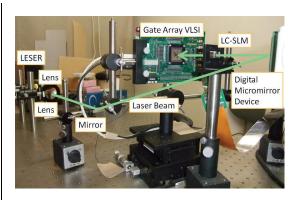

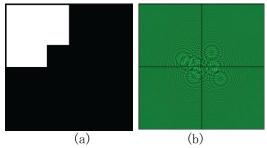

MEMS・レーザアレイによる高速動的光再構 成型ゲートアレイの開発結果を示す。図3に そのブロック図を、図 4 に光学写真を示す。 この光学系は、波長 532nm、光出力 300mW の レーザ光源、MEMS の1種であるテキサス・イ ンスツルメンツ社の DMD、液晶ホログラムメ モリ(LC-SLM: Liquid Crystal Spatial Light Modulator), ゲートアレイ VLSI から構成さ れる。この DMD には 1024×768 個のミラーが 実装されており、1 つのミラーの大きさは  $10.8\mu\,\mathrm{m} \times 10.8\mu\,\mathrm{m}$ 、各ミラーは $\pm 12^{\circ}$  の範囲 で動かせる。ここでは試験を容易にする目的 で、図 5(a) に示す様に、236×236 個のマイ クロミラーを1つのミラーとして使用し、そ のミラーを4つ実装して試験を行った。4ミ ラー・1 レーザモジュールの実装に相当する。 この4つのミラーの内の1つによって反射さ れたレーザ光は液晶ホログラム上の対応す るホログラム領域に入射する。ここで、液晶 ホログラムにはセイコーエプソン製の 1,920  $\times 1,080$  ピクセル、画素ピッチ  $8.5 \mu$  m $\times 8.5$  $\mu$ mのTFT液晶パネル(L3D07U-81G00)を用い、 その上に図 5(b) に示すような計算機ホログ ラムパターンを実装した。ここでは4つのコ ンテキストのホログラムパターンが実装さ れている。最終的にミラーのスイッチング、 レーザのスイッチングによる光再構成に成 功し、4 ミラー・1 レーザモジュールの実装 に成功した。

本研究においては、この MEMS とレーザア レイとを併用した高速光再構成技術を実証

図3:MEMS・レーザアレイによる高速動的光 再構成型ゲートアレイのブロック図

図4:MEMS・レーザアレイによる高速動的光 再構成型ゲートアレイの光学写真

図5:ミラーアレイとホログラムパターン

する以外にも、偏向依存性ホログラムメモリ技術の研究、MEMS デバイスをホログラムメモリとして使用した MEMS 光再構成型ゲートアレイの研究、MEMS を利用した宇宙空間向けプログラマブルデバイスの研究、MEMS 光電子デバイスの組み立て技術などの研究を実施した。それらの成果については以下の参考文献に示す。

## 5. 主な発表論文等

〔雑誌論文〕(計3件)

- [1] H. Morita, M. Watanabe, "Micro electro mechanical Configuration of an Optically Reconfigurable Gate Array," IEEE Journal of Quantum Electronics, Vol. 46, Issue 9, pp. 1288 1294, 2010.

- [2] A. Ogiwara, M. Watanabe, T. Mabuchi, F. Kobayashi, "Formation of holographic memory for defect tolerance in optically reconfigurable gate arrays," Applied Optics, Vol. 49, No. 22, pp. 4255-4261, 2010.

- [3] M. Nakajima, M. Watanabe, "A four context optically differential reconfigurable gate array," IEEE/OSA Journal of Lightwave Technology, Vol. 27, No 20, pp. 4460-4470, 2009.

- 〔査読付き国際会議論文〕(計29件)

- [1] T. Watanabe and M. Watanabe, "Dependable optically reconfigurable gate array with a phase-modulation type holographic memory," International conference on Field-Programmable Logic and its Applications, 2011.

- [2] T. Mabuchi, M. Watanabe, A. Ogiwara, F. Kobayashi, "Optically reconfigurable gate array with a polymer-dispersed liquid crystal holographic memory," NASA/ESA Conference on Adaptive Hardware and Systems, 2011.

- [3] T. Watanabe, M. Watanabe, "A 16-laser array for an optically reconfigurable gate array," IEEE International Conference on Space Optical Systems and Applications, pp. 255-260, 2011.

- [4] Y. Aoyama, M. Watanabe, "Reduction method of refresh cycles for a dynamic optically reconfigurable gate array, IEEE Symposium on Low-Power and High-Speed Chips, 2011.

- [5] F. Matsusaki, F. Kobayashi, A. Nagino, M. Watanabe, "Programming Options for an Optical FPGA with Clockwise Dynamic Reconfigurability," International Conference on Innovative Computing and Communication and Asia-Pacific Conference on Information Technology and Ocean Engineering, 2011.

- [6] H. Morita, M. Watanabe, "MEMS interleaving read operation of a holographic memory for optically reconfigurable gate arrays," International Workshop on Applied Reconfigurable Computing, Lecture Notes in Computer Science, Vol. 6578, pp. 242-252, 2011.

- [7] Y. Yamaji, M. Watanabe, "A 64-context MEMS optically reconfigurable gate array," IEEE International Conference on Field-Programmable Technology, pp. 499-502, 2010.

- [8] H. Morita, M. Watanabe, "A retention time improvement method for a MEMS dynamic optically reconfigurable gate array," International Symposium on Micro-NanoMechatronics and Human Science, pp.257-261, Nagoya, Japan, Nov., 2010.

- [9] A. Ogiwara, M. Watanabe, T. Mabuchi, E. Kobayashi, "Formation of holographic memory using subwavelength grating mask for optically reconfigurable gate array," MICROOPTICS CONFERENCE, pp. 108-109, 2010.

- [10] T. Watanabe, M. Watanabe, "Fault

- tolerance of a holographic storage system,"

International Symposium on

Communications and Information

Technologies, pp. 1126-1130, 2010.

- [11] D. Seto, M. Watanabe, "Recovery method for a laser array failure on Dynamic Optically Reconfigurable Gate Arrays, IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, pp. 411-419, 2010.

- [12] H. Morita, M. Watanabe, "Relationship between alignment errors of optical components and power consumption in optoelectronic devices," IEEE CPMT Symposium Japan, CD-ROM, 2010.

- [13] H. Morita, M. Watanabe, "A binary MEMS Optically Reconfigurable Gate Array," IEEE/ACIS International Conference on Computer and Information Science, pp. 63-68, 2010.

- [14] H. Morita, M. Watanabe, "Excellent Fault Tolerance of a MEMS Optically Differential Reconfigurable Gate Array," Optical MEMS and Nanophotonics, pp. 133-134, 2010.

- [15] D. Seto, M. Watanabe, "Partial block by-block reconfiguration for a dynamic optically reconfigurable gate array," International Conference on engineering of reconfigurable systems and algorithms, pp. 232-237, July, 2010.

- [16] Y. Aoyama, M. Watanabe, "An acceleration method of optical reconfigurations using analog configuration contexts," NASA/ESA Conference on Adaptive Hardware and Systems, pp. 311-315, 2010.

- [17] D. Seto, M. Watanabe, "Recovery method for a turn-off failure mode of a laser array on an ORGA," NASA/ESA Conference on Adaptive Hardware and Systems, pp. 242-247, 2010.

- [18] D. Seto, M. Watanabe, "MEMS dynamic optically reconfigurable gate array usable under a space radiation environment," International Workshop on Applied Reconfigurable Computing, Lecture Notes in Computer Science, Vol. 5992, pp. 134-144, 2010.

- [19] D. Seto, M. Watanabe, "MEMS inversion/non-inversion dynamic optically reconfigurable gate array," IEEE International Symposium on System Integration, pp. 24-29, 2009.

- [20] H. Morita, M. Watanabe, "MEMS Optically Differential Reconfigurable Gate Array," IEEE International Conference on Electron Devices and Solid-State

- Circuits, pp. 119-122, 2009.

- [21] D. Seto, M. Watanabe, "Fault tolerance analysis of MEMS holographic memory for DORGAS," International Symposium on Micro-NanoMechatronics and Human Science, pp. 33-37, 2009.

- [22] A. Ogiwara, Y. Ochi, M. Miyake, M. Watanabe, T. Mabuchi, F. Kobayashi, "Formation of volume holographic memory using liquid-crystal composites for optically reconfigurable gate array," 15th MICROOPTICS CONFERENCE, pp. 194-195, 2009.

- [23] H. Morita, M. Watanabe, "MEMS Optically Reconfigurable Gate Array," International conference on Field Programmable Logic and its Applications, pp. 511- 515, 2009.

- [24] T. Mabuchi, K. Miyashiro, M. Watanabe, A. Ogiwara, "Fault tolerance of a dynamic optically reconfigurable gate array with a one-time writable volume holographic memory," IEEE International Midwest Symposium on Circuits & Systems, pp. 917-920, 2009.

- [25] M. Nakajima, M. Watanabe, "A sixteen context dynamic optically reconfigurable gate array," NASA/ESA Conference on Adaptive Hardware and Systems, pp. 120-125, 2009.

- [26] T. Mabuchi, K. Miyashiro, M. Watanabe, A. Ogiwara, "Defect tolerance of an optically reconfigurable gate array with a one-time writable volume holographic memory," NASA/ESA Conference on Adaptive Hardware and Systems, pp. 106-111, 2009.

- [27] T. Mabuchi, K. Miyashiro, M. Watanabe, A. Ogiwara, "Optically reconfigurable gate array with a one-time writable holographic memory," International Conference on engineering of reconfigurable systems and algorithms, pp. 307-308, 2009.

- [28] S. Kato, M. Watanabe, "Inversion/ non-inversion implementation for an 11,424 gate-count dynamic optically reconfigurable gate array VLSI," International Symposium on Systems, Architectures, Modeling and Simulation, Lecture Notes in Computer Science, Vol. 5657, pp. 139-148, 2009.

- [29] M. Nakajima, M. Watanabe, "Fast optical reconfigurations of a nine-context DORGA," International Workshop on Applied Reconfigurable Computing, Lecture Notes in Computer Science, Vol. 5453, pp. 123-132, 2009.

### [学会発表] (計 27件)

- [1] 森田, <u>渡邊</u>, 「MEMS ダイナミック光再構成型ゲートアレイにおける MEMS 組立精度」,電子情報通信学会技術研究報告(VLIS 設計研究会),vol.109,no 360,VLD2010-106,pp.151-156,慶応大学,1月,2011.

- [2] 森田, <u>渡邊</u>,「ホログラム閾値可変による MEMS ダイナミック光再構成型ゲートアレイの動作効率改善法」, 第8回情報学ワークショップ(WiNF2010), CD-ROM, 名古屋大学, 12月, 2010.

- [3] 渡辺,<u>渡邊</u>,「ホログラムメモリシステムのレーザーアレイ故障の復旧方法」, 第 54 回宇宙科学技術連合講演会, CD-ROM, 静岡県コンベンションアーツ センター「グランシップ」, 11 月, 2010.

- [4] 森田, <u>渡邊</u>, 「光再構成型ゲートアレイにおける MEMS アドレッシング技術」, 電子情報通信学会技術研究報告(リコンフィギャラブルシステム研究会), vol. 110, No. 204, RECONF2010-30, pp. 73-78, 静岡大学, 9月, 2010.

- [5] 渡辺,<u>渡邊</u>,「光再構成型ゲートアレイのレーザアレイ故障の復旧方法」電子情報通信学会技術研究報告(機構デバイス研究会), vol. 110, No. 178, OPE2010-55, pp. 135-140, 千歳アルカディアプラザ, 8月, 2010.

- [6] 山地, <u>液邊</u>, 「64 コンテキスト MEMS 光再構成型ゲートアレイ」電子情報通信学会技術研究報告(機構デバイス研究会), vol. 110, No. 178, OPE2010-56, pp. 140-144, 千歳アルカディアプラザ, 8月, 2010.

- [7] 間渕,<u>渡邊</u>,<u>荻原</u>,<u>小林</u>,「偏光依存性 ホログラムメモリの偏光スイッチング を用いた光再構成試験」,平成22年度 電気関係学会東海支部連合大会,CD-ROM, 中部大学,8月,2010.

- [8] 瀬戸, <u>渡邊</u>, 「ダイナミック光再構成型 ゲートアレイのレーザー故障回避」, 第57回応用物理学関係連合講演会 講 演予稿集, 東海大学湘南キャンパス, p. 03-112, 3月, 2010.

- [9] 間渕,越智,<u>渡邊</u>,<u>荻原</u>,<u>小林</u>,「偏光 依存性ホログラムメモリを用いた光再 構成試験」,第57回応用物理学関係連合 講演会 講演予稿集,東海大学湘南キ ャンパス,p. 03-087,3月,2010.

- [10] <u>**荻原**</u>, 越智, <u>**渡邊**</u>, 間渕, <u>小林</u>, 「液晶を用いた光再構成型ゲートアレイ用異方性ホログラムメモリの作製」, 第 57 回応用物理学関係連合講演会 講演予稿集, 東海大学湘南キャンパス, p. 12-232, 3 月, 2010.

- [11] 森田, 渡邊, 「差分光再構成手法に対す

- る不良耐性」,電子情報通信学会技術研 究報告 (画像工学研究会), vol. 109, No. 469, IE2009-192, pp. 77-82, 東北大学, 3月、2010.

- [12]瀬戸,<u>渡邊</u>,「MEMS を用いた反転・非反 転ダイナミック光再構成型ゲートアレ イ」,電子情報通信学会技術研究報告(リ コンフィギャラブルシステム研究会), Vol. 109, No. 320, RECONF2009-43, pp. 7-12, 高知文化プラザ, 12月, 2009.

- [13] 森田, 渡邊, 「ディジタルミラーデバイ スを用いた差分光再構成型ゲートアレ イ」電子情報通信学会技術研究報告(信 号処理研究会), Vol. 109, No. 226, SIP2009-56, pp. 1-5, 福井県 芦原温泉, 10月,2009.

- [14] 瀬戸,**渡邊**,「MEMS ダイナミック光再構 成型ゲートアレイの不良耐性」,電子情 報通信学会技術研究報告(VLSI 設計技術 研究会), Vol. 109, no. 201, VLD2009-42, pp. 71-76, 大阪大学, 9月, 2009.

- [15] 間渕, 宮城, 渡邊, 荻原, 「不揮発性液 晶ホログラムメモリを用いた光再構成 型ゲートアレイの不良耐性」,第 53 回 宇宙科学技術連合講演会, CD-ROM, 京 都大学, 9月, 2009.

- [16] 森田,<u>渡邊</u>,「MEMS を使用した光再構成 技術」, 第 53 回宇宙科学技術連合講演 会, CD-ROM, 京都大学, 9月, 2009.

- [17] 瀬戸**,渡邊**,「MEMS を用いたダイナミッ ク光再構成型ゲートアレイ」, 平成 21 年度電気関係学会東海支部連合大会, CD-ROM, 愛知工業大学, 9月, 2009.

- [18] 森田, <u>渡邊</u>, 「デジタルミラーデバイス を用いた 4 コンテキスト光再構成」, 電子情報通信学会技術研究報告(光エレ クトロニクス研究会), vol. 109, no. 173, OPE2009-81, pp. 37-40, 東北大学, 8月,2009.

- [19] 間渕,宮城,<u>渡邊</u>,<u>荻原</u>,「不揮発性液 晶ホログラムメモリを用いたダイナミ ック光再構成型ゲートアレイの故障耐 性」, 電子情報通信学会技術研究報告(回 路とシステム研究会), vol. 109, no. 110, CAS2009-20, pp. 109-112, 釧路市 生涯学習センター, 7月, 2009.

- [20] 森田, <u>渡邊</u>, 「デジタルミラーデバイス を用いた光再構成」, 電子情報通信学会 技術研究報告(回路とシステム研究会), vol. 109, no. 110, CAS2009-21, pp. 113-116, 釧路市生涯学習センター, 7 月,2009.

- [21] 間渕, 宮城, <u>渡邊</u>, <u>荻原</u>, 「不揮発性液 晶ホログラムメモリを用いたダイナミ ック光再構成型ゲートアレイ」, LSI とシ ステムのワークショップ, pp. 277-279, 北九州国際会議場, 5月, 2009.

- [22] 森田, **渡邊**, 「光再構成型ゲートアレイ の組み立て誤差・総合補正手法」, LSI とシステムのワークショップ, pp. 286-288, 北九州国際会議場, 5 月, 2009.

- [23] 瀬戸, 渡邊,「11,424 ゲートダイナミッ ク光再構成型ゲートアレイへの多数決 回路実装 」,第 56 回応用物理学関係 連合講演会 講演予稿集, 筑波大学, p., 3月,2009.

- [24] 中島, 渡邊, 「16 コンテキスト光再構成 型ゲートアレイ」、電子情報通信学会技 術研究報告(回路とシステム研究会), vol. 108, no. 453, CAS2008-111, pp. 61-65, 岐阜長良川温泉国際会議場, 3 月, 2009.

- [25] 間渕,宮城,**渡邊,荻原**,「不揮発性液 晶ホログラムメモリを用いた光再構成 型ゲートアレイ」、電子情報通信学会技 術研究報告(回路とシステム研究会), vol. 108, no. 453, CAS2008-112, pp. 67-70, 岐阜長良川温泉国際会議場, 3 月, 2009.

- [26]瀬戸,渡邊,「ダイナミック光再構成型 ゲートアレイのゲートアレイ部の性能 評価」, 電子情報通信学会技術研究報告 (集積回路研究会), vol. 108, no. 347, ICD2008-117, pp. 73-78, 東工大(大岡 山), 12月, 2008.

- [27] 中島, **渡邊**,「13. 75ns 高速ホログラム光 再構成」, 電子情報通信学会技術研究報 告(シリコン材料・デバイス研究会), vol. 108, no. 292, SDM2008-171, pp. 15-19, 機械振興会館, 11 月, 2008.

[その他]

ホームページ等

http://www.ipc.shizuoka.ac.jp/~tmwatan/

- 6. 研究組織

- (1)研究代表者

渡邊 実 (Minoru Watanabe) 静岡大学・工学部・准教授

研究者番号:30325576

(2)研究分担者

小林 史典 (Fuminori Kobayashi)

九州工業大学・システム創成情報工学研究 系·教授

研究者番号:60134970

荻原 昭文(Akifumi Ogiwara) 神戸市立工業高等専門学校 電子工学科・ 教授

研究者番号:00342569

(3)連携研究者 無し