# 科学研究費補助金研究成果報告書

平成 23年 6月 24日現在

機関番号:34315

研究種目:基盤研究(C) 研究期間:2008~2010 課題番号:20560340 研究課題名(和文)

電子ビーム直描による耐タンパ性を備えた個人認証用ビアプログラムデバイスの研究研究課題名(英文) Via programmable logic device with tamper resistance fabricated by EB direct writing technique applied for user authentication

研究代表者

藤野 毅 ( FUJINO TAKESHI )

立命館大学・理工学部・教授

研究者番号:60367993

# 研究成果の概要(和文):

本研究では,電子ビーム直描を用いて多品種少量生産システム LSI を低コストで設計・製造できる手法に関する研究を行った.具体的には,2~3層のビア工程を変更するだけで,任意のロジックを構成することが可能な,ビアプログラマブルASIC アーキテクチャ VPEX を考案し,標準的な ASIC との性能・コストの比較を行った.この結果,性能指標である面積・遅延積 (AD積) は,ASIC の約2倍であり,数万個以下の生涯生産個数の LSI では ASIC より低コストであることが明らかになった.

# 研究成果の概要(英文):

We have studied the LSI fabrication method using EB direct writing, which is cost effective even in the small lifetime production volume. We have proposed the via programmable structured ASIC architecture "VPEX", in which any logic can be programmed by changing only 2-3 via layers . The performance and the cost of VPEX architecture were evaluated compared to standard ASIC architecture. The product of Area and Delay, which is the performance indices, is twice that of ASIC, and the total cost is lower than that of ASIC in the case that the lifetime production volume is less than several ten thousands units.

# 交付決定額

(金額単位:円)

|         | 直接経費      | 間接経費      | 合 計       |

|---------|-----------|-----------|-----------|

| 2008 年度 | 1,100,000 | 330,000   | 1,430,000 |

| 2009 年度 | 1,200,000 | 360,000   | 1,560,000 |

| 2010年度  | 1,200,000 | 360,000   | 1,560,000 |

| 年度      |           |           |           |

| 年度      |           |           |           |

| 総計      | 3,500,000 | 1,050,000 | 4,550,000 |

研究分野:電気電子工学

科研費の分科・細目:電気電子工学、電子デバイス、電子機器

キーワード: 半導体超微細化 先端機能デバイス 電子ビーム描画 プログラマブルロジック サイドチャネルアタック

## 1.研究開始当初の背景

半導体集積回路の微細化の進展によって 大容量のメモリとマイクロプロセッサなど のロジック回路を含む電子システムを、1チップの大規模集積回路(LSI)上に実現することが可能になった.このような「システム LSI」は、小型低消費電力かつ高性能な電子情報システムの実現に必須の技術となっている.

しかしながら,最先端のシステムLSIは非常に多額の初期開発費用が必要になっている.特に回路転写(フォトリソグラフィー)用の

原版であるフォトマスク費用は1億円以上と高額となっており,この費用負担によって, 多品種少量生産システムLSIの開発が非 常に困難となっている.

少量生産システムLSIの低コスト化を進める 方法として,フォトマスクを使用しない電子 ビームウエハ直接描画(EB直描)技術が注 目されているが,ウエハを処理する速度が低 く,実用化に至っていない.

# 2.研究の目的

本研究では,多品種少量生産システム LSI を経済的に設計・製造できる手法に対する解決方法を研究する.具体的には,上述の EB 直描技術を用いて,EB 直描技術に最適化した LSI 設計技術を構築することにより,EB 直描技術によるウエハ処理速度を飛躍的に向上させることを研究の目的としている.

# 3.研究の方法

われわれの提案する,ビアプログラマブルロジック VPEX は,基本素子として 2 入力排他的論理和 ( EXOR ) を用い,第 1 ビア層と第 3 ビア層によって回路論理を決定する等の基本アーキテクチャは固まった.本 VPEX 技術は,米国電気電子学会 IEEE が主催する,Custom Integrated Circuits Conference にて論文が採択され,2007 年 9 月に米国サンノゼで発表し,その新規性 ( EXOR ゲートを用いていること,EB 直描にレイアウト最適化していること)と有効性 ( EXOR ゲートを用いた基本論理素子が,面積が小さく,低消費電力かつ高速であること)は認められた.

上記の VPEX ビアプログラマブルロジック研究成果を,自動設計ツールの研究やデバイス試作を通じてさらに進展させていくとともに,本技術を個人認証デバイスに使用する際に必要となる暗号回路の耐タンパ性に関する研究・無線電力転送およびインターフェースに関する研究を行う.具体的には次の(1)~(4)の項目を検討する.

(1) VPEX グローバルアーキテクチャの研究 VPEX の基本ロジックエレメントアーキテクチャをベースとして,基本素子間の配線手法などのグローバルアーキテクチャを改良し,より小面積で高速なアーキテクチャの研究を行う.

(2)ビアプログラマブルロジック用自動設 計ツールの研究

上記のロジックエレメントに対して,実際に所望の回路を実装する上で,それぞれの素子に回路を割り当てていくための自動設計ツールの研究を行う.

# (3) VPEX デバイス試作と動作検証

新しく提案したLSIアーキテクチャが有効であることを示すためには、やはり実デバイス(LSI)による動作の実証が必要となる.現在,ローム 0.18 µmCMOSのデザインルールを用いてレイアウト設計に着手しており、小規模な回路を搭載した実証LSIチップを,東京大学大規模集積システム設計教育研究センター(VDEC)を通して試作依頼する予定である.試作LSIの製造完了は来年度となり、チップの評価および評価結果をフィードバックしたより大規模なチップを再試作・評価を実施していく.

(4)暗号回路の耐タンパ性に関する研究暗号回路を実装した個人認証用デバイスでは,図2に示すように,暗号処理を実行している際の消費電力を解析することによりその暗号処理に使用している暗号鍵を推定するという「電力差分攻撃(DPA)によるサイドチャネルアタック」が問題となっている.当研究室でも,DPAに対する耐タンパ性を備えた回路の基礎検討を開始しており,「ドミノ型 RSL (Random Switching Logic)回路」を新しく考案した.今後, VPEX 技術にドミノ型 RSL の技術を取り込んだ VPEX の耐タンパ性技術に関して研究を行う.

#### 4. 研究成果

(1) VPEX グローバルアーキテクチャの研究

# <2008 年度>

・VPEX の改良型アーキテクチャ VPEX2 の検討を行い,ディジタル回路の構成に必須な D-FFの面積を半減するロジックエレメントを採用することで,平均チップ面積を 20%削減できることを示した.

#### <2009 年度>

・VPEX の改良型アーキテクチャ VPEX2 では、レイアウトの最適化およびロジックエレメント構成素子の追加により、目的とする回路を構成したときのチップ面積の削減および演算性能の向上を実現した。本 VPEX2 アーキテクチャのロジックエレメント構造を特許出願するとともに、査読付き国際会議で発表した。

# <2010年度>

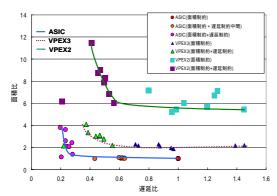

・VPEX の新改良型アーキテクチャ VPEX3 のアーキテクチャを考案した.ロジックエレメント構成素子の削減とレイアウトの抜本的見直し,およびプログラムレイアウトしてビア3層を使用することにより,目的とする回路を構成したときのチップ面積が昨年度のVPEXと比較して約1/3に削減できることが明らかになった.本新アーキテクチャは英文論文誌に投稿・査読中である.

図1.新VPEX3アーキテクチャの評価結果

# (2)ビアプログラマブルロジック用自動設計ツールの研究

# <2008年度>

・VPEX を使ったチップ作成のための設計自動 化ツールの検討を行い,ロジックエレメント への自動配置およびロジックエレメント間 の配線を行う自動設計ツールのプロトタイ プを完成させた.

#### <2009 年度>

・VPEX2 に対応した設計自動化ツール (HDL 記述よりレイアウトを自動生成するための自動配置配線ツール)を作成した.本ツールを使用して, VPEX2 の配線アーキテクチャの検討を行った.

#### <2010年度>

・VPEX3 に対応した設計自動化フロー(HDL 記述よりレイアウトを自動生成するための 自動配置配線ツール)を構築した.カナダ の University of British Columbia との研 究交流により,アメリカの大学が開発した 自動配置ツール Capo と概略配線ツール FGR を VPEX3 の設計フローに取り込むことが可 能になり,VPEX3 アーキテクチャの性能評 価を正確に行うことができるようになった.

# (3) VPEX デバイス試作と動作検証

# <2008 年度>

・VPEX 技術(VPEX1)を使用して,ローム 0.18  $\mu$  mCMOS のデザインルールを用いてレイアウト作成を行い,チップ試作をおこなった.試作したチップは,FPGA ボードを用いて正常動作・電気的特性の評価を行った結果,基本論理素子の正常動作を確認した.

# <2009 年度>

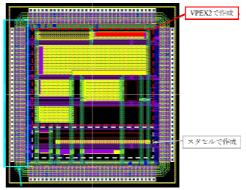

VPEX2 アーキテクチャを用い,ローム社 0.18 µ mCMOS プロセス上で配線遅延評価テストチップの設計を行った.通常の ASIC と比較した場合の配線遅延比較および,VPEX2 で

採用している長距離配線用 BW(Bridge Wire) 配線の効果を検討した .

#### <2010年度>

ビアプログラマブルロジックにおいては,配線経路中のビア個数の増大に伴う抵抗の増加,配線経路上以外の余分な冗長配線上の寄生容量によって,ASICと比較して,配線における信号遅延が増加する.この影響を定量的に評価するために,ローム社 0.18 μ mCMOS プロセス上で配線遅延評価テストチップのリングオシレータにより評価を行った.その結果と,上記 CAD ツールを用いて作製したチップレイアウトから,ビアプログラマブルロジックの配線遅延の定量的評価を行い,通常のASIC に対して,約1.5 倍の仮想配線容量を持つことを明らかにした.

図2. ビアプログラマブル配線評価テストチップ

### (4)暗号回路の耐タンパ性に関する研究

# <2008年度>

・VPEX 技術の応用アプリケーションとして,暗号処理回路を検討しているが,暗号処理を実行している際の消費電力を解析することによりその暗号処理に使用している暗号鍵を推定するという「電力差分攻撃(DPA)によるサイドチャネルアタック」対策が問題となっている.われわれの提案する「ドミノ型RSL(Random Switching Logic)回路」回路がサイドチャネルアタックに耐性があることをシミュレーションにより確認した.

#### <2009 年度>

・VPEX 技術の応用アプリケーションとして、暗号処理回路を検討しているが、暗号処理を実行している際の消費電力を解析することによりその暗号処理に使用している暗号鍵を推定するという「電力差分攻撃(DPA)によるサイドチャネルアタック」対策が問題となっている。本サイドチャネル攻撃に対する耐性すなわち「耐タンパ性」に対して検討を行い、われわれの考案した「ドミノ RSL 回路」を用いることにより耐タンパ性が実現できることを FPGA 評価ボード上で検証した。

# <2010年度>

2009 年度 9 月より, JST/CREST の「ディペンダブル VLSI システムの基盤技術」において,「耐タンパディペンダブルVLSIシステムの開発・評価」のテーマで研究代表者として採択された.したがって 2010 年度以降の耐タンパ性に関する研究成果に関しては,その多くを JST/CREST の成果とみなせるため,省略する.

# 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## [雑誌論文](計11件)

著書名:北森達也、堀遼平、上岡泰輔、吉川雅弥、藤野毅、論文標題:ビアプログラマブルデバイス VPEX における配線リソースと配線遅延の評価、雑誌名:電子情報通信学会技術研究報告書、査読:無、巻:VLD2010-147、発行年:2011、ページ:183-188

著書名:上岡泰輔、北森達也、堀遼平、吉川雅弥、藤野毅、論文標題:ビアプログラマブルASICアーキテクチャ VPEX3の面積と遅延評価、雑誌名:電子情報通信学会技術研究報告書、査読:無、巻:VLD2010-146、発行年:2011、ページ:177-182

著書名:岩井克彦、小島憲司、汐崎充、 浅川俊介、藤野毅、論文標題:Domino-RSL 方式を用いたDPA 耐性を持つDES 暗号回 路の設計試作と安全性評価、雑誌名:電 子情報通信学会技術研究報告書、査読: 無、巻:VLD2010-126、発行年:2011、ペ ージ:57-62

著書名:堀遼平、北森達也、上岡泰輔、吉川雅弥、藤野毅、論文標題:ビアプログラマブルストラクチャードASIC・VPEXの新アーキテクチャ提案と性能評価、雑誌名:電子情報通信学会技術研究報告書、査読:無、巻:ICD2010-91、発行年:2010、ページ:49-62

著書名:西本智広、北森達也、國生雄一、 山田翔太、藤野毅、吉川雅弥、論文標題: ビアプログラマブルデバイス VPEX の配 線遅延評価、雑誌名:電子情報通信学会 技術研究報告書、査読:無、巻: VLD2009-109、発行年:2010、ページ:61-66 著書名:堀遼平、國生雄一、西本智広、 山田翔太、吉田直之、藤野毅、吉川雅弥、 に最適な基本論理ゲートアーキテクチャ の検討、雑誌名:電子情報通信学会技術研究報告書、査読:無、巻:VLD2009-108、 発行年:2010、ページ:55-60

著書名:山田翔太、國生雄一、西本智広 、吉田直之、堀遼平、松本直樹、北森達 也、<u>藤野毅</u>、吉川雅弥、論文標題:ビア プログラマブルデバイスVPEXのロジッ クアレイブロックと配線アーキテクチ ャの検討、雑誌名:電子情報通信学会技 術研究報告書、査読:無、巻: VLD2009-107、発行年:2010、ページ:45-54 著書名:川原崎正英、西本智広、國生雄 一、北村一真、山田翔太、吉川雅弥、藤 野毅、論文標題:ビアプログラマブルデ バイス VPEX のチップ評価と DES 暗号回路 実装の検討、雑誌名:電子情報通信学会 技術研究報告書、査読:無、巻: VLD2008 139、発行年:2009、ページ:77 - 82 著書名:國生雄一、川原崎正英、石橋宏 太、西本智広、北村一真、吉川雅弥、藤 野毅、論文標題:ビアプログラマブルロ ジックデバイスVPEXにおける自動配置ツ ールの開発と性能評価、雑誌名:電子情 報通信学会技術研究報告書、査読:無、 巻:ICD2008-123、発行年:2008、ページ : 107-112

著書名:西本智広、川原崎正英、長谷川英司、寺川知宏、<u>藤野毅</u>、論文標題:ビアプログラマブルデバイスVPEXのロジックエレメント改良による面積削減と高性能化、雑誌名:電子情報通信学会技術研究報告書、査読:無、巻:ICD2008-122、発行年:2008、ページ:101-106著書名:A.Nakamura, M.Kawaharazaki, M.Yoshikawa, T.Fujino,論文標題:Regular Fabric of Via Programmable Logic Device using EXclusive-or Array (VPE X) for EB Direct Writing、雑誌名:IE ICE TRANS. ELECTRON、査読:有、巻:Vol.E91-CNo.4、発行年:2008、ペー

# [学会発表](計13件)

ジ:509-516

発表者名: 上岡泰輔、北森達也、堀遼平、吉川雅弥、<u>藤野毅</u>、発表標題: ビアプログラマブルASICアーキテクチャ VPEX3の面積と遅延評価、学会名:電子情報通信学会 VLSI 設計技術研究会、発表年月日:2011年3月3日、発表場所:沖縄県男女共同参画センター「ているる」那覇市(沖縄県)

発表者名: 北森達也、堀遼平、上岡泰輔、吉川雅弥、藤野毅、発表標題: ビアプログラマブルデバイス VPEX における配線リソースと配線遅延の評価、学会名:電子情報通信学会 VLSI 設計技術研究会、発表年月日: 2011 年3月3日、発表場所:沖縄県男女共同参画センター「ているる」那覇市(沖縄県)

発表者名: 堀遼平、北森達也、上岡泰輔、

吉川雅弥、藤野毅、発表標題:ビアプログラマブルストラクチャード ASIC・VPEX の新アーキテクチャ提案と性能評価、学会名:電子情報通信学会集積回路研究会、発表年月日:2010年11月29日、発表場所:九州大学 福岡市(福岡県) 発表者名:M.Yoshikawa、Y.Kokusyo、T.Fujino、発表標題:Placement Tool Dedicated for a Via-programmable Logic Device VPEX、学会名:Proc. of 23rd International Conference on Computer Applications in Industry and Engineering、発表年月日:2010年11月8日 発表提所:ラスベガス アメリカ

8日、発表場所:ラスベガス アメリカ 発表者名:Kenji Kojima、Kazuki Okuyama、 Katsuhiro Iwai、Mitsuru Shiozaki、 Masaya Yoshikawa、Takeshi Fujino、発 表標題:LSI Implementation Method of DES Cryptographic Circuit utilizing Domino-RSL Gate Resistant to DPA Attack、学会名:The 16th Workshop on Synthesis And System Integration of Mixed Information technologies、発表 年月日:2010年10月18日、発表場所: 台北市(台湾)

発表者名:山田翔太、國生雄一、西本智 広、吉田直之、堀遼平、松本直樹、北森 達也、藤野毅、吉川雅弥、発表標題:ビ アプログラマブルデバイスVPEXのロジッ クアレイブロックと配線アーキテクチャ の検討、学会名:電子情報通信学会VLSI 設計技術研究会、発表年月日:2010年3 月3日、発表場所:沖縄県男女共同参画セ ンター「ているる」 那覇市(沖縄県) 発表者名:西本智広、北森達也、國生雄 -、山田翔太、<u>藤野毅</u>、吉川雅弥、発表 標題:ビアプログラマブルデバイス VPEX の配線遅延評価、学会名:電子情報通信 学会 VLSI 設計技術研究会、発表年月日: 2010年3月3日、発表場所:沖縄県男女 共同参画センター「ているる」那覇市(沖 縄県)

発表者名: 堀遼平、國生雄一、西本智広、山田翔太、吉田直之、<u>藤野毅</u>、吉川雅弥、発表標題: ビアプログラマブルデバイスに最適な基本論理ゲートアーキテクチャの検討、学会名:電子情報通信学会 VLSI設計技術研究会、発表年月日:2010年3月3日、発表場所:沖縄県男女共同参画センター「ているる」 那覇市(沖縄県)発表者名: Takeshi Fujino、Tomohiro Nishimoto、Yuichi Kokusyo、 Masaya Yoshikawa、Guy Lemieux、発表標題: Via-programmable Logic Array VPEX2 with Configurable DFF using 2 Logic Elements、学会名: The 12th International Symposium on Integrated

Circuits, B1.2、発表年月日:2009年12 月14日-16日、発表場所:シンガポール( シンガポール)

発表者名: Kazuma Kitamura、Syouta Ya mada、Masahide Kawarasaki、Yuuichi K okusyou、Usman Ahmed、Guy Lemieux、M asaya Yoshikawa、<u>Takeshi Fujino</u>、発表標題: Interconnect Utilization of the VPEX Via-Programmable Structured ASIC、学会名: The 15th Workshop on Synthesis And System Integration of Mixed Information technologies、発表年月日: 2009年3月9日、発表場所:沖縄パシフィックホテル 那覇市(沖縄県)

発表者名:川原崎正英、西本智広、國生雄一、北村一真、山田翔太、吉川雅弥、藤野毅、発表標題:ビアプログラマブルデバイス VPEX のチップ評価と DES 暗号回路実装の検討、学会名:電子情報通信学会 VLSI 設計技術研究会、発表年月日:2009年3月、発表場所:沖縄県男女共同参画センター「ているる」那覇市(沖縄県)

発表者名:西本智広、川原崎正英、長谷川英司、寺川知宏、<u>藤野毅</u>、発表標題:ビアプログラマブルデバイス VPEX のロジックエレメント改良による面積削減と高性能化、学会名:電子情報通信学会集積回路研究会、発表年月日:2008 年 12月11日、発表場所:東京工業大学(東京都)

発表者名:國生雄一、川原崎正英、石橋 宏太、西本智広、北村一真、吉川雅弥、 藤野毅、発表標題:ビアプログラマブル ロジックデバイス VPEX における自動配 置ツールの開発と性能評価、学会名:電 子情報通信学会集積回路研究会、発表年 月日:2008年12月11日、発表場所:東京工業大学(東京都)

[図書](計0件)

〔産業財産権〕 出願状況(計1件)

名称:半導体装置およびその製造方法

発明者:藤野 毅 権利者:立命館大学

種類:特許

番号:特願 2009-134429 出願年月日:2009年6月3日

国内外の別:国内

取得状況(計0件)

[その他]

# ホームページ等

http://www.ritsumei.ac.jp/se/re/fujinol

ab/

# 6 . 研究組織

(1)研究代表者

藤野 毅 ( FUJINO TAKESHI ) 立命館大学・理工学部・教授

研究者番号:60367993

- (2)研究分担者 なし

- (3)連携研究者 なし