# 科学研究費助成事業 研究成果報告書

令和 6 年 6 月 1 2 日現在

機関番号: 13901

研究種目: 基盤研究(B)(一般)

研究期間: 2020~2022

課題番号: 20H04155

研究課題名(和文)光と電子が密に融合する集積回路のアーキテクチャと設計技術

研究課題名(英文)Research on architecture of optoelectronic integrated circuits and their design methodology

研究代表者

石原 亨(Ishihara, Tohru)

名古屋大学・情報学研究科・教授

研究者番号:30323471

交付決定額(研究期間全体):(直接経費) 13,500,000円

研究成果の概要(和文):本研究課題は、光と電子が密に融合する光電融合集積回路のアーキテクチャと設計技術を構築することにより、光電融合集積回路における遅延-電力-面積のトレードオフ限界を明確にし、光電融合集積回路の最適な構成を明らかにするものである。上記目的のために、初年度は、光電融合集積回路の回路遅延、消費電力、回路面積の見積もりモデルを作成した。2021年度は上記モデルに基づいて光信号の多重化による並列演算技術および各種低消費電力化技術を光ニューラルネットワーク回路に適用する手法を構築した。前年度までの成果に基づき、最終年度は光電融合リカレントニューラルネットワーク(RNN)を考案し、その評価を行った。

研究成果の学術的意義や社会的意義本研究課題は、世界に先駆けて光電融合集積回路に対する遅延、電力、面積のモデルを構築し、そのモデルに基づいて光電融合集積回路を最適設計する手法を構築した。また、光電融合集積回路を深層ニューラルネットワークに適用し、光ニューラルネットワークの最適なアーキテクチャを明らかにした。具体的には、光電融合集積回路に基づくリカレントニューラルネットワーク(RNN)アーキテクチャを開発した。光ニューラルネットワークの開発は、AI推論処理を超低遅延化し省エネルギー化する技術として学術的かつ社会的意義の高い先駆的な研究成果である。今後ますます大量のデータが超広帯域で流通する情報化社会に必要不可欠な研究成果である。

研究成果の概要(英文): This research project aims to clarify the Pareto-optimal boundary for delay-power-area in optoelectronic integrated circuits by building architecture and design technology for optoelectronic integrated circuits in which photonic and electronic circuits are closely integrated. The purpose of this study is to clarify the optimal configuration of the optoelectronic integrated circuits. For this purpose, in the first year, we created a model for estimating circuit delay, power consumption, and circuit area of the optoelectronic integrated circuits. In FY2021, we developed a method to apply parallel computing technology based on Wavelength Division Multiplexing (WDM) and various low power consumption methods developed in past research to optical neural network circuits. Based on the results achieved up to the previous year, in the final year we devised and evaluated a optoelectronic recurrent neural network (RNN) architecture.

研究分野: 計算機システム

キーワード: 計算機システム 光電融合回路 光二ューラルネットワーク

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

#### 1.研究開始当初の背景

本研究課題 は、今日の高 性能コンピュ ータを実現す るエレクトロ

ニクス技術と 高速通信を担

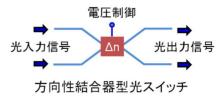

旧来の光スイッチ: サイズ・遅延とも大 素子長=10mm、伝搬遅延時間=100ps

ナノフォトニクスに基づく光スイッチ: 素子長=100 μ m、伝搬遅延時間=1ps

うフォトニクス技術を有機的に融合させることによって全く新しい光電融合集積回路を構成すると同時に、光電融合集積回路に対する設計手法を開拓するものである。光スイッチや光配線等のフォトニクス技術は今日の高速通信を支える必須技術であるが、これらの技術を"通信"ではなく"演算処理"に応用する研究はほとんど行われていない。また、光と電子が密に融合する集積回路の設計手法に関する研究もほとんど行われていないのが現状である。今日実用化されている光配線や光スイッチのサイズは集積回路(以下 LSI)中の素子と比べて 6 桁から 8 桁程度大きいため、光スイッチの高集積化が極めて難しいことが理由の一つと考えられる。しかし、2000 年を過ぎた頃からフォトニック結晶に代表されるナノフォトニクス技術が急速に発展し、光スイッチを超小型化して光集積回路として集積化することが可能になった。上図に示すとおり、従来は数 cm 程度の素子長が必要であった光スイッチは、フォトニック結晶を用いることにより光の波長の数倍程度(3~5 μm)まで小型化できるため、光スイッチの信号伝搬時間を 100 fs 程度まで小さくできる目途が立ちつつある。これは、従来の CMOS ゲートの伝播遅延時間の 1/100~1/50 に相当する。

研究代表者は過去の研究の中で、光電融合集積回路に関するいくつかの設計手法を提案した。具体的には、回路面積の削減手法に関しては、波長分割多重方式を用いて光信号を一つの光集積回路上で重畳することにより演算を並列化して高速化するとともに、演算当たりの回路面積を大幅に削減する手法を提案した。光信号が波の性質を持つことから、別波長の複数の光信号を重ねて一つの回路に伝搬させることにより複数の演算を並列で実行できる。本研究課題では、波長分割多重方式以外に位相を操作する並列演算に取り入れてさらなる高性能化と回路面積の低減を達成する方法を検討する。

#### 2.研究の目的

本研究の目的は光と電子が融合する集積回路の最適な構成を明らかにすることである。 ナノフォトニクスの急激な進展に伴い、国内外における光集積回路の EDA 研究が始まって いるが、とりわけ国内では光集積回路に対する EDA 研究はほとんど行われていない。また、 光と電子が融合する集積回路に関しては回路アーキテクチャの研究もほとんど行われてい ないのが現状である。上記の内外の状況を踏まえ、本研究課題では以下の項目を実施し、光 電融合回路の最適なアーキテクチャを明確にすることを目的とする。

1. 光と電子が密に融合する光電融合集積回路を対象とする。光と電子が密に融合する集積回路を対象とした研究は世界的にもほとんど前例がない。過去に実施した応募者の研究結果から、光デバイスは素子遅延や面積効率の観点でアナログ信号を効率よく処理できることが分かっている。一方、CMOS素子に基づく集積回路はディジタル信号を極めて高速かつ高い電力効率で処理できる。したがって、光電融合集積回路では、光を媒体と

するアナログ信号と電気を媒体とするディジタル信号のミックスドシグナルを扱う回路構造が一つの現実解と考えられる。ミックスドシグナル回路に対する研究は長い歴史があるが、本研究課題では、光電融合回路における新たな境界条件の下でミックスドシグナル回路の最適設計手法を検討する。

- 2. 光電融合集積回路のアーキテクチャだけでなく回路遅延と消費電力および回路面積のトレードオフを最適化する設計支援技術の研究に取り組む。光集積回路のアーキテクチャや新規構造に関しては国内外において過去5年間に多数の提案が行われているが、低消費電力化や回路面積低減を目的(あるいは制約)とした設計最適化技術や設計支援技術に関する研究は代表者の知る限りほとんど行われていない。本研究課題では、世界に先駆けて光電融合集積回路に対する遅延、電力、面積のモデルを構築し、そのモデルに基づいて光電融合集積回路を最適設計する研究に取り組む。

- 3. 光電融合集積回路を非ノイマン型コンピューティングに適用し評価を実施する。機械学習やパタン認識あるいは非線形最適化問題の反復解法で使用される演算などは、非ノイマン型コンピューティングに対応し、適切な近似演算(Approximate computing)を導入すれば演算の質を劣化させることなく演算を大幅に簡略化できる場合が多い。本応募課題では、光電融合集積回路をニューラルネットワークなどの非ノイマン型コンピューティングに応用し、光電融合集積回路の有効性を評価する。

本研究課題は、将来の高性能コンピュータを実現するデータ処理機能の中で光演算回路に適した機能と構造を見極め、その機能を光演算回路と CMOS ゲートに基づく光電融合集積回路で構成することにより、超高速データ処理を低い消費電力で実現する光電融合回路のアーキテクチャを構築する。光と電気が密に融合する光電融合の最適な構成を明確にすることが目的である。

### 3.研究の方法

EDA の研究はシステム設計などのフロントエンド設計と、回路合成や配置配線などのバックエンド設計に分けられる。本研究課題ではバックエンド設計に関して回路遅延と消費電力および回路面積のトレードオフを最適化し、設計者のニーズに合った回路を合成する手法の研究に取り組む。このために、まず、光と電子が融合する集積回路の遅延、消費電力、回路面積を見積もるためのモデルを構築する。次に、これらのモデルに基づいた設計最適化技術を構築する。 光集積回路の物理設計技術の研究は後続研究で実施予定である。

上記設計最適化技術の構築と同時に、光集積回路に対する根本的な消費電力の削減技術および回路面積の低減技術を開発する。ナノフォトニクス技術の急速な発展によって、光回路のスイッチングエネルギーは劇的に削減されたが、信号を媒介するレーザ光を生成するための電力はほとんどスケールされていない。一方、光集積回路の低消費電力化には光源となるレーザ光の低消費電力化が鍵となる。すなわち、光回路中で光源の電力を減衰させない回路構造を構築することが光集積回路の低消費電力化にとって重要な鍵となる。そこで、本研究課題では、光集積回路において光の電力減衰を低減する回路構成法を開発する。また、光信号に対する各種多重化方式を適用することにより光を用いた演算を並列化し高速化するとともに、少ない素子数で並列演算を実行する演算方式を開発する。最終的には光ニューラルネットワークなどの非ノイマン型コンピューティング回路を題材としたプロトタイプを設計し、光電融合集積回路の実現可能性と有効性を評価する。

1年目:回路遅延、消費電力、回路面積の見積もりモデル作成

CMOS に基づく電子回路に関しては様々なモデルが構築されているが、ナノフォトニクスに基づく光集積回路の消費電力モデルや回路面積モデルに関しては回路の設計最適化に利用できる実用的なモデルが十分に構築されていない。そこで、光集積回路に関しては、東工大の納富教授と密に協力して現実的なモデル作成に取り組む。CMOS に基づく電子集積回路部分に関しては京都大の塩見助教および名古屋大の増田助教と連携してコンパクトかつ高精度なモデルを構築する。

### 2年目:面積削減技術と低消費電力化技術の開発

代表者が過去に開発した光信号の多重化による並列演算技術および各種低消費電力化手法を拡張する。多重化に関しては既に波長分割多重方式(WDM: Wavelength Division Multiplexing)を活用した並列演算方式を論文発表しているが、波長分割多重方式以外に位相を積極的に操作する技術を活用した光多重並列化手法を検討する。さらに、1年目に開発する遅延・電力・面積のモデルに基づいて、光電融合集積回路を最適に設計するアルゴリズムを開発する。

# 3年目:非ノイマン型演算器を対象とした光電融合回路の評価検証

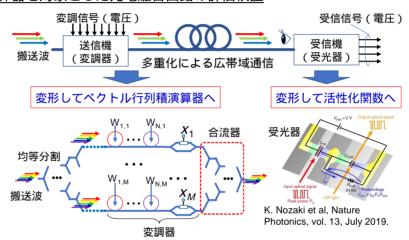

本研究課題実施前の2019年には、右図にオリイマサ電融合の非ノイマン型演算アーキテクの上部は既存の光通信に表する光 NNの概要を、NNの概要を、といいの概率する光 NNの概率する光 NNの概率する光 NNの概率する光 NNの概率するとに示すように光通

信に使用されている多重化や光変調技術および受光技術などさまざまな技術を直接的に採用している。例えば乗算には光変調器を利用し、加算には光の合流干渉を使用している。また、光変調器と光合流器において波長分割多重技術を活用し、波長数と同数の並列アナログ乗算と並列アナログ加算を実行する。光スイッチの高速伝搬性を最大限に活用し、また、波長分割多重方式の光並列性を活用した超高速演算が可能である。本研究課題では、波長分割多重方式以外の位相変復調技術を適用することにより更なる光並列性を活用するとともに、上図のアーキテクチャに代表される非ノイマン型演算に遅延、電力、面積の最適設計を施し、その効果を検証する。

#### 4.研究成果

本研究課題は、光と電子が密に融合する光電融合集積回路のアーキテクチャと設計技術を構築することにより、光電融合集積回路における遅延-電力-面積のトレードオフ限界を明確にし、光電融合集積回路の最適な構成を明らかにするものである。上記目的のために、2020 年度は下記の3項目に取り組み、国際論文誌1件、国際会議2件、国内会議1件の論文発表を行った。

- 1) 回路設計段階で光電融合集積回路の遅延、電力、面積を正確に見積もるモデルを構築

- 2) 光電融合集積回路に対する回路アーキテクチャレベルの設計最適化技術を構築

- 3) 光電融合集積回路をニューラルネットなどの非ノイマン型演算回路に適用し性能を評価

上記3項目を目的として、光電融合集積回路の回路遅延、消費電力、回路面積の見積もりモデルを作成した。特に、光集積回路の電力消費メカニズムは電子回路とは大きく異なるため、電子回路には存在しない光の分岐や合流干渉にともなう電力損失を明らかにし、アーキテクチャレベルの消費電力モデルを構築した。初年度はニューラルネットワークの中で最も単純なモデルである多層パーセプトロンを対象に研究を行った。具体的には、まず、ニューラルネットワークの必須構成要素であるベクトル行列積演算器を光の伝搬によって実現する光演算回路を考案した。次に、そのベクトル行列積演算器を通過する光搬送波の減衰量をモデル化した。また、上述の光演算回路を伝搬する光搬送波の減衰量に基づき、光搬送波の生成に必要なレーザ光源の消費電力を見積もるモデルを構築した。さらには、光ニューラルネットワークの推論精度を劣化させることなく、レーザ光源の消費電力を削減する手法を考案した。一連の研究成果は国内会議1件、国際会議2件、国際論文誌1件で論文発表した。

第2年度目の2021年度は光ニューラルネットワークに波長分割多重を適用しAI推論処理を高性能化する方法を検討し、国際論文誌2件、国際会議1件の論文発表を行った。具体的には代表者が過去に開発した光信号の多重化による並列演算技術および各種低消費電力化手法を光ニューラルネットワーク回路に適用する手法の検討を行った。多重化に関しては既に波長分割多重方式(WDM: Wavelength Division Multiplexing)を活用した並列演算方式を論文発表しているが、2021年度は波長分割多重方式を光ニューラルネットワークに適用して波長数に比例した並列数で積和演算を実行する方法を検討した。また、光ニューラルネットワークにおけるエッジ(枝)の接続をアプリケーションに応じて最適化できる動的再構成可能構造を構築した。具体的には、高度に枝刈りが施されたスパースニューラルネットワークにおいて、エッジ(枝)とノードの接続関係をリング共振器の共振周波数制御によりプログラムする構造を考案した。研究成果はVLSI設計技術関連のトップカンファレンスである Design Automation Conference (DAC) 2021で発表した。

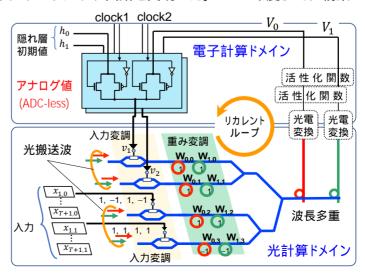

最終年度の 2022 年度は、光ニューラルネットワークの構成を動的に再構成する方法とリカレントニューラルネットワークの構築方法を検討し、国際会議 3 件と国内会議 1 件の論文発表を行った。具体的には、光電融合リカレントニューラルネットワーク (RNN)の設計と評価を行った。RNN を同期式順序回路として実現するために、光変調器の入力容量に電荷を保持するダイナミックラッチを設計した。光を用いた積和演算結果を受光器によって光電変換した後に電子回路で簡単な活性化関数を実現し、その結果をダイナミックラッチに保持する。光電変換によって生成される電荷を入力容量に貯め込む回路構造を用いることで高速かつ超低消費エネルギーなフィードバック回路を実現した。2021 年度までに構築し

た光に基づくベクトル行列積 演算回路と上記のダイナミックラッチを融合させることにより光電融合の RNN を実現した。研究成果は IEEE の国際会議と国内の研究会(回路とシステムワークショップでの発表は奨励賞を受賞した。現在、ジャーナル論文の執筆準備を進めている。

### 5 . 主な発表論文等

「雑誌論文 〕 計10件(うち査読付論文 10件/うち国際共著 0件/うちオープンアクセス 1件)

| 〔雑誌論文〕 計10件(うち査読付論文 10件/うち国際共著 0件/うちオープンアクセス 1件)                                                                                        |                          |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 1.著者名 MATSUO Ryosuke、SHIOMI Jun、ISHIHARA Tohru、ONODERA Hidetoshi、SHINYA Akihiko、NOTOMI Masaya                                           | 4.巻<br>E104.A            |

| 2.論文標題<br>A Synthesis Method Based on Multi-Stage Optimization for Power-Efficient Integrated Optical<br>Logic Circuits                 | 5 . 発行年<br>2021年         |

| 3.雑誌名 IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences                                           | 6.最初と最後の頁<br>1546~1554   |

| 掲載論文のDOI(デジタルオブジェクト識別子)<br>10.1587/transfun.2020KEP0018                                                                                 | 査読の有無<br>有               |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                  | 国際共著                     |

| 1.著者名<br>HATTORI Naoki、SHIOMI Jun、MASUDA Yutaka、ISHIHARA Tohru、SHINYA Akihiko、NOTOMI Masaya                                             | 4.巻<br>E104.A            |

| 2.論文標題<br>Neural Network Calculations at the Speed of Light Using Optical Vector-Matrix Multiplication<br>and Optoelectronic Activation | 5 . 発行年<br>2021年         |

| 3.雑誌名<br>IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences                                        | 6.最初と最後の頁<br>1477~1487   |

| 掲載論文のDOI (デジタルオブジェクト識別子)<br>10.1587/transfun.2020KEP0016                                                                                | 査読の有無<br>  有             |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                  | 国際共著                     |

| 1.著者名<br>服部直樹,増田豊,石原亨,塩見準,新家昭彦,納富雅也                                                                                                     | 4.巻<br>IEICE-VLD2019-137 |

| 2.論文標題<br>集積ナノフォトニクスに基づく光ニューラルネットワークを対象とした回路アーキテクチャ探索                                                                                   | 5 . 発行年<br>2020年         |

| 3.雑誌名<br>第33回 回路とシステムワークショップ論文集                                                                                                         | 6.最初と最後の頁<br>10~15       |

| 掲載論文のDOI (デジタルオプジェクト識別子) なし                                                                                                             | <br>  査読の有無<br> <br>  有  |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                  | 国際共著                     |

| 1.著者名                                                                                                                                   | 4 . 巻                    |

| Shiomi Jun、Ishihara Tohru、Onodera Hidetoshi、Shinya Akihiko、Notomi Masaya                                                                | -                        |

| 2.論文標題<br>An Optical Accelerator for Deep Neural Network Based on Integrated Nanophotonics                                              | 5 . 発行年<br>2020年         |

| 3.雑誌名 Proc. IEEE International Conference on Rebooting Computing                                                                        | 6.最初と最後の頁<br>95~101      |

| 掲載論文のDOI(デジタルオブジェクト識別子)<br>10.1109/ICRC2020.2020.00017                                                                                  | 査読の有無<br>有               |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                  | 国際共著                     |

| 1.著者名<br>Hattori Naoki、Masuda Yutaka、Ishihara Tohru、Shiomi Jun、Shinya Akihiko、Notomi Masaya                                             | 4.巻                    |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 2.論文標題 Optical-electronic implementation of artificial neural network for ultrafast and accurate inference processing                   | 5 . 発行年<br>2021年       |

| 3.雑誌名 Proc. Al and Optical Data Sciences II. International Society for Optics and Photonics                                             | 6.最初と最後の頁<br>415~421   |

| 掲載論文のDOI(デジタルオブジェクト識別子)<br>10.1117/12.2577966                                                                                           | 査読の有無<br>有             |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                  | 国際共著                   |

|                                                                                                                                         |                        |

| 1 . 著者名<br>HATTORI Naoki、SHIOMI Jun、MASUDA Yutaka、ISHIHARA Tohru、SHINYA Akihiko、NOTOMI Masaya                                           | 4 . 巻<br>E104.A        |

| 2.論文標題<br>Neural Network Calculations at the Speed of Light Using Optical Vector-Matrix Multiplication<br>and Optoelectronic Activation | 5 . 発行年<br>2021年       |

| 3.雑誌名<br>IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences                                        | 6.最初と最後の頁<br>1477~1487 |

| 掲載論文のDOI(デジタルオブジェクト識別子)<br>  10.1587/transfun.2020KEP0016                                                                               | 査読の有無 有                |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                  | 国際共著                   |

|                                                                                                                                         | 1 . w                  |

| 1 . 著者名<br>Ichikawa Taisei、Masuda Yutaka、Ishihara Tohru、Shinya Akihiko、Notomi Masaya                                                    | 4.巻                    |

| 2.論文標題<br>Optoelectronic Implementation of Compact and Power-efficient Recurrent Neural Networks                                        | 5 . 発行年<br>2022年       |

| 3.雑誌名<br>Proc. IEEE Computer Society Annual Symposium on VLSI (ISVLSI)                                                                  | 6.最初と最後の頁<br>390~393   |

|                                                                                                                                         |                        |

| 掲載論文のDOI(デジタルオブジェクト識別子)<br>10.1109/ISVLSI54635.2022.00087                                                                               | 査読の有無<br>有             |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難                                                                                                  | 国際共著                   |

| 1 . 著者名<br>Hattori Naoki、Masuda Yutaka、Ishihara Tohru、Shinya Akihiko、Notomi Masaya                                                      | 4 . 巻<br>-             |

| 2.論文標題<br>Power-aware pruning for ultrafast, energy-efficient, and accurate optical neural network design                               | 5 . 発行年<br>2022年       |

| 3.雑誌名<br>Proc. Design Automation Conference (DAC)                                                                                       | 6.最初と最後の頁<br>1285~1290 |

| 掲載論文のDOI(デジタルオブジェクト識別子)<br>10.1145/3489517.3530405                                                                                      | 査読の有無<br>有             |

| オープンアクセス<br>オープンアクセスとしている(また、その予定である)                                                                                                   | 国際共著                   |

| 1.著者名                                  | 4 . 巻     |

|----------------------------------------|-----------|

| 市川大生,増田豊,石原亨,新家昭彦,納富雅也                 | -         |

| 2.論文標題                                 | 5.発行年     |

| 省面積と低電力を両立する光電融合RNN アーキテクチャ            | 2022年     |

| 3.雑誌名                                  | 6.最初と最後の頁 |

| 第35回回路とシステムワークショップ論文集                  | 412~417   |

| 掲載論文のDOI(デジタルオブジェクト識別子)                | 査読の有無     |

| なし                                     | 有         |

| オープンアクセス<br>オープンアクセスではない、又はオープンアクセスが困難 | 国際共著      |

| 1.著者名                                                                                              | 4.巻       |

|----------------------------------------------------------------------------------------------------|-----------|

| Wang Chunlu、Masuda Yutaka、Ishihara Tohru                                                           | -         |

| 2.論文標題                                                                                             | 5.発行年     |

| An optoelectronic pipelined convolutional-RNN architecture for energy-efficient Al accelerator     | 2024年     |

| 3.雑誌名                                                                                              | 6.最初と最後の頁 |

| Proc. 25th Workshop on Synthesis And System Integration of Mixed Information technologies (SASIMI) | 14 ~ 19   |

| 掲載論文のDOI(デジタルオブジェクト識別子)                                                                            | 査読の有無     |

| なし                                                                                                 | 有         |

| オープンアクセス                                                                                           | 国際共著      |

| オープンアクセスではない、又はオープンアクセスが困難                                                                         | -         |

# 〔学会発表〕 計8件(うち招待講演 0件/うち国際学会 6件)

1 . 発表者名

Akihiko Shinya, Kengo Nozaki, Shota Kita, Tohru Ishihara, Shingo Matsuo, Masaya Notomi,

2 . 発表標題

Energy efficient OEO conversion and its applications to photonic integrated systems

3 . 学会等名

IEEE Optical Fiber Communications Conference and Exhibition (OFC) (国際学会)

4.発表年

2022年

1.発表者名

服部直樹,増田豊,石原亨,塩見準,新家昭彦,納富雅也

2 . 発表標題

集積ナノフォトニクスに基づく光ニューラルネットワークを対象とした回路アーキテクチャ探索

3.学会等名

第33回 回路とシステムワークショップ

4 . 発表年

2020年

| 1. 発表者名<br>Shiomi Jun、Ishihara Tohru、Onodera Hidetoshi、Shinya Akihiko、Notomi Masaya                                       |

|---------------------------------------------------------------------------------------------------------------------------|

| 2.発表標題<br>An Optical Accelerator for Deep Neural Network Based on Integrated Nanophotonics                                |

| 3.学会等名<br>IEEE International Conference on Rebooting Computing(国際学会)                                                      |

| 4 . 発表年<br>2020年                                                                                                          |

| 1. 発表者名<br>Hattori Naoki、Masuda Yutaka、Ishihara Tohru、Shiomi Jun、Shinya Akihiko、Notomi Masaya                             |

| 2. 発表標題<br>Optical-electronic implementation of artificial neural network for ultrafast and accurate inference processing |

| 3.学会等名<br>SPIE Conference 11703, AI and Optical Data Sciences II(国際学会)                                                    |

| 4 . 発表年<br>2021年                                                                                                          |

| 1. 発表者名<br>Ichikawa Taisei、Masuda Yutaka、Ishihara Tohru、Shinya Akihiko、Notomi Masaya                                      |

| 2.発表標題 Optoelectronic Implementation of Compact and Power-efficient Recurrent Neural Networks                             |

| 3.学会等名<br>IEEE Computer Society Annual Symposium on VLSI (ISVLSI)(国際学会)                                                   |

| 4 . 発表年<br>2022年                                                                                                          |

| 1. 発表者名<br>Hattori Naoki、Masuda Yutaka、Ishihara Tohru、Shinya Akihiko、Notomi Masaya                                        |

| 2. 発表標題 Power-aware pruning for ultrafast, energy-efficient, and accurate optical neural network design                   |

3 . 学会等名

4 . 発表年 2022年

Design Automation Conference (DAC)(国際学会)

| 1 | <b>双主</b> 字夕 |

|---|--------------|

|   | ,発表者名        |

市川大生, 增田豊, 石原亨, 新家昭彦, 納富雅也

# 2 . 発表標題

省面積と低電力を両立する光電融合RNN アーキテクチャ

# 3 . 学会等名

第35 回回路とシステムワークショップ論文集

#### 4 . 発表年

2022年

# 1 . 発表者名

Wang Chunlu, Masuda Yutaka, Ishihara Tohru

### 2 . 発表標題

An optoelectronic pipelined convolutional-RNN architecture for energy-efficient Al accelerator

### 3.学会等名

Workshop on Synthesis And System Integration of Mixed Information technologies (SASIMI)(国際学会)

#### 4 . 発表年

2024年

#### 〔図書〕 計0件

#### 〔産業財産権〕

〔その他〕

| 6     | . 研究組織                    |                       |    |

|-------|---------------------------|-----------------------|----|

|       | 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |

|       | 塩見 準                      | 大阪大学・情報科学研究科・准教授      |    |

| 研究分担者 | (Shiomi Jun)              |                       |    |

|       | (40809795)                | (14401)               | ,  |

|       | 納富雅也                      | 東京工業大学・理学院・教授         |    |

| 研究分担者 | (Notomi Masaya)           |                       |    |

|       | (50393799)                | (12608)               |    |

| 研究分担者 | 増田 豊 (Masuda Yutaka)      | 名古屋大学・情報学研究科・助教       |    |

|       | (60845527)                | (13901)               |    |

### 7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

# 8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|