#### 研究成果報告書 科学研究費助成事業

今和 5 年 6 月 1 5 日現在

機関番号: 21602

研究種目: 基盤研究(C)(一般)

研究期間: 2020~2022

課題番号: 20K11737

研究課題名(和文)近似計算における設計効率化・低電力化のための回路設計技術

研究課題名(英文)Circuit Design Methodology for Design Efficiency and Low Power Consumption on Approximate Computing

### 研究代表者

小平 行秀 (Yukihide, Kohira)

会津大学・コンピュータ理工学部・上級准教授

研究者番号:00549298

交付決定額(研究期間全体):(直接経費) 3,300,000円

研究成果の概要(和文):本研究では,近似計算を利用することを前提に,論理合成やレイアウト設計に焦点を当て,回路性能の改善や設計時間の短縮のために,論理回路に対して,2 つのネット(ネット対)の併合を適用する集積回路の設計支援システムの開発を行った.開発した手法では,ネット対を併合することで,複数のゲートと複数のネットが削除されることになり,回路規模を削減することができる.開発した手法は,一般的な設計 手法と比べて,セル数,チップ面積,消費電力,動作速度などの回路性能が改善した。

研究成果の学術的意義や社会的意義 開発した手法により,回路性能の改善や設計時間の短縮を実現する集積回路の自動設計技術の向上に貢献した. なお,開発した設計支援システムは,アプリケーションを限定していないため,必ずしも高信頼・高精度での計算が要求されるわけではなく,誤差が含まれることを許るようでは急速を増加される。 して、回路性能の改善や設計時間の短縮を実現できることが期待される。

研究成果の概要(英文): In this research, we focused on logic synthesis and layout design under the assumption that approximate computation is used, and developed a design automation system for integrated circuits that applies the merging of two nets (net pairs) to logic circuits in order to shorten design time and reduce power consumption. The developed method reduced the size of circuits by merging net pairs because the developed system reduced the number of gates and wires by merging net pairs. Compared to general design methods, the developed method improved the circuit performance such as the number of cells, chip area, power consumption, and operating speed.

研究分野: 集積回路設計自動化

キーワード: 集積回路設計自動化 近似計算 レイアウト設計 論理合成

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

# 1.研究開始当初の背景

近年,画像処理や機械学習などの計算量の多いアプリケーションを LSI や FPGA といった集積回路に実装することで,計算の効率化を図る研究が盛んに行われている.これらのアプリケーションは,必ずしも高信頼・高精度での計算が要求されるわけではなく,所望の品質を実現する必要最低限の計算精度で,高速に,低電力で計算することが求められている.そこで,精度に重大な影響を及ぼさない範囲で誤差を含むことを許容し,計算の高速化と低電力化を図る近似計算(Approximate Computing)に関する研究が注目されている.

これまでの近似計算を用いた集積回路設計に関する研究は,論理合成より前の設計工程を対象としており,アルゴリズムの近似,回路アーキテクチャの近似,論理回路の近似に関する研究が多い.前述の通り,近似計算を行うアプリケーションは,計算量の多いものが多く,実装される回路は大規模となる.この大規模な回路を LSI や FPGA に実装する場合,レイアウト設計工程では扱う問題の規模が特に大きくなるため,設計時間は長い.高位合成ツールを利用して C言語や C++から設計し,近似計算を利用する大規模な回路を実装する技術者は,CAD ツールの論理合成やレイアウト設計の工程の高速化を望んでいる.

現在の CAD ツールの論理合成やレイアウト設計の工程は,計算の誤差を許容しない回路を設計することを前提としている.論理合成前の回路とレイアウト設計後の回路が同じ動作をすることを保証するために,様々な設計工程が適用される.一方,計算の誤差を許容する近似計算を利用することを前提に回路を設計した場合,更なる回路の最適化が図られたり,過度な動作保証を省略したりすることで,設計時間の短縮が実現できると期待される.

# 2.研究の目的

本研究では,近似計算を利用することを前提にして,論理合成やレイアウト設計に焦点を当て,論理回路に対して,設計時間の短縮や消費電力の削減のための集積回路の設計技術を開発することを目的とした.

### 3.研究の方法

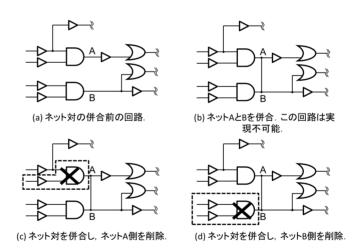

本研究では,論理回路に対し て2 つのネット(ネット対)の 併合を適用することで、ゲート 数や配線数の削減を行う論理回 路の修正手法を検討した(図 1). ネット対の信号値が常に-致している場合,計算誤差を発 生させることなく、そのネット 対を併合することができる.本 研究で検討した近似計算では, ネット対の信号値が多くの時間 で一致している場合も、そのネ ット対を併合する. ネット対の 信号値が一致する時間が長けれ ば長いほど,計算誤差は小さく なると考えられる .ここで ,図1 (a) に示す回路のネット A と

図1 ネット対の併合例.

# 4. 研究成果

検討した手法では、論理合成後のネットリストに対して、ネット対の併合を行う、論理シミ

計算機実験では, 検討した手法の有効 性を示すために,ベン

ネット対の併合後(面積: 414.2µm²).

図2 ネット対の併合前後のレイアウト例.

チマーク回路 47 回路に対して検討した手法により開発した回路の性能と,一般的な設計手法により開発した回路の性能を比較した.検討した手法は,一般的な設計手法と比べて,47 回路の平均で,セル数が 40%,チップ面積が 30%,消費電力が 7%削減され,回路の動作速度が 15%改善した.また,20,000 ゲート程度の規模の回路において,レイアウトの設計時間が 35%改善した.一方,ゲート数とクリティカルパス遅延を考慮する 2 つの手法を比較した場合は,どの性能も 1%程度の違いのみであった.

図 2 に検討した手法に得られたレイアウトの例を示す.赤で示された長方形は記憶素子である.検討した手法は,記憶素子の相対的な位置を出来るだけ保ったままでレイアウトを縮小することで,性能のばらつきを抑えることができた.

| 5 . 主な発表論: |

|------------|

|------------|

〔雑誌論文〕 計0件

| ( 学会発表 ) | 計2件 | (うち招待護演     | 0件/うち国際学会 | 0件)   |

|----------|-----|-------------|-----------|-------|

| し子云光仪丿   |     | しょう 1月1寸冊/宍 | リイ ノク国际子云 | VIT / |

| 1 |   | 杂丰 | 老 | Ŋ              |

|---|---|----|---|----------------|

|   | • | 元収 | ъ | $\blacksquare$ |

羽田喜光,小平行秀

2 . 発表標題

近似計算におけるネット対のマージによる回路とレイアウトの設計手法

3 . 学会等名

第33回 回路とシステムワークショップ論文集

4.発表年

2020年

#### 1.発表者名

矢野悠生,野崎慎二,相澤朋英,小平行秀

# 2 . 発表標題

Approximate Computingにおける回路の高速化のためのネット対のマージ手法

# 3 . 学会等名

電子情報通信学会 VLD研究会

# 4.発表年

2023年

〔図書〕 計0件

〔産業財産権〕

〔その他〕

-

6 研究組織

| ь. | . 妍光組織                    |                       |    |

|----|---------------------------|-----------------------|----|

|    | 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |

# 7. 科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|