# 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成25年 5月27日現在

機関番号: 17102 研究種目:基盤研究(A) 研究期間:2009~2012 課題番号:21246061

研究課題名(和文) 形態機能性マイクロ接合によるナノデバイス/СМОS融合型三次元集

積回路の創生

研究課題名 (英文) Creation of Nano-device/CMOS Merged Three Dimensional Integrated

Circuits Using Shape-Functionalized Micro-interconnect

# 研究代表者

浅野 種正 (ASANO TANEMASA)

九州大学・大学院システム情報科学研究院・教授

研究者番号:50126306

### 研究成果の概要(和文):

研究代表者らが考案した先鋭形状をもつマイクロ接合電極の接合機構の解明を行うとともに、 それを発展させて電子機器の省電力化に有効な三次元集積回路を製造するための技術開発を行った. その結果, 従来技術では困難であった非加熱での接合・相互配線を実現し, シリコン半 導体と異なる機能, 材料を集積できることを示した. 応用例として医療など特殊用途に用いる ことができる近赤外線の撮像素子を試作し, 動作させた.

### 研究成果の概要 (英文):

Bonding mechanism of cone-shaped microbump electrode, which was invented by the leader of this project research, has been investigated. Application of the mechanism to development of three dimensional integration of semiconductor circuits has also been investigated. This project achieved room temperature bonding of high density micro interconnect, which was not able to carry out using existing technology. The developed technology has been applied to integration of heterogeneous integration on silicon. As an example, a high-resolution near infrared image sensor has been fabricated using the developed technology.

# 交付決定額

(金額単位:円)

|        | 直接経費         | 間接経費         | 合 計          |

|--------|--------------|--------------|--------------|

| 2009年度 | 25, 900, 000 | 7, 770, 000  | 33, 670, 000 |

| 2010年度 | 4, 800, 000  | 1, 440, 000  | 6, 240, 000  |

| 2011年度 | 3, 800, 000  | 1, 140, 000  | 4, 940, 000  |

| 2012年度 | 2, 000, 000  | 600, 000     | 2, 600, 000  |

| 年度     |              |              |              |

| 総計     | 36, 500, 000 | 10, 950, 000 | 47, 450, 000 |

研究分野:工学

科研費の分科・細目:電気電子工学・電子デバイス・電子機器

キーワード:電子デバイス・集積回路,インターコネクト・パッケージのシステム化応用,センシングデバイス

#### 1. 研究開始当初の背景

情報爆発時代の社会・経済を支え、持続可能で安全・安心な社会システムを将来に繋ぐために、半導体 LSI の飛躍的な高性能化が強

く求められている。一方、LSI はこれまで素子の微細化によって高性能化を達成してきたが、発熱の制限からそれももはや限界が見えてきており、微細化とは別の革新的な高性

能化の概念とそれを具現化する技術を開発することが喫緊の課題である。

回路層を積層して層間を結線する三次元集積回路は、現状の二次元平面に集積化された LSI に比べ、長距離(グローバル)配線の大幅削減、演算の並列化・分散化によるクロック効率の増大などによる低電力・高速の信号処理を実現する革新的な概念を与えるものである。それを具現化する鍵の技術の一つとして、積層回路間を任意の位置で高密度に縦に電気接続する手法を開発する必要がある。

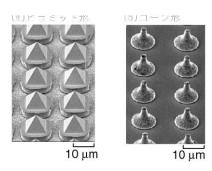

研究代表者らは、積層 LSI チップ間を高密度に電気接続する電極として、先端が先鋭な形状をもつコンプライアント バンプを提唱した(図 1)。このバンプ電極はその形態が発生する機能のため、電極密度、低温接続性、低歪み接合性において従来技術を凌駕する性能をもつ。産業界においてシリコン CMOSの三次元集積化に対する関心高まる中、コンプライアント・バンプ技術に強い関心が寄せられている。

図1 先鋭マイクロバンプ

# 2. 研究の目的

本研究は、コンプライアント・バンプ技術をさらに発展させ、シリコン CMOS と非シリコン系ナノテクノロジーで作製したデバイスを物理的にシームレスに接続を可能にする水準の接合電極技術を開発することを目的とする。

# 3. 研究の方法

援した.

#### 4. 研究成果

#### 4.1 接合温度の低温化

先鋭形状をもつバンプは、単純な圧接だけで接合する場合でも、圧潰時の新生面の生成効果が高いために、接合温度を低温化する効果があることが本研究の開始時点でわかっていた。例えば、Au 製の平坦電極どうしを接合した場合、応用上十分な接合強度を得るには300℃以上の温度が必要であるが、一方をAu のコーン形バンプとするとそれを150℃まで低温化できる。本研究ではさらなる低温化を目指し、以下に述べるような、非加熱、常温で接合可能な二つの新しい方法を開発した

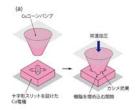

かしめ接合:これは、図 2(a)に示すように、 先鋭形状のバンプに対向する平坦電極に孔 を設けておき、その中に先鋭バンプを先端から押し込む(calking、かしめる)方法である. 言わば、スタッドバンプをプラグ、孔付き対 向電極をソケットに見立てたものである. 先 鋭バンプはその形状から、このかしめ効果を 利用しやすいと類推し、Au/Au および Cu/Cu の組み合わせで実験を行ってみたところい ずれの場合にも常温・大気中での接合を実現 できることがわかった. 図 2(b)に Cu/Cu 電極 で常温接合を実現した接合断面の電子顕微 鏡像を示す.

Au 先鋭バンプ/Au 平坦電極の組み合わせの場合には、平坦電極側の孔は単純な四角形あるいは丸形状で容易に常温接合を実現できたが、Cu/Cu の組み合わせの場合には、単純形状の孔ではかしめ効果が弱いことが判明した。そこで図 2(a)に示すように、相手側電極の開孔を十字形に交差するスリット形状にした。これにより安定した常温接合でできるようになった。接続抵抗は、1 バンプ+1 アルミ線あたり  $83m\Omega$ と、応用を考える上で十分低い値が得られた。

図 2 先鋭マイクロバンプによるかしめ接 合

<u>超音波接合</u>:かしめ効果は接合の低温化に有効ではあるが、その利用には相手側電極に開孔を設けるための微細加工を施すフォトリソグラフィー工程のコストが余分にかかることになる.そこで、接合の低温化に有効であると思われる超音波接合を先鋭バンプに

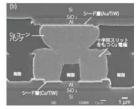

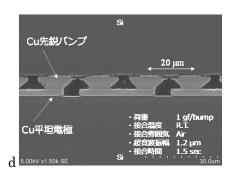

適用してみた.その結果,相手側電極に開孔を設けずとも Au/Au あるいは Cu/Cu の常温接合ができることがわかった.図 3 に Cu/Cu 常温接合の断面を電子顕微鏡で観察した例を示す.先鋭形状の Cu バンプの先端が潰れ,平坦な Cu 電極に接合していることがわかる.デイジーチェーンによる電気抵抗の評価の結果,チップ上に形成したピッチ 20 ミクロン,総数 11,000 個のアレイ状に配置したバンプを無欠陥で接合でき,1 接点当たりの抵抗も 45 m $\Omega$  と十分に低抵抗にできることがわかった.

図 3: Cu 製先鋭バンプを超音波加振して常温で接合した Si チップの断面

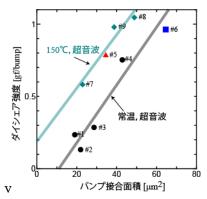

では、熱の効果はどのようなものであろう か. これを調べるために、Au 製の先鋭バンプ を用い, シリコンチップどうしの超音波接合 を常温で実施した場合と 150℃に昇温して接 合した場合のダイシェア強度を比較、測定し た.図4にその結果を示す.この図の横軸は, バンプの接合面積である. これはダイシェア 試験後の剥離面を観察して計測したバンプ の接合面積である. この結果から明らかなよ うに、いずれの場合にもダイシェア強度はバ ンプが実際に接合している面積の増大に比 例して大きくなり、同じ接合面積ならば昇温 した方がダイシェア強度は大きい. これは熱 により接合界面の相互拡散が進行するため, 界面(元のバンプや電極の表面)の汚染物質 による金属間結合の妨害を回避できるため であると解釈できる.

図 4 超音波接合における熱の効果

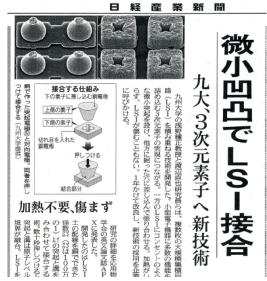

図 5 本研究の成果を報道した新聞記事(日 経産業新聞,平成 23年3月4日)

Cu の常温接合に関する産業界の関心は高く,英文学術雑誌での論文発表の後,新聞でも報道された(図 5).

#### 4.2 異種半導体・異種機能の接合

低温で多ピンの相互接続に対する要望が 高いもうひとつの応用に, 異種半導体間の接 合がある. 要望が高い理由は, 熱膨張係数の 差による接合精度の悪化ならびにひずみの 発生の抑制である. 例えば本研究で試作を目 指したシリコン CMOS と InP 基板上に形成し た金赤外光用フォトダイオードアレイを接 合して作製する近赤外イメージセンサーの 場合, 両者の熱膨張係数の差は約 2ppm であ る. したがって、200℃昇温すると 10mm 角の チップでは  $4\mu$ m の位置ずれが発生すること になる.  $10\sim20\,\mu\,\mathrm{m}$  のピッチで画素が配列さ れるイメージセンサーでは、この位置ずれが 致命的となる. また, 室温に戻したとき発生 するひずみにより、脆弱な InP にクラックが 発生する場合もある.

本研究で開発した Au 先鋭バンプ接合技術を利用して、qVGA (quarter Video Graphic Array, 画素数  $320\times256$ ) の近赤外イメージセンサーの試作に成功した. 図 6 (a) に試作したセンサーの構造模式図を示す. 個々の画素ごとに InP 基板上にヘテロエピタキシャル成長させた InGaAs フォトダイオードとシリコン CMOS 読み出し回路を  $20\,\mu$  m ピッチで接続したものである. 図 6 (b) に試作したイメージセンサーで撮像した近赤外像を示す. 室温動作でも鮮明な画像が得られていることがわかる.

この種のイメージセンサーの製造には従来,インジウムを使ったハンダの溶融接合が用いられており,性能(解像度),信頼性,価格の点で普及の大きな障害になっている.本

# VVVVV

図 6 試作した近赤外イメージセンサーの 構造模式図(a)と撮像例(b). なお, 撮像は非 冷却で撮影.

研究の成果は、この障害をブレークスルーできると期待できる. 最近、超音波の常温接合を用いての近赤外イメージセンサーの試作にも成功しており、医療用途などへの展開が期待できる.

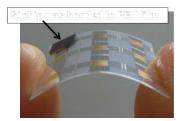

## 4. 3 フレキシブルエレクトロニクスへの展 開

フレキシブルエレクトロニクスやプリンティドエレクトロニクスにはフィルム上の配線にLSIを接合・実装する技術の開発が不可欠である.例えば、フレキシブルなディスプレイを想像した場合、それを人に違和感なく使えるものにするにはワイヤレス化することが必要である.画素の駆動は薄膜トランジスタを用いた回路で実行できるが、ワイヤレスによる外部との情報通信や外部からでまる外部との情報通信や外部がある.動画表示などの場合にはさらに内部にある.動画表示などの搭載も必要になるである。

フレキシブルエレクトロニクス用のフィルム材料としては、透明で安価、強度も高いポリエチレンナフタレート(PEN)がひとつの有望な材料である.一方、PEN のガラス転移

図 7 先鋭バンプ技術により PEN フィルム 上への LSI の常温接合

点は 155℃程度であるため,接合等のプロセス温度はそれ以下に保つ必要がある. LSI の接合のように荷重が加わる場合には,ガラス転移点以下でも PEN の変形が生じ,配線の断線を招く可能性もあるため,常温接合技術が不可欠であると言って良い.

本研究では, 先鋭バンプの特性を活用して PEN フィルム上の配線に LSI チップを常温で マイクロ接合する技術の開発も併せて進め てきた. その結果, かしめ効果を利用した常 温接合,超音波加振の併用による常温接合の いずれの方法でも LSI の接合が可能であるこ とがわかった(図 7). いずれの方法でも約 10,000 接点のバンプ接続を常温で達成して いる. 超音波接合を用いた場合の接合特性に おいて Si チップどうしの接合と異なる特徴 的な点は、同一荷重では PEN 上の接合の方が バンプ接合面積が小さくなる点である. 有限 要素解析の結果より、これは PEN の方が Si に比べ柔軟な分、接合時の PEN 側の変形が大 きいためであると解釈している. フィルム上 の LSI チップの接合で懸念されるのは、接合 強度であるが、調査の結果、強度は電極の接 合面積で決定されることから PEN 上でも十分 な接合強度を得ることができると言える.

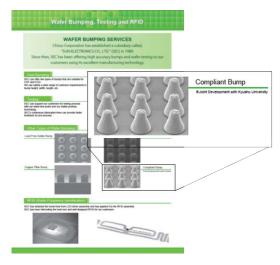

#### 4. 4 実用化への取り組み

本研究の成果は産業界から高い関心を寄せられてきたことから、半導体上へのマイクロ電極製造受託事業を行っている企業への技術移転を併行して進めた。その結果、民間企業の量産用の製造装置を使っても先鋭マイクロバンプを形成できることがわかり、当該企業の製品群の一つとしてカタログ掲載された(図8).

図8 技術を移転した企業(サンエレクトロニクス(株))のカタログに先鋭バンプ技術が掲載

# 5. 主な発表論文等

〔雑誌論文〕(計14件)

- 1. L. Qiu, A. Ikeda, K. Noda, S. Nakai, and T. Asano, "Room-Temperature Cu Microjoining with Ultrasonic Bonding of Cone-Shaped Bump" Jpn. J. Appl. Phys. 52 (2013) 04CB10, DOI: 10.7567/JJAP.52.04CB10.

- 2. T. Shuto, K. Iwanabe, K. Noda, S. Nakai, and <u>T. Asano</u>, "Ultrasonic Bonding of Cone Bump for Integration of Large-Scale Integrated Circuits in Flexible Electronics", Jpn. J. Appl. Phys. 52 (2013) 05DB10, DOI:10.7567/JJAP.52.05DB10.

- 3. <u>浅野種正</u>, "(招待論文)先鋭バンプを用いた異種材料・機能のマイクロ接合技術", 電子情報通信学会論文誌 C J95-C (2012) 148.

- 4. <u>池田晃裕</u>, 仲原清顕, 仇立靖, <u>浅野種正</u>, "自己組織化単分子膜を用いた銅とはんだの フラックスレス接合の研究", 電子情報通信 学会論文誌 C J95-C (2012) 304.

- 5. T. Shuto, N. Watanabe, A. Ikeda, and T. Asano, "Room-Temperature Microjoining of LSI Chips on Poly(ethylene naphthalate) Film Using Mechanical Caulking of Au Cone Bump", Jpn. J. Appl. Phys. 51 (2012) 04DB04, DOI:10.1143/JJAP.51.04DB04.

- 6. X. Yi, G. Nakagawa, H. Ozawa, T. Fujigaya, N. Nakashima, and <u>T. Asano</u>, "Ion Beam Bombardment Effect on Contacts in Solution-Processed Single-Walled Carbon Nanotube Thin Film Transistor", Jpn. J. Appl. Phys. 50 (2011) 098003, DOI:10.1143/JJAP.50.098003.

- 7. X. Yi, H. Ozawa, G. Nakagawa, T. Fujigaya, N. Nakashima, and <u>T. Asano</u>, "Single-Walled Carbon Nanotube Thin Film Transistor Fabricated Using Solution Prepared with 9,9-Dioctyfluorenyl-2,7-diyl-Bipyridine Copolymer", Jpn. J. Appl. Phys. 50 (2011) 070207, DOI:10.1143/JJAP.50.070207.

- 8. T. Shuto, N. Watanabe, A. Ikeda, T. Higashimachi, and <u>T. Asano</u>, "Microjoining of LSI Chips on Poly(ethylene naphthalate) Using Compliant Bump", Jpn. J. Appl. Phys. 50 (2011) 06GM05,

DOI:10.1143/JJAP.50.06GM05.

- 9. N. Watanabe, and <u>T. Asano</u>, "Room-Temperature Cu-Cu Bonding in Ambient Air Achieved by Using Cone Bump", Appl. Phys. Express 4 (2011) 016501, DOI:10.1143/APEX.4.016501.

- 10. N. Watanabe, and <u>T. Asano</u>, "Characteristics of a Novel Compliant Bump for 3-D Stacking With High-Density Inter-Chip Connections", IEEE Transaction on Components, Packaging, and Manufacturing Technology 1 (2011) 83, DOI:10.1109/TCPMT.2010.2101450.

- 11. A. Ikeda, K. Kajiwara, N. Watanabe, and T. Asano, "Effect of Argon/Hydrogen Plasma Cleaning on Electroless Ni Deposition on Small-Area Al Pads", Jpn. J. Appl. Phys. 49 (2010) 08JA05, DOI:10.1143/JJAP.49.08JA05.

- 12. S. Adachi, and <u>T. Asano</u>, "Investigation of Enhanced Impact Ionization in Uniaxially Strained Sin-Channel Metal Oxide Semiconductor Field Effect Transistor", Jpn. J. Appl. Phys. 49 (2010) 04DC14, DOI:10.1143/JJAP.49.04DC14.

- 13. N. Watanabe, and <u>T. Asano</u>, "Room-Temperature Bonding Using Mechanical Caulking Effect of Compliant Bumps for Chip-Stack Interconnection", Jpn. J. Appl. Phys. 49 (2010) 04DB02, DOI:10.1143/JJAP.49.04DB02.

- 14. N. Watanabe, I. Tsunoda, T. Takao, <u>K. Tanaka</u>, and <u>T. Asano</u>, "Fabrication of Back-Side Illuminated Complementary Metal Oxide Semiconductor Image Sensor Using Compliant Bump", Jpn. J. Appl. Phys. 49 (2010) 04DB01, DOI:10.1143/JJAP.49.04DB01.

# 〔学会発表〕(計 33件)

- 1. T. Shuto, K. Iwanabe, Li Jing Qiu, and <u>T. Asano</u>, "Room-Temperature High-Density Interconnection using Ultrasonic Bonding of Cone Bump for Heterogeneous Integration", Proceedings of the 63rd Electronic Components and Technology Conference 2013.

- 2. T. Shuto, K. Iwanabe, and T. Asano,

"High-Density Room-Temperature Bonding of LSI Chips on Plastic Film Using Cone Bump", Proceedings of the 9th International Thin-Film Transistor Conference, (2013).

- 3. A. Ikeda, K. Nishi, and T. Asano, "Phosphorus Doping of 4H-SiC by KrF Excimer Laser Irradiation in Phosphoric Solution", Ext. Abstr. International Conference on Solid State Devices and Materials 2012, (2012).

- 4. K. Iwanabea, T. Shutoa, K. Nodab, S. Nakaib, and <u>T. Asano</u>, "Room-Temperature Micro-joining Using Ultrasonic Bonding of Compliant Bump", Proceedings of IEEE International Workshop on Low Temperature Bonding for 3D Integration (2012).

- 5. N. Watanabe, <u>T. Higashimachi</u>, and <u>T. Asano</u>, "Deformation Analysis of Au Cone Bump in 3D LSI Stacking", Dig. Papers International Microprocesses and Nanotechnology Conference 2012, (2012).

- 6. T. Shuto, K. Iwanabe, L. Qiu, and <u>T. Asano</u>, "Room Temperature Microjoining of qVGA Class Area-Bump Array Using Cone Bump", Proceedings of IEEE CPMT Society Japan Chapter 2012, (2012).

- 7. T. Shuto, K. Iwanabe, K. Noda, S. Nakai, and <u>T. Asano</u>, "Ultrasonic Bonding of Cone Bump for Integration of LSIs in Flexible Electronics", Proceedings of International Conference on Flexible and Printed Electronics 2012, (2012).

- 8. T. Shuto, N. Watanabe, A. Ikeda, and <u>T. Asano</u>, "Low-temperature bonding of LSI chips to PEN film using Au cone bump for heterogeneous integration", Proceedings of 3D Systems Integration Conference 2011, (2011).

- 9. A. Ikeda, N. Watanabe, and  $\underline{\text{T. Asano}}$ , "High frequency signal transmission characteristics of cone bump interconnections", Proceedings of 3D Systems Integration Conference 2011, (2011).

- 10. T. Shuto, N. Watanabe, <u>A. Ikeda</u>, and <u>T. Asano</u>, "Room temperature bonding of LSI chips on PEN film using mechanical caulking of Au cone bump", Ext. Abstr. International Conference on Solid State Devices and Materials 2011, (2011).

- 11. T. Shuto, N. Watanabe, A. Ikeda and T. Asano, "Low-Temperature Bonding of LSI Chips to Polymer Substrate using Au Cone Bump for Flexible Electronics", Proceedings of the 61st Electronic Components and Technology Conference 2011, (2011).

- 12. T. Shuto, N. Watanabe, A. Ikeda, <u>T. Higashimachi</u>, and <u>T. Asano</u>, "Direct Bonding of LSI Chips to Flexible Substrate Using Compliant Bump", Dig. Papers International Microprocesses and Nanotechnology Conference 2010, (2010).

- 13. T. Shuto, N. Watanabe, A. Ikeda, T. Higashimachi, and T. Asano, "Direct Connection of LSI Chips to Polyethylene Naphthalate Using Au Cone Bump", Proceedings of the 17th International Display Workshops, (2010).

[図書](計 0 件)

[産業財産権]

- ○出願状況(計 0 件)

- ○取得状況(計 0 件)

〔その他〕

ホームページ等

http://fed.ed.kyushu-u.ac.jp/index.html

- 6. 研究組織

- (1)研究代表者

浅野 種正(ASANO TANEMASA) 九州大学・大学院システム情報科学研究 院・教授

研究者番号:50126306

(2)研究分担者

田中康一郎(TANAKA KOICHIRO) 九州産業大学・情報科学部知能情報科・ 教授

研究者番号: 40253570

(3)連携研究者

東町高雄 (HIGASHMACHI TAKAO) 崇城大学・工学部機械工学科

研究者番号:50461611

池田晃裕 (IKEDA AKIHIRO) 九州大学・大学院システム情報科学研究 院・助教

研究者番号:60315124