# 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成24年6月15日現在

機関番号: 3 2 6 5 7 研究種目:基盤研究(C) 研究期間:2009~2011

課題番号:21560311

研究課題名(和文) 動的再構成可能プロセッサを用いた超高速小型パワエレコントローラの

基礎研究

研究課題名(英文) Fundamental study of ultra small power electronics controller using

dynamic reconfigurable processor

#### 研究代表者

横山 智紀 (YOKOYAMA TOMOKI) 東京電機大学・未来科学部・教授

研究者番号:60307668

## 研究成果の概要(和文):

動的に内部ハードウェア回路を再構成可能な、動的再構成可能プロセッサ(Dynamic Reconfigurable Processor, DRP)を用いて、デバイス内部に複数の構成情報を保持し、それらを高速に切り換えることで、複数の処理要素それぞれにこれらの構成情報を対応させることにより、面積コストと電力コストの双方が削減できるコントローラの基本設計を行った。その結果、従来の FPGA を用いたコントローラに較べて同じ演算回路を少ないチップリソース消費で実装出来ること、回路の動的切り替えにより効率的に演算処理を行えることを確認した。また、UPS の自律分散制御システムのコントローラへの適用を検討し、FPGA によるハードウェアコントローラを用いた実験システムを用いてシステム構成した場合との比較検討を行った。DRPと FPGA と組み合わせることで、柔軟にシステムに対応できるコントロールシステムが実現でき、同時にチップで消費するリソース量の削減により、コントローラの省電力化が期待できる。

### 研究成果の概要(英文):

A new digital control system using Dynamic Reconfigurable Processor (DRP) was proposed for power electronics controllers. Recently, DRP was developed and released to the consumer market. DRP has the dynamic reconfigurable features to change the plural calculation circuit configuration in one clock duration. So the resource cost and the power cost of the processor can be decreased without the trade off of the calculation performance. It was confirmed that DRP has the possibility to become one effective solution for the power electronics applications. Through this research, DRP is applied for the controller of the autonomous decentralized single phase UPS system, the design concept of the system were described and the consideration of the resource consumption were discussed, and it was confirmed that DRP is suitable for future power electronics controllers.

(金額単位:円)

|         | 直接経費        | 間接経費        | 合 計         |

|---------|-------------|-------------|-------------|

| 2009 年度 | 1, 700, 000 | 510,000     | 2, 210, 000 |

| 2010 年度 | 1, 300, 000 | 390, 000    | 1, 690, 000 |

| 2011 年度 | 600,000     | 180, 000    | 780,000     |

| 年度      |             |             |             |

| 年度      |             |             |             |

| 総計      | 3, 600, 000 | 1, 080, 000 | 4, 680, 000 |

研究分野:パワーエレクトロニクス

科研費の分科・細目:電気電子工学・電力工学・電力変換・電気機器

キーワード:プロセッサ、動的再構成、コントローラ

#### 1. 研究開始当初の背景

動的に内部ハードウェア回路を再構成可能 な、動的再構成可能プロセッサ (Dynamic Reconfigurable Processor, DRP) と呼ばれる デバイス群の開発が進んでいる。

これらのデバイスは、デバイス内部に複数の構成情報を保持し、それらを高速に切り換えることができ、複数の処理要素それぞれにこれらの構成情報を対応させることにより、面積コストと電力コストの双方が削減できると期待されている。これにより、演算回路規模が大きくともチップのゲート数を節減し、かつ消費電力を下げながら、FPGAと同様またはそれ以上の処理性能を実現することが期待されている。

#### 2. 研究の目的

本研究では、電力変換器用制御コントローラに、動的再構成可能プロセッサを適用することによって、変換器全体としての、小型化、高効率化、高性能化の実現性を検討し、実システムとしての有効性を示すことを最終目的とする。特に変換器コントローラ自体にフレキシブルな機能を持たせたままでの1チップ化の可能性を示し、将来の電力変換器コン

トローラの有り方を示すことを目的とする。

## 3. 研究の方法

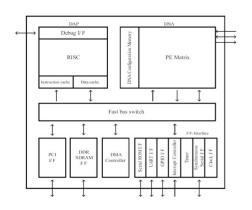

Fig. 1. Circuit configuration of the DAPDNA-EP102

動的再構成可能プロセッサを基にした制御系設計を行う。開発環境を構築し、基本演算のリソース確認およびシステム全体の構成設計を行う。それに基づき、系統連系システムを対象とした制御シミュレーションと動的再構成可能プロセッサに基づくベンチマークシミュレーションを行い、実験時に想定される性能評価を行う。系統連系制御システムを動的再構成可能プロセッサ用の開発環境によるソフトウェア開発を行い、シミュレーションベースでの動作確認を行う。さらに、系統連系制御システムに動的再構成可能プ

ロセッサを用いたコントローラを組み込み、 実験検証を行い、システムの有効性を確認す る。

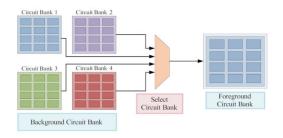

Fig. 2 Configuration of circuit bank

#### 4. 研究成果

本研究で『は、電力変換器用制御コントローラに、動的再構成可能フ『ロセッサを適用することによって、変換器全体としての、小型化、高効率化、高性能化の実現性を検討し、実システムとしての有効性を示すことを目的として、研究を進めた。その結果、変換器コントローラ自体にフレキシフ』ルな機能を持たせたままで『の1チッフ』化の可能性を示し、将来の電力変換器コントローラの有り方を示すことができた。

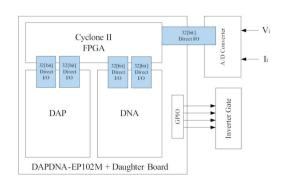

Fig.3 Circuit configuration of DRP based control system

具体的には、動的再構成可能フ』ロセッサを基にした制御系設計を行い、開発環境を構築し、基本演算のリソース確認および』システム全体の構成設計を行った。UPSの自立分

散制御システムを対象とした制御シミュレーションと動的再構成可能フロセッサに基つ C へ ンチマークシミュレーションを行い、実験時に想定される性能評価を行った。系統連系制御システムを動的再構成可能フロセッサ用の開発環境によるソフトウェア開発を行い、シミュレーションへ D ースての動作確認を行った。

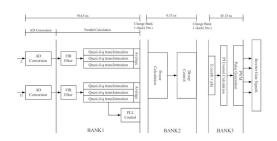

Fig. 4 Timing chart of DRP

それをもとに UPS システムに動的再構成可能プロセッサを用いたコントローラを組み込み、実験検証を行い、システムの有効性を確認しようとしたが、DRP 製造メーカーの生産中止により実システムの製作が困難になったため、従来型の FPGA コントロールシステムとの性能比較、評価を行い、UPS システムを対象とした検証をシミュレーション結果とあわせた検討とした。 これらの成果を元に、論文作成を行い、国際学会での発表を行った。これらの結果、DRP が将来的にパワーエレクトロニクス用コントローラプロセッサとして有望であり、応用が期待できることを示した。

## 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

〔学会発表〕(計 3件)

- ① Comparison of micro controller suitable for power electronics controller with DRP processor, Yushi Fujiyama, <u>Tomoki Yokoyama</u>, IEEJ SPC Japan-Korea Workshop 2011, 2011 年 10 月 22 日,福岡

- ②DRP を用いたパワーエレクトロニクス向 けコントローラの検討,藤田真治,<u>横山智紀</u>, p.l-525, 平成 22 年電気学会産業応用部門大 会、2010 年 8 月 24 日、東京

- ③ A Study of Dynamic Reconfigurable Processor for Power Electronics Application, Shinji Fujita, Shinsuke Oida, Tomoki Yokoyama, The 2010 International Power Electronics Conference, p1252-1257、2010年6月23日、札幌

### 6. 研究組織

(1)研究代表者

横山 智紀 (Tomoki Yokoyama) 東京電機大学・未来科学部・教授 研究者番号: 60307668

- (2)研究分担者 なし

- (3)連携研究者 なし