# 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成24年5月25日現在

機関番号: 13501 研究種目:若手研究(B) 研究期間:2009~2011

課題番号:21760254

研究課題名(和文) インダクタが不要な超小型無線通信システムの実現

研究課題名(英文) Realization of small wireless communication system without an inductor

研究代表者

佐藤 隆英 (SATO TAKAHIDE)

山梨大学・大学院医学工学総合研究部・准教授

研究者番号: 10345390

研究成果の概要(和文):インダクタを用いずに小型な無線通信システムを構築するため、無線通信システムを構成する基本回路ブロックをインダクタを用いることなく実現し、それらの特性の改善を行った。低雑音増幅器および発振回路において、主要な雑音源で発生する雑音を打ち消す構成を応用し、雑音特性の改善を行った。さらにアクティブインダクタ回路のひずみ特性を改善し、アクティブインダクタを用いたフィルタおよび発振回路のひずみ特性を改善した。

研究成果の概要 (英文): In order to build a small wireless communications system, the basic circuit blocks which are used for a wireless communications system were realized without using an inductor, and those characteristics have been improved.

A noise cancellation structure is applied to a low-noise amplifier and an oscillator. Noise characteristics of a low-noise amplifier and an oscillator are improved drastically. The distortion characteristic of an active inductor circuit has been improved. And the distortion characteristics of a filter and an oscillator using the proposed active inductor have been improved.

#### 交付決定額

(金額単位:円)

|        | 直接経費        | 間接経費        | 合 計         |

|--------|-------------|-------------|-------------|

| 2009年度 | 1, 200, 000 | 360, 000    | 1, 560, 000 |

| 2010年度 | 1, 100, 000 | 330, 000    | 1, 430, 000 |

| 2011年度 | 1, 100, 000 | 330, 000    | 1, 430, 000 |

| 総計     | 3, 400, 000 | 1, 020, 000 | 4, 420, 000 |

研究分野:工学

科研費の分科・細目:電気電子工学・電子デバイス・電子機器

キーワード:集積回路、無線通信システム、アクティブインダクタ、低雑音増幅器、発振回路、 発振回路

## 1. 研究開始当初の背景

様々な無線通信システムの集積化が進んでいる。特に携帯通信端末ではWCDMA、無線 LAN、bruetooth など複数の通信規格が同一の端末に搭載されることが一般的となっている。このような背景から無線通信用の集積回路は出来るだけ小型に実現されることが望まれている。通常、無線通信システムは低雑音増

幅器、ミキサ、発振回路、フィルタなどの基本回路ブロックにより構成される。これらの基本回路ブロックにはインダクタが不可欠である。インダクタを集積回路内部で実現する際には、一般にスパイラルインダクタが用いられるが、スパイラルインダクタは MOSFET などその他の素子に比べ非常に大きなチップ面積を必要とする。無線通信システム用の

集積回路においてインダクタの占める面積 は非常に大きいため、インダクタを用いるこ となく無線通信システムを構築することが 出来れば、無線通信システムの劇的な小型化 に非常に有効である。

#### 2. 研究の目的

インダクタを用いることなく無線通信シス テムを構築するため、まず無線通信シスム に用いられる各基本回路ブロックをインダ クタを用いずに実現し、それらの特性の改善 を行う。無線通信システム用の基本回路ブロックをインダクタを用いずに構成した場びで の問題点を明らかにし、その特性を回路場立 工夫により改善する手法を提案する。また、アクティブインダクタと同等な入力インピーダンスタ 実現する回路の特性を改善し、既存のインダクタをアクティブインダクタで置き換えた 基本回路ブロックを開発し、その特性を評価 する。

## 3. 研究の方法

インダクタの代わりに抵抗やMOSFETを用いて無線通信システム用の基本回路ブロックを構成する。インダクタの不使用により劣化する特性を明らかにし、回路構成の工夫により改善を行う。また、受動素子のインダクタと置き換え可能なアクティブインダクタについても検討を行う。既存のアクティブインダクタの特性を改善した提案するアクティブインダクタを用いて基本回路ブロックを構成する。

### 4. 研究成果

(1) インダクタの不使用による無線通信システムに対する影響

#### ① 雑音の増加

理想的なインダクタは雑音を発生しない。このため、インダクタを増幅回路の負荷として用いることで低雑音の増幅回路が実現可能となる。これに対して、抵抗を負荷に用いた増幅回路では抵抗が雑音を生ずるため、増幅回路の利得の増加とともに雑音特性が悪化し低雑音増幅回路には適さない。これは増幅回路に限らずミキサや発振回路等においても同様である。

# ② 歪み特性の悪化

インダクタと等しい入力インピーダンスを有する回路としてアクティブインダクタが知られている。アクティブインダクタはMOSFET 数個と容量により実現される回路であるため、インダクタに比べ非常に小さいチップ面積で実現することが出来る。しかし、MOSFET は非線形素子であるため、アクティブインダクタを通常のインダクタに置き換えて実現した回路は歪特性が劣る。そのため、

アクティブインダクタは高調波歪みの影響 が無視できない応用では問題となる。

# ③ の他の影響

インダクタは、直流の電圧降下を生じないためインダクタを用いた回路はダイナミックレンジが広い。また、インダクタは電力を消費しないため、電力の利用効率に優れる。

#### (2) 雑音特性の改善

インダクタの不使用による雑音の増加の影響を低減する手法として、回路中の主要な雑音源となる MOSFET を 2 個の MOSFET に分割し、出力端子までの経路を伝達関数の符号の異なる 2 経路とすることで MOSFET において発生する雑音を打ち消す構成を用いて低雑音増幅回路および発振回路を構成し、雑音の低減効果を確認した。

## ① 低雜音增幅回路

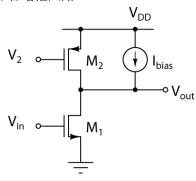

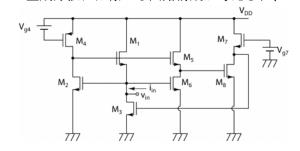

図 1: MOSFET を用いた増幅回路

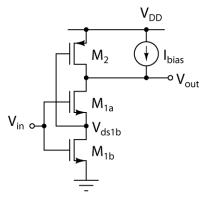

図1に増幅回路を示す。この増幅回路において主要な雑音源は $M_1$ である。 $M_1$ において生ずる雑音を低減するため図2に示すように $M_1$ を $M_{1a}$ と $M_{1b}$ の2個のトランジスタに分割する。 $M_{1b}$ において生ずる雑音は $M_{1a}$ または $M_2$ の異なる経路を経由して出力端子に伝わる。これらの経路の伝達関数は符号が異なるため、 $M_{1b}$ において生ずる雑音は出力端子において打ち消しあい、回路全体の雑音特性が改善される。この回路の原理は既知であったものの、雑音特性を最適とするための設計指針は明らかとなっていなかった。そこで本研究では図2の増幅回路の設計指針を明らかにした。

図 2:M1 による雑音を低減する増幅回路

提案する設計指針を以下に述べる。Miaおよび M<sub>1b</sub>のサイズが一定であるとき、M<sub>2</sub>と M<sub>1a</sub>(およ び M<sub>11</sub>) のドレイン電流が等しくなるように M<sub>2</sub>のチャネル幅およびチャネル長を選ぶこと でバイアス電流源  $I_{bias}$ が不要となるため、入 力換算雑音電力は最小となる。また、この条 件下では入力換算雑音電力および電圧利得 は M<sub>1a</sub>と M<sub>1b</sub>のチャネル長の和(L1) によらず L1 に対する M<sub>1a</sub>のチャネル長の比(分割比) のみに依存する。入力換算雑音電力は分割比 を小さくすることで減少し、電圧利得は分割 比を大きくすることで増加する。このため、 回路を設計する際に、回路の電圧利得が仕様 として与えられる場合、必要な電圧利得を得 られる最小の分割比を選択すれば良い。得ら れた分割比から入力換算雑音電力が求めら れる。逆に、入力換算雑音電力が仕様として 与えられる場合には、仕様を満たす最大の分 割比を選択すればよい。また、実現可能な分 割比の最低値は用いるトランジスタの最小 チャネル長と L1 に依存する。そのため入力 換算雑音を最小にするには L1 を許容される 最大値に選び、分割比を最小にするとよい。

#### ② 発振回路

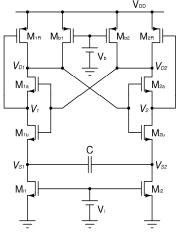

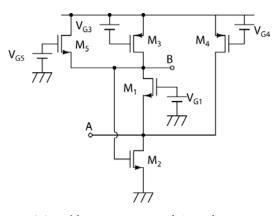

図 3:位相雑音を低減した発振回路

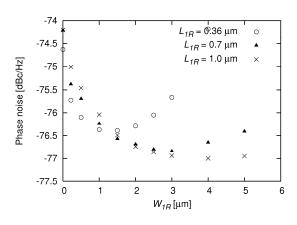

図 4: W<sub>1R</sub>と位相雑音の関係

図2の構成を応用した発振回路を図3に示す。 $M_{1a}$ 、 $M_{1b}$ および $M_{1R}$ が図2と同様の回路を構成している。通常の弛張発振回路では $M_{1a}$ および $M_{1b}$ をスイッチング動作する1個のMOSFETで実現するが、このMOSFETが過渡状態において生ずる雑音が発振回路の位相雑音の原因となる。提案回路では、 $M_{1b}$ の雑音を低減可能となるため、従来回路に比べ位相雑音が改善される。図3の位相雑音のシミュとは $M_{1R}$ のチャネル幅であり、 $W_{1R}$ が零のときが従来回路を示している。図4より提案構成とすることで位相雑音が-3dB程度改善されていることが分かる。

# (3) アクティブインダクタの低歪化 受動素子であるインダクタを直接置き換え て用いることを想定し、アクティブインダク タの歪特性の改善を行った。

① 低ひずみアクティブインダクタ MOSFET は非線形素子であるため、従来のアクティブインダクタは入力インピーダンスが入力振幅に大きく依存し、非線形な特性を有していた。そこで歪みの主要な原因となる MOSFET を特定し、その歪みを打ち消す手法を提案した。回路内部で大きな電圧振幅の信号が加わる MOSFET において生ずる歪みと写しい歪みを回路内部で意図的に発生させ、歪みを回路内部で意図的に発生させ、形と実現している。歪みの打ち消しに用いる信号の生成方法には様々な回路構成が考えられ、

図 5:低歪みアクティブインダクタ1

図 6:低歪みアクティブインダクタ2

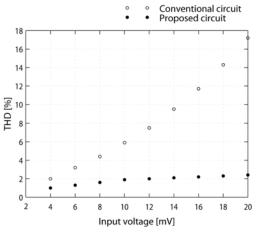

提案手法を実現する複数の新たなアクティブインダクタを導くことに成功した。図5および図6に提案した低歪みアクティブインダクタの例を示す。図7に提案回路と従来回路の歪特性の比較結果を示す。従来回路では入力電圧の増加に伴い急激に歪が増加しているのに対し、提案回路では入力電圧が増加した際にもほぼ一定の歪特性を示していることがわかる。

図7:提案アクティブインダクタの歪特性

# ② アクティブインダクタの応用

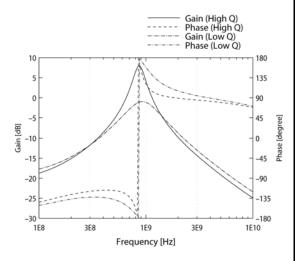

提案する低歪みアクティブインダクタを発振回路およびフィルタへ応用し、特性を評価した。図8に低歪みアクティブインダクタを用いた2次帯域通過フィルタの周波数特性を示す。中心周波数は約1GHzであり、中心周波数およびQは電気的に可変としている。提案する低歪みインダクタを用いることで、とで後来回路使用時に比べフィルタの歪みが約半分に低減されることが確認された。発振回路についても提案回路の使用により高調波歪が低減されることが確認された。

図 8:低歪みアクティブインダクタを用いた フィルタの周波数特性

## 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者には下線)

[雑誌論文](計1件)

① <u>佐藤隆英</u>、高木茂孝、藤井信生、アクティブインダクタの対称構成による低消費電力化、電気学会論文誌 C、査読有、129巻、2010、pp. 1534-1540

〔学会発表〕(計4件)

- ① <u>Takahide Sato</u>, "Active Inductor Design using Distortion Reduction Technique", IEEJ 2011 International Analog VLSI Workshop, 2011 年 11 月 4 日, Indonesia Bali

- ② <u>佐藤隆英</u>, "低ひずみアクティブインダクタを用いた帯域通過フィルタの設計", 平成23年電気学会電子・情報・システム部門大会,2011年9月7日,富山大学(富山市)

- ③ <u>佐藤隆英</u>," MOSFET の分割による熱雑音 低減手法の弛張発振回路への応用",電 気学会 電子回路研究会,2011 年3月2 4日,防衛大学校(横須賀市)

- ④ <u>佐藤隆英</u>," バイアス電流の制御による アクティブインダクタの歪低減",電気 学会電子回路研究会,2011年3月24 日,防衛大学校(横須賀市)

### [その他]

ホームページ等

http://www.ccn.yamanashi.ac.jp/~takahides/contents/reserch2011.html

# 6. 研究組織

(1)研究代表者

佐藤 隆英 (SATO TAKAHIDE)

山梨大学・大学院医学工学総合研究部・准 教授

研究者番号:10345390

(2)研究分担者 なし

(3)連携研究者なし