#### 研究成果報告書 科学研究費助成事業

今和 6 年 6 月 7 日現在

機関番号: 26402

研究種目: 基盤研究(C)(一般)

研究期間: 2021~2023

課題番号: 21K11813

研究課題名(和文)間欠動作する故障検出機構と多重化によるAMSシステムの高信頼化

研究課題名(英文)Fault dectection system and Built-In Self Test schemes for AMS System LSI

#### 研究代表者

橘 昌良(Tachibana, Masayoshi)

高知工科大学・システム工学群・教授

研究者番号:50171715

交付決定額(研究期間全体):(直接経費) 3,300,000円

研究成果の概要(和文):アナログ混載システムLSIで多用される各種回路からアナログ信号処理システムで多用されるひずみの少ないブートストラップスイッチと電位の比較において高速な応答を可能とするダイナミックコンパレータをモチーフとし、回路のインパルス応答に基づいた回路素子の開放/短絡などのカタストロフィック故障を検出できる故障検出システムの開発を行い、回路シミュレーションと実チップによる試作/測定の結果、回路素子の開放/短絡については約88%の検出が出来ることを確認した。 さらに故障検出回路では,電源電圧との差がトランジスタのしきい値電圧よりも小さい電圧の検出を可能とするコンパレータの設計とLSI化 を行った。

研究成果の学術的意義や社会的意義 アナログ回路の故障検出のためのテスト方式の研究は古くから行われているが、これらの研究は特別なテストモ ードと大規模な即手系を使用してテストを行い、故障原因と故障箇所の特定に重点を置いた出荷時のテストを前提としたものが多い。

本研究による故障検出方式では、故障箇所、原因の特定にはこだわらず、システムの動作中に故障検出を行う ことが出来るので、システム動作時のシステムの信頼性向上を図ることが出来る。

研究成果の概要(英文): We propose fault-based BIST(Built-In Self Test) schemes for Analog part of AMS (Analog Mixed-Signal) system LSI. The BIST systems can be used throughout life time of LSIs, from fabrication process to the system's operation. Motif circuits of analog system to design BIST systems are Bootstrapped Switch and Dynamic Comparator. The BIST systems are based on transient response of circuits and fault coverage of Catastrophic faults, such like open/short fault of circuit elements, are about 88% with reasonable area overhead.

We also design Window Comparator for Fault Detect Circuits which detect extreme voltage near ground and power supply.

研究分野:システムLSI設計、LSI設計支援系

キーワード: Built-In Self Test Analog-Mixed Signal カタストロフィック故障 デペンダブルコンピューティング

科研費による研究は、研究者の自覚と責任において実施するものです。そのため、研究の実施や研究成果の公表等に ついては、国の要請等に基づくものではなく、その研究成果に関する見解や責任は、研究者個人に帰属します。

#### 1.研究の背景

アナログ回路は、デジタルシステムと比べて多重化による高信頼化が難しく、集積度の高い AMS(Analog Mixed-Signal)システム LSI の高信頼化の問題点の一つとなっている。

しかし、現実のシステムではすべての回路が常時動作する必要があるような構成をとることはあまりなく、特定の回路が動作しない時間が発生する。このような空き時間を利用して間欠的にテストを行い、異常が発生した回路とあらかじめ用意されている正常な回路との切り替えを行うことができれば、システム全体の信頼性を向上させることができる。また、回路に異常が発生した場合にシステムの使用を停止することができるだけでも有用である。

### 2.研究の目的

AMS システム LSI の高信頼化を目的としたアナログ回路の故障検出をシステムの動作中にも行える機構の開発を目的とする。

この機構はLSIシステムがデジタル/アナログ両方の回路を組み合わせて使える利点を利用して、アナログ回路にテスト信号発生回路、動作状態を監視するプローブ回路とその出力から動作異常を検出する故障検出回路を組み合わせ、それらをデジタル回路により制御することにより、システムは動作中であるが検査対象となるアナログ回路の動作を必要としない時間帯を利用して、間欠的にテストを進めることの出来るものである。

このような、システムの動作状態での動作異常の検出を行うことのできる BIST システムを提案し、LSIを試作しその有効性を実証することを目標としている。

### 3.研究の方法

AMS システム LSI で一般的に用いられる各種形式のアナログ回路とその故障検出を行う回路のシミュレーションと実チップによる有効性の検証をおこなった。対象としたのはアナログ信号処理システムで良く使用されるアナログスイッチ、特に、ひずみの少ない信号伝送が行えるブートストラップスイッチと電位の比較に用いられるコンパレータのうち高速な応答を要求されるところで使用されるダイナミックコンパレータである。また、故障検出回路では、電源電圧、接地電圧との差がトランジスタのしきい値電圧よりも小さい電圧の検出も要求されるため入力電圧をシフトして検出するコンパレータの設計とLSI化を行った。

回路設計とシミュレーションおよび LSI チップの試作は VDEC (VLSI Design and Education Center)を利用して各種の EDA ツールと Rohm 0.18 μm CMOS プロセスを使用して行った。対象としたのは、カタストロフィック故障でありトランジスタの各端子の開放 / 短絡故障と抵抗、キャパシタンスの開放 / 短絡故障である。回路のインパルス応答に基づいた回路素子の開放/短絡などの致命的故障(カタストロフィック故障)を検出できる故障検出システムの開発を行い、回路シミュレーションと実チップによる試作/測定の結果、回路素子の開放/短絡については約88%の検出が出来ることを確認した。

## 4. 研究成果

# (1) ブートストラップド・スイッチにおける素子の開放/短絡故障検出

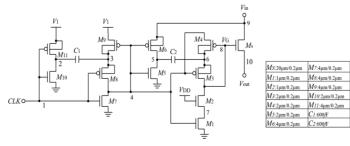

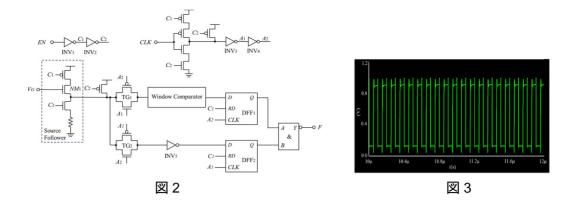

ブートストラップド・スイッチは、スイッチとなるトランジスタのゲートソース間電圧を常に電源電圧とすることで、スイッチの非直線歪みを低下させたスイッチである。この回路では内部の電圧が電源電圧の2倍まで高くなることがあるため、テストの際に駆動回路ので電源電圧を通常の1/2にすることで、テスト時に耐圧を超えた電圧を検出する必要が無い故障検出回路を作成することが出来た。図1にブートストラップド・スイッチ、図2に故障検出回路、図3に図1においてトランジスタM1にゲート開放の故障を組み込んだ場合のゲート電圧の実測値を示す。シミュレーションと実測により66個の故障のうち87.9%が検出可能であることを確認した。

図 1

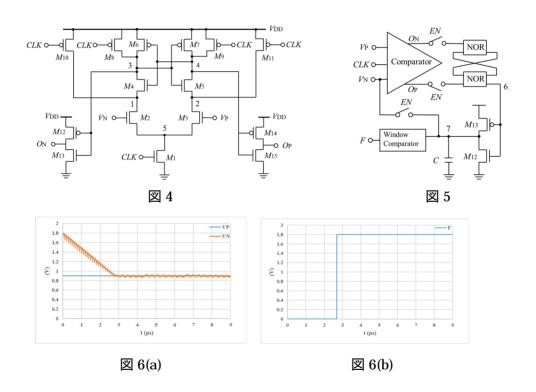

## (2)ダイナミック・コンパレータにおける素子の開放 / 短絡故障検出

ダイナミック・コンパレータ (図 4) は応答速度に影響を与えない様に内部ノードの電圧を測定することが難しいため、図 5 に示すような帰還ループを作り、VN の電圧の推移を観測することで故障検出を行っている。故障検出モードでは VP の値は電源電圧の半分である 0.9V に固定し、図 5 の出力端子 F の値を監視することで故障を検出する。回路に故障が存在しない場合、シミュレーションによると VN の値は図 6(a)の様に推移し、出力端子 F の値は図 6(b)の様になる。回路に故障がある場合には F の電圧の変化により検出が可能である。シミュレーションと実測により 6 6 個の故障のうち 87.8%が検出可能であることを確認した。

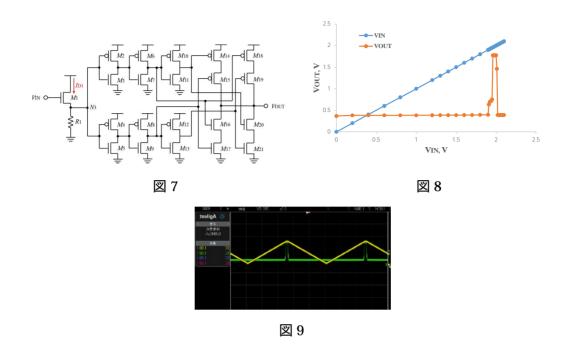

## (3) ウィンドウ・コンパレータ

故障検出回路では電源電圧、接地電圧にきわめて近い電圧の検出を行いことがあるが、一般にトランジスタのしきい値電圧よりも電源電圧、接地電圧に近い電圧の検出を簡素な回路で行うのは難しい。そこで、ソースフォロアによる電圧シフト回路を使用した回路の設計と試作を行った。図7に電源電圧に近い電圧の検出を行うための回路を示す。図8は実測結果であり、しきい値電圧0.3Vよりも電源電圧に近い電圧で反応していることがわかる。図9はこの回路に存在するヒステリシスを繰り返し波形により測定した結果である。

なお、図 7 の回路は電源電圧に近い電圧の検出を行うもであるが、同様な構成でトランジスタの極性を替えれば接地電圧に近い電圧の検出も可能である。

(4)以上の2種のBIST手法は、および、ウィンドウ・コンパレータを使用すれば、検出できる故障はかぎられるが、LSIの製造段階からシステムに実装した後までどの段階でも動作させること出来る。このため、検査対象となるアナログ回路を複数システムに実装しておき、故障が発見された場合は回路を切り替えることでシステムの高信頼化をはかることが出来る。

#### 5 . 主な発表論文等

「雑誌論文 〕 計2件(うち査読付論文 2件/うち国際共著 0件/うちオープンアクセス 2件)

オープンアクセスとしている(また、その予定である)

| 「推協調文」 首2件(フラ直説的調文 2件/フラ国際共省 0件/フラオーフファフピス 2件) |           |

|------------------------------------------------|-----------|

| 1.著者名                                          | 4 . 巻     |

| Masayoshi Tachibana ; Tang Xiaobin             | -         |

|                                                |           |

| 2.論文標題                                         | 5.発行年     |

| BIST Scheme for Dynamic Comparators            | 2022年     |

|                                                | 6.最初と最後の頁 |

| ら、株理砂石<br>electronics                          | 0.取別と取扱の貝 |

| erectronics                                    | -         |

|                                                |           |

| 掲載論文のDOI(デジタルオブジェクト識別子)                        | 査読の有無     |

| 10.3390/electronics11244169                    | 有         |

|                                                |           |

| オープンアクセス                                       | 国際共著      |

| オープンアクセスとしている(また、その予定である)                      | -         |

|                                                |           |

| 1. 著者名                                         | 4 . 巻     |

| Masayoshi Tachibana ; Tang Xiaobin             | 10        |

| 2 *A+++#-PX                                    | F 38/-/T  |

| 2.論文標題                                         | 5.発行年     |

| A BIST Scheme for Bootstrapped Switches        | 2021年     |

| 3.雑誌名                                          | 6.最初と最後の頁 |

| electronics                                    | -         |

| - Constrained                                  |           |

|                                                |           |

| 掲載論文のDOI(デジタルオプジェクト識別子)                        | 査読の有無     |

| 1 40 0000 ( ) 1 40 ( ) 00 (                    |           |

有

国際共著

## 〔学会発表〕 計6件(うち招待講演 0件/うち国際学会 0件)

1.発表者名

オープンアクセス

小池 智哉 、橘 昌良

10.3390/electronics10141661

2 . 発表標題

高次 変調回路に向けたNauta OTAの設計

3 . 学会等名

令和4年度 電気・電子・情報関係学会四国支部連合大会

4 . 発表年

2022年

- 1.発表者名

- 林 竜史、橘 昌良

- 2 . 発表標題

バンドギャップ基準電源回路における素子バラツキを抑制する回路の設計

3 . 学会等名

令和4年度 電気・電子・情報関係学会四国支部連合大会

4.発表年

2022年

| 1.発表者名<br>小池 智哉 、橘 昌良                    |

|------------------------------------------|

|                                          |

| 2 . 発表標題<br>高次 変調回路に向けたNauta OTAの設計      |

| 2 24 4 77 77                             |

| 3 . 学会等名<br>令和3年度電気· 電子· 情報関係学会四国支部連合大会  |

| 4.発表年                                    |

| 2021年                                    |

|                                          |

| 1.発表者名<br>青木 聡太、橘 昌良                     |

| 2. 発表標題                                  |

| パンドギャップ基準電源回路を対象としたBIST手法に関する研究          |

| 2                                        |

| 3 . 学会等名<br>令和3年度電気·電子·情報関係学会四国支部連合大会    |

| 4.発表年<br>2021年                           |

|                                          |

| 1.発表者名<br>林 竜史、橘 昌良                      |

| 2. 文字 中華 日本                              |

| 2.発表標題<br>パンドギャップ基準電源回路の素子パラツキを抑制する回路の検討 |

| 3.学会等名                                   |

| 令和3年度電気·電子·情報関係学会四国支部連合大会                |

| 4 . 発表年<br>2021年                         |

| 1.発表者名                                   |

| 5. 完成有名<br>乾 沙羅、橘 昌良                     |

| 2 . 発表標題                                 |

| CMOSアナログ回路設計のためのパラメータ計算システム              |

| 3 . 学会等名<br>令和3年度電気·電子·情報関係学会四国支部連合大会    |

| 4 . 発表年<br>2021年                         |

|                                          |

|                                          |

〔図書〕 計0件

〔産業財産権〕

〔その他〕

-

6.研究組織

| · K// 5 0/104/194         |                       |    |

|---------------------------|-----------------------|----|

| 氏名<br>(ローマ字氏名)<br>(研究者番号) | 所属研究機関・部局・職<br>(機関番号) | 備考 |

7.科研費を使用して開催した国際研究集会

〔国際研究集会〕 計0件

8. 本研究に関連して実施した国際共同研究の実施状況

| 共同研究相手国 | 相手方研究機関 |

|---------|---------|

|---------|---------|