# 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成 25 年 6 月 11 日現在

機関番号:17104 研究種目:基盤研究(B)

研究期間:2010 ~ 2012

課題番号:22360118

研究課題名(和文) 新原理に基づく革新的シリコン省エネダイオード

研究課題名(英文) Innovative Low Loss Semiconductor Rectifier with Pulsed Carrier

**Injection Mechanism**

研究代表者

大村 一郎(OMURA ICHIRO)

九州工業大学・工学研究院・教授 研究者番号:10510670

### 研究成果の概要(和文):

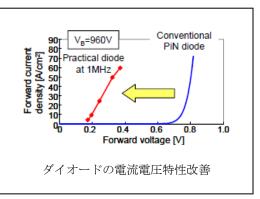

整流ブリッジなどで莫大な数用いられている電力用ダイオードに着目し、シリコン技術で、従来にくらべ50%程度の損失削減の原理確認と基本設計を完了。従来ダイオードでは定常的にキャリアが再結合しているのに対し、本研究では、再結合の量を極力減らし、必要最小限の電子及びホールをパルス的に注入することによって、実質的に0.4 V以下で導通を可能なダイオードを実現した。さらに波及技術としてSWデバイス(IGBT)の高性能化設計も見出した。

## 研究成果の概要 (英文):

The possibility of silicon power device loss reduction by 50% is demonstrated in theory and experiment. In the research, PiN diodes, which have been used in variety of applications, are particularly considered for loss reduction with new carrier injection method. The new method with pulsed injection shows reduction of forward voltage drop down to 0.4V which is about a half of the conventional PiN diodes. In the research IGBT loss reduction method is also demonstrated.

### 交付決定額

(金額単位:円)

|         | 直接経費         | 間接経費        | 合 計          |

|---------|--------------|-------------|--------------|

| 2010 年度 | 6, 400, 000  | 1, 920, 000 | 8, 320, 000  |

| 2011 年度 | 5, 700, 000  | 1, 710, 000 | 7, 410, 000  |

| 2012 年度 | 2, 300, 000  | 690, 000    | 2, 990, 000  |

| 年度      | 0            | 0           | 0            |

| 年度      | 0            | 0           | 0            |

| 総計      | 14, 400, 000 | 4, 320, 000 | 18, 720, 000 |

#### 研究分野:

科研費の分科・細目:電気電子工学・電力工学・電力変換・電気機器 キーワード:パワーエレクトロニクス、パワー半導体、電力用ダイオード

# 1. 研究開始当初の背景

文部科学省低炭素社会づくり研究開発戦略(平成21年8月11日文部科学大臣決定)によるとCO2排出量の「2050年までに、現状から60~80%の削減」は単独技術による効果では達成不可能であり、複数の組み合わせと、技術の普及に寄るMASSの効果が不可欠であるとされている。すなわち、デバイス

や機器での CO2 削減量とそれらデバイス等の導入量の掛け算を積み上げた形での CO2 の削減方針になっている。この開発戦略の「戦略 3」では、2030 年頃の CO2 排出量を大幅に削減しうる先進的技術の開発(緩和策)の必要性が明言され、2020 年頃の量産化とその後の10年の普及期間に CO2削減に大きく寄与する技術の早期立ち上げを、効率

性と経済性を高めつつ行うとされている。すなわち、技術的な実現見通しのほかに、量産性や導入コスト、経済性、資源的制約の回避が戦略の中で明言されている。

2050年の社会では、民政・産業・運輸の最終エネルギーの半分が電力で供給される可能性が高い中で(現状では20%の最終エネルギーが電力で供給)、本研究では電力利用の高効率化に寄与するパワーエレクトロニクスのキーコンポー年度としてのパワー半導体に注目し、特にありとあらゆるパワエレ回路にもっとも膨大な数が使われている電力用ダイオードに注目した。

### 2. 研究の目的

文科省低炭素社会づくり研究開発戦 略によれば2020年までに製品化が可能 で、2030年にCO2削減効果の得られる先 進的低炭素化技術の早期立ち上げ、特に 電力利用での超低損失化が重要事項の 例にあげられている。電力損失のCO2排 出への効果は「損失低減効果×普及量」 で与えられ、技術的な効果と普及の両者 を見据えたスウィートスポットに狙い を定めた研究が重要となる。本研究では 昨今の電気電子機器に整流ブリッジな どで莫大な数用いられている電力用ダ イオードに着目し、10年後の2020年時 点で大量生産可能なインフラを持つシ リコン技術で、従来に比べ50%程度の損 失削減の原理確認と基本設計の完了を 目的とする。従来PiNダイオードの電流 導通では定常的に電子及びホールが素 子内に注入され続け、素子内部でそれぞ れのキャリアが再結合しているメカニ ズムであったが、本研究で再結合の量を 極力減らし、必要最小限の電子及びホー ルを10MHzから1GHzの高周波でパル ス的に注入する構造と回路を付加する ことによって、実質的に0.4V以下で導通 を可能なダイオードを実現することを 目的とする。

### 3. 研究の方法

まったく新しい原理による高注入導電デバイスのため、その原理と設計概念を確立する。 ①従来のPiNダイオード、SiC-SBDの損失を評価し、今回の研究ターゲットを確認。

②今回提案する、10MHzから1GHzでの高周波パルス・キャリア注入するという新しいメカニズムでの損失低減の原理確認を、半導体基本方程式を用いた大規模な数値解析で行った。

③最適制御アルゴリズム構築のため、キャリア挙動メカニズムを解明し数学モデルを構築。

④本提案ダイオードの構造及びシステム上の

制御の実用化検討を行う。とくに高周波でパルス的に注入する構造及び回路を3次元の数値解析で行った。

⑤一層の低損失化に向けた、シリコン結晶や プロセスへの要求スペックを検討、試作研究 に向けた準備を行った。(試作クリーンルー ムの選定、プロセスの検討)

### 4. 研究成果

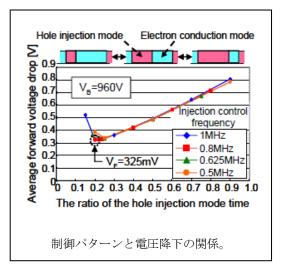

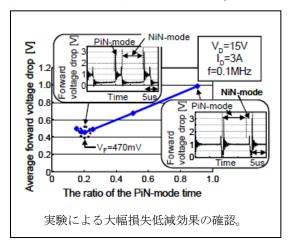

(1)従来PiNダイオードの電流導通では定常的に電子及びホールが素子内に注入され続け、素子内部でそれぞれのキャリアが再結合しているメカニズムであったのに対し、キャリア再結合の量を極力減らし、必要最小限の電子及びホールをパルス的に注入する構造と回路を付加することによって、実質的に0.4V以下で導通を可能であることを見出した。

(2)数学的モデルと最適制御アルゴリズムの構築と検討として、数値解析結果のデータを基にパルス的なキャリア注入の制御アルゴリズム構築に必要な最適パルス周波数とパルス幅を見出した。またアルゴリズム研究として、実験的に評価用の専用回路を構築し、評価を行った。回路上のインダクタ

ンスを極力減らすことで、駆動制御も含め 本コンセプトを実験的に実証できた。

(3)具体的構造の検討(当該年度に特許出願済み)として、シリコンパワー素子で一般的なトレンチゲート構造を用いることで、素子内に注入制御構造をインテグレーションし、シミュレーションで実証。構造は特許出願。基本構造は現状のトレンチ IGBT (Insulated Gate Bipolar Transistor) の構造を一部変更したものであり、IGBT の微細化研究とも関連付けて研究を行った。

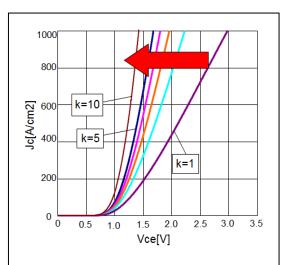

(4)パワー半導体での新しいスケール則に基づく設計を提案し、新しい設計方法に基づく微細化により同一チップ面積、同一電圧降下の条件で約5倍の電流を流す能力が得られることが分かった。(H24年度に国内特許出願済み、H25年度、優先権を利用し外国特許出願決定。)

新しい微細化スケール側によるIGBTの損失低減効果の発見。

(5)ゲートの駆動エネルギーは微細化係数の2乗に反比例することが分かり、例えば現状の10倍の微細化で、同一チップ面積で駆動エネルギーは100分の1に減少し、新たなゲート駆動方法が可能になることが分かった。この結果ゲート駆動回路のチップ上への集積化や、チップオンチップの実装による集積化が容易になった。

(6)微細化により製造工程の短縮と大口径ウエハの利用が可能となることで、量産性が大幅に向上した。

上記内容は、日経エレクトロニクス (2013/2/18) に 2 ページ記事として掲載。また半導体産業新聞 (2012/8/8) に微細化のメリットに関し掲載。

## 5. 主な発表論文等

〔雜誌論文〕(計3件)

①Hiromichi Ohashi, <u>Ichiro Omura</u>, "Role of Simulation Technology for the Progress in Power Devices and Their Applications", IEEE TRANSACTION ON ELECTRON DEVICES,

查読有, Vol.60, No.2,pp.528-536, 2013 http://dx.doi.org/10.1109/TED.2012.22 28272

②Masahiro Tanaka, <u>Ichiro Omura</u>, "IGBT Scaling Principle Toward CMOS Compatible Wafer Processes", Solid-State Electronics, 查読有, vol.80, pp.118-123, 2012

http://dx.doi.org/10.1016/j.sse.2012.10.020

③ Masahiro Tanaka, <u>Ichiro Omura</u>, "Structure Oriented Compact Model for Advanced Trench IGBTs without Fitting Parameters for Extreme Condition: part I", Microelectronics Reliability, 查読有, vol.51, PP.1933-1937, 2011

http://dx.doi.org/10.1016/j.microrel.20 11.07.050

〔学会発表〕(計8件)

- ①「高耐圧パワーデバイス用スケールダウン・テストヘッドの開発」、松吉峻、附田正則 (ICSEAD)、平井秀敏、<u>大村一郎</u>、電子情報 通信 学会、IEICE Technical Report EE2012-46,CPM2012-168, pp.105-109, 2013 年 1 月 24 日、熊本

- ② "Semiconductor Power Switches: Principles and the Future", <u>Ichiro</u> <u>Omura</u>, The 24th International

Symposium on Power Semiconductor Devices & IC's Short Course (ISPSD'12) (invited), June 3-7, Bruges, Belgium, 2012

- ③"Scaling Rule for Very Shallow Trench IGBT toward CMOS Process Compatibility", Masahiro Tanaka and Ichiro Omura, Proc. of ISPSD, 查読有, pp.177-180, June 3-7, Bruges, Belgium, 2012

- ④ "Universal Trench Edge Termination Design", Kota Seto, Ryu Kamibaba, Masanori Tsukuda and <u>Ichiro Omura</u>, Proc. of ISPSD, 查読有, pp. 161-164, June 3-7, Bruges, Belgium, 2012

- ⑤ "Scattering Parameter Approach to Power MOSFET Design for EMI", Masanori Tsukuda, Keiichiro Kawakami and <u>Ichiro Omura</u>, Proc. of ISPSD, 查読有, pp. 181-184, June 3-7, Bruges, Belgium, 2012

- ©"Lateral Power Devices: from LDMOS, LIGBT to GaN", <u>Ichiro Omura</u>, 2012 International Symposium on VLSI Technology, Systems and Applications VLSI Design, Automation and Test(invited), April 23-25, Hsinchu, Taiwan, 2012

- ⑦ Motohiro Tsuda, Yasuaki Matsumoto, <u>Ichiro Omura</u>, "Ultra Low Loss Trench Gate PCI-PiN Diode with V<sub>F</sub><350mV", The 23rd International Symposium on Power Semiconductor Devices & IC's (ISPSD'11), 查読有, May 23-26, San Diego, USA, 2011

- ®Yasuaki Matumoto, Kenichi Takahama, Ichiro Omura, "Challenge to the Barrier of Conduction Loss in PiN Diode toward VF<300 mV with Pulsed Carrier Injection Concept", The 22<sup>nd</sup> International Symposium on Power Semiconductor Devices and ICs (ISPSD'10), 查読有, June 6-10, Hiroshima, Japan, 2010

〔産業財産権〕 ○出願状況(計6件)

名称:高電圧絶縁ゲート型電力用半導体装置

およびその製造方法

発明者:大村一郎、田中雅浩、附田正則、

三木大和

権利者:九州工業大学

種類:特許

番号:特願 2012-195347

出願年月日:2012年9月5日

国内外の別:国内

名称:高電圧電力用半導体装置

発明者:大村一郎、瀬戸康太、附田正則

権利者:九州工業大学

種類:特許

番号:特願 2012-123461 出願年月日:2012年5月30日

国内外の別:国内

名称:高電圧絶縁ゲート型電力用半導体装置 発明者:大村一郎、田中雅浩、三木大和

権利者: 九州工業大学

種類:特許

番号:特願 2012-123462 出願年月日:2012年5月30日

国内外の別:国内

名称:半導体装置及び駆動方法

発明者:大村一郎、松本泰明、津田基裕、

附田正則

権利者:九州工業大学

種類:特許

番号: 101117564

出願年月日:2012年5月17日

国内外の別:国外(台湾)

名称:半導体装置及び駆動方法

発明者:大村一郎、松本泰明、津田基裕、

附田正則

権利者:九州工業大学

種類:特許

番号: PCT/JP2012/062300 出願年月日: 2012年5月14日

国内外の別:国外

名称:半導体装置及び駆動方法

発明者:大村一郎、松本泰明、津田基裕、

附田正則

権利者:九州工業大学

種類:特許

番号:特開 2012-243918 出願年月日:2011年5月18日

国内外の別:国内

[その他]

(1) 日経エレクトロニクス 2013.2.18, pp.16-17

(2)半導体産業新聞(平成 24 年 8 月 8 日)研究開発・新技術インタビュー

6. 研究組織

(1)研究代表者

大村 一郎 (OMURA ICHIRO) 九州工業大学・工学研究院・教授

研究者番号: 10510670