## 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成25年6月7日現在

機関番号: 1 4 4 0 1 研究種目:基盤研究(C) 研究期間:2010~2012 課題番号:22560330 研究課題名(和文)

ナノスケールデバイスの過渡的電気・熱連成シミュレーション技術の開発とその応用 研究課題名(英文)

Development of Simulator for Transient Electrothermal Properties of Nanoscale Devices 研究代表者

鎌倉 良成 (KAMAKURA YOSHINARI) 大阪大学・大学院工学研究科・准教授

研究者番号:70294022

研究成果の概要(和文):ナノスケールトランジスタを対象に、内部の電子と熱の輸送を統一的に解くシミュレーション技術を新たに開発した。フォノン輸送やゼーベック効果など、モンテカルロ法を用いた熱電輸送解析に必要な新規アルゴリズムを提案し、またそれら要素技術を統合することにより電子とフォノンの輸送問題を同時に解くシミュレータを開発することができた。さらに得られた知見を等価回路モデルで表現し、回路レベルでの熱電解析を可能とした。

研究成果の概要(英文): Using a coupled Monte Carlo technique for solving both electron and phonon Boltzmann transport equations, the transient electrothermal simulator for nanoscale Si devices was developed. To this end, novel algorithms for simulating phonon transport and Seebeck effects were proposed. It has been also suggested that the simulated observations on the hot spot generation and dissipation can be practically described by the equivalent thermal circuit model.

## 交付決定額

(金額単位:円)

|         |             |             | (亚铁十)。 (1)  |

|---------|-------------|-------------|-------------|

|         | 直接経費        | 間接経費        | 合 計         |

| 2010 年度 | 1, 500, 000 | 450,000     | 1, 950, 000 |

| 2011 年度 | 1, 100, 000 | 330,000     | 1, 430, 000 |

| 2012 年度 | 800,000     | 240, 000    | 1, 040, 000 |

| 年度      |             |             |             |

| 年度      |             |             |             |

| 総計      | 3, 400, 000 | 1, 020, 000 | 4, 420, 000 |

研究分野: 半導体工学

科研費の分科・細目:電気電子工学 電子デバイス・電子機器

キーワード:トランジスタ、熱伝導、シミュレーション、MOSFET、シリコン、モンテカルロ 法

## 1. 研究開始当初の背景

CMOS を用いた半導体集積回路技術が電力密度の壁に遭遇し、極微細回路における熱排出問題の正しい理解と制御法の確立が重要となっている。特にナノスケール MOSFETでは、ソースから注入された電子は、チャネル内部でほとんどエネルギーを失わず(準弾

道的伝導)、ドレインに到達してから一気に光学フォノンを放出することが知られており、このときの典型的発熱密度は 10 TW/cm³以上と見積もられる。光学フォノンは群速度が遅く、熱が周囲に拡散するためにはフォノン-フォノン散乱を通じた音響フォノンへの変換を待たなければならない。もしこの過程が

ボトルネックとなった場合には、非平衡フォノンの溜まり場、いわゆるホットスポッケール形成へとつながる。このようなナノスケール固有の物理現象に対し、ミクロな視点、理解したが行われ、理解が行われ、理解が行われ、理解がでの影響につかるが、回路動作への影響についない。まだあまり良く分かっている。単体トランジスタの発熱がチップをは広がる過程など、時間・空間的に広いを囲でのマルチスケール・シミュレーション体系の確立が急務となっている。

## 2. 研究の目的

チャネル長 10 nm級のナノスケール MOSFET を対象とし、その内部におけるエネルギー散逸過程を物理的に正しく理解した上で、そこから得られた知見を踏まえ集積回路の動作に発熱が与える影響を明らかにする。さらに、発熱の制御と抑制方法に関する理論的検討を行う。これら解析を遂行するため、すでに開発した熱・電気連成シミュレータを発展させ、広範囲の時間・空間領域をカバーし得るマルチスケール解析システムを新たに構築する。

#### 3. 研究の方法

半導体デバイス中の電子と熱の連成輸送問題を、ボルツマン輸送方程式に基づいて数値解析した。用いた手法はモンテカルロ法であり、ナノスケールで顕在化する電子やフォノンの準弾道輸送効果にも対応可能である。特にフォノンのモンテカルロ(MC)シミュレーションについては、アルゴリズムやモデルが未だあまり整備されていないこともあり、詳細な検討を行った。

## 4. 研究成果

(1) フォノン輸送シミュレータの開発 ①シミュレーション方法

現実的なナノスケールデバイスの熱特性にフォノンの準弾道輸送特性が与える影響をMCシミュレーションによって調べた。この手法は、フォノンのボルツマン輸送方程式を粒子モデルに基づき直接解くものであり、と式を雑な微細素子構造に対して有効な方法といえる。計算時間が必要なこともあり、これ構での適用事例は1次元等の単純なテスト構造に限られてきた。本研究では、現実的なデバイス構造に対してこの手法を適用し、フーリエ則ベースの熱解析手法の妥当性あるいは限界を調べるため、新たなシミュレータの開発を行った。

MC シミュレーションでは、音響フォノンを 粒子(エネルギーのかたまり) として表現し、

多数の MC 粒子のブラウン運動を追跡するこ とで、その統計から、半導体内部の熱輸送特 性を予測する。室温ではフォノン分布が高エ ネルギー領域にまで広がるため、フォノン状 熊密度(DOS) や群速度の高精度なモデル化 が必要となる。そこで本研究では、Si の現実 的なフォノン分散から、DOS と群速度(等エ ネルギー面上で平均)のエネルギー依存性を 求め、それらをテーブルとしてシミュレータ に組み込んだ。バルク Si 中の散乱過程として は、フォノン-フォノン散乱およびフォノン-欠陥散乱を考慮した。フォノン-フォノン散乱 ではウムクラップ過程を非弾性1体散乱で 模擬し、エネルギー分布が熱平衡に向かって 緩和するよう散乱後の状態選択を行った。そ れぞれの散乱過程のパラメータは、バルク Si の熱伝導率の実験値を再現するよう調整し た。さらにデバイス応用を見据えてフォノン 境界散乱を取り入れ、薄膜 Si に見られる熱 伝導率低下の再現を試みた。ランバート則に 基づき Si/SiO<sub>2</sub> 界面における 100%の拡散的フ ォノン反射を仮定したところ、薄膜 Si での熱 伝導率の実験値を良好にシミュレートする ことができた。

## ②シミュレータの応用

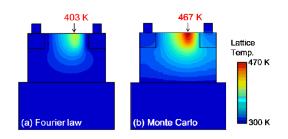

開発したフォノン輸送シミュレータを用いて、FinFET 内部の発熱分布を解析した。今回はバルク Fin を仮定し、ドレイン近傍に  $Q=42~\mu W$  の発熱領域(密度:  $5.3~TW/cm^3$ ) を設置することでホットスポットを模擬した。また、境界条件として、ソース/ドレインコンタクト並びに基板部にヒートシンク(300~K~の熱浴)を置いた。図 1 に定常状態温度分布の計算結果を示す。

図 1: FinFET 中の温度分布のシミュレーション結果。(a) フーリエ則を仮定した熱伝導方程式の数値解。(b)MC シミュレーションの結果。

比較のため、MC 法による結果と共に、従来用いられてきたフーリエ則に基づく熱伝導方程式の解を示した。同じ Q を入力しても、MC 法の方が高い温度上昇を予測する。この要因を分析したところ、主にドレインパッド部の熱抵抗成分の違いによるものであることが判明した。フィン端からコンタクト熱浴

までの距離はフォノンの平均自由行程に比べて十分短く、この部位ではフォノン準弾道輸送効果が顕著となるため、フーリエ則では等価的な熱抵抗が過小に評価される。一方、Fin 内部の熱伝導については、界面による激しい散乱の影響で熱伝導は拡散的であり、両シミュレーション手法で有意な差がないことも今回明らかになった。

## (2) 電子輸送シミュレータによる熱電効果の 解析

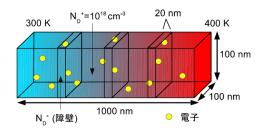

半導体中の熱電効果を MC 法で解析する方法について基礎検討を行った。本研究では例題として、実験値の報告例が多い Si の Seebeck 係数 S を取り上げ、構造中に導入したエネルギー障壁構造が S に与える影響を調べた。図 2 に仮定したシミュレーション系の模式図を示す。

図 2: Seebeck 効果を解析した素子構造

自由電子を粒子、イオン化ドナーは連続な正 の背景電荷として導入した。素子内部には、 周囲のドナー密度 $(N_D^+=10^{18}~{

m cm}^{-3})$  と比べド ーピング濃度の低い $(N_D)$ 幅 20 nm の層を挿入 し、拡散電位  $V_{hi}$  を利用することで周期的な エネルギー障壁構造を導入した。Si 中の電子 輸送(運動と散乱) には、Jacoboni らによる標 準的な MC シミュレーション用モデルを用い、 内部電界分布は 1 次元 Poisson 方程式により 計算した。このように、電子挙動解析と Poisson ソルバが情報をやり取りすることで、 自己無撞着に電子密度分布と電位分布を解 くことができる。系の両端を電気的に開放し、 温度勾配を与えると、素子両端に電気化学ポ テンシャル差が生ずる。エネルギーバンド図 で言えば、Poisson 方程式で求めた電位(電気 ポテンシャル) 分布は伝導帯の底  $E_c(x)$  に相 当する。さらに、化学ポテンシャル $E_C - E_F$ (こ こで $E_F(x)$ はFermi 準位) は、電子の平均エネ ルギーと密度から算定できる。このときデバ イス両端に現れる E<sub>F</sub> の差を温度差で割るこ とでSを計算した。

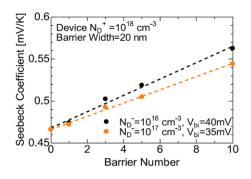

$N_D$ と障壁数を変化させ、Sにどのような影響が現れるかを調べた結果が図3である。障壁数を増やすにつれて、Sが線形に上昇する様子が確認できた。また、 $N_D$ 、すなわち障壁の

高さにもSが依存することが分かった。障壁構造を導入することによって、エネルギーが低い電子は素子全体の電荷輸送からカットオフされる。また、障壁の両側では電子温をが異なることから、一定のエネルギーを超える電子の数nと平均速度(v)に差が生ずる。今回のシミュレーション条件では系は開放を加ているので、正味電流がゼロとなる条件を上げ、障壁の左右からの電流  $\sim n(v)$ をバランスさせる必要がある。このような効果が作用することで、障壁層導入がSの変化につながったものと考えられる。

図 3: Seebeck 係数の障壁数/高さ依存性

# (3) 過渡的電気・熱連成シミュレーション技術の開発

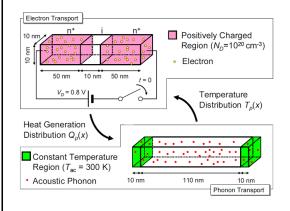

本研究では、Si-MOSFET チャネル部を模した 1 次元 *n-i-n* 構造中の電子とフォノンを粒子でモデル化し、それらの分布の時間発展を MC 法で追跡した(図 4)。電子伝導の解析部においては、電子とフォノンの衝突回数をカウントすることで発熱分布を求め、それに従ってフォノンを生成する。さらにフォノン拡散の結果、変化したフォノン温度分布から電子-フォノン散乱確率を更新、その情報を電子伝導モデルに逐次フィードバックした。

図 4: 本研究で提案した熱電気連成シミュレ

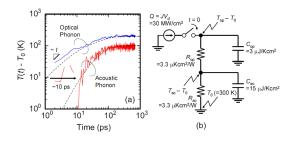

図5にシミュレーション結果を示す。発熱に よるドレイン端の音響および光学フォノン 温度の上昇を、素子ターンオン後の時間の関 数としてプロットした。チャネル長 10 nm の 極微細素子の場合、ソースから注入された電 子は印加電圧から得た運動エネルギーの大 部分をドレイン内部にて光学フォノンを放 出することで失う。光学フォノンは群速度 が遅いため、熱が周囲に拡散するにはフォノ ン-フォノン散乱を通じた音響フォノンへの 変換を待たなければならない。それらの描像 を反映し、図 5 (a) からは、ターンオン直後 の線形( $\propto t$ ) の光学フォノン温度の上昇、およ び光学→音響への緩和(= 10 ps を仮定) を経 ての音響フォノン温度の立ち上がりの様子 がわかる。なお、これらのシミュレーション 結果は図 5 (b) に示す熱等価回路で良好に記 述することが可能である。

図 5: ドレイン端における局所格子温度の過渡シミュレーション結果 (a)。実線: MC シミュレーションの結果、破線: 熱等価回路(b) による計算結果。

#### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## [雑誌論文] (計4件)

① Tatsuhiro Numata, Shigeyasu Uno, Yoshinari Kamakura, Nobuya Mori, and Kazuo Nakazato, "An Analytic Circuit Model of Ballistic Nanowire Metal-Oxide-Semiconductor Field-Effect Transistor for Transient Analysis," Jpn. J. Appl. Phys., vol. 52, 04CN01 (1-7), 2013.

②<u>Yoshinari Kamakura</u>, Takashi Himukashi, Hiroshi Tsuji, and Kenji Taniguchi, "Characteristics of Hot Hole Injection, Trapping, and Detrapping in Gate Oxide of Polycrystalline Silicon Thin-Film Transistors," Jpn. J. Appl. Phys., vol. 51, no. 2, pp. 02BC05(1-4), 2012.

③ Yoshinari Kamakura, Tomofumi Zushi, Takanobu Watanabe, Nobuya Mori, and Kenji Taniguchi, "Impact of Self-Heating Effect on the Electrical Characteristics of Nanoscale Devices," Key Engineering Materials, vol. 470, pp. 14-19, 2011.

④ Tomofumi Zushi, Yoshinari Kamakura, Kenji Taniguchi, Iwao Ohdomari, and Takanobu Watanabe, "Molecular Dynamics Simulation on Longitudinal Optical Phonon Mode Decay and Heat Transport in a Silicon Nano-Structure Covered with Oxide Films," Jpn. J. Appl. Phys., vol. 50, no. 1, pp. 010102 (1-6), 2011.

### 〔学会発表〕(計6件)

①Indra Nur Adisusilo, Kentaro Kukita, and Yoshinari Kamakura, "Monte Carlo Simulation of Seebeck Coefficient of Si Nanostructure with Barrier Layers," The 2013 International Meeting for Future of Electron Devices, Kansai, June 5-6, Osaka, (2013).

②Kentaro Kukita, Indra Nur Adisusilo, and Yoshinari Kamakura, "Influence of Phonon Dispersion Relation on Thermal Resistance in Silicon Nanostructures" International Workshop on Computational Electronics (IWCE 2013), June 4-7, 2013) Nara.

③Kentaro Kukita, Indra Nur Adisusilo, and Yoshinari Kamakura, "Impact of Quasi-Ballistic Phonon Transport on Thermal Properties in Nanoscale Devices: A Monte Carlo Study," Technical Digest of International Electron Devices Meeting, Dec. 10-12, San Francisco, USA, pp. 411-414, (2012).

① Takefumi Kamioka, Hiroya Imai, Yoshinari Kamakura, Kenji Ohmori, Kenji Shiraishi, Masaaki Niwa, Keisaku Yamada, and Takanobu Watanabe, "Current Fluctuation in Sub-Nano Second Regime in Gate-All-Around Nanowire Channels Studied with Ensemble Monte Carlo/Molecular Dynamics Simulation," Technical Digest of International Electron Devices Meeting, Dec. 10-12, San Francisco, USA, pp. 399-402, (2012).

⑤Kentaro Kukita and Yoshinari Kamakura, "Monte Carlo Simulation of Phonon Transport in Silicon Thin films Including Realistic Dispersion Relation," accepted for the presentation at 15th International Workshop on Computational Electronics (IWCE 2012), (May 22-25, 2012) Madison, USA.

⑥Y. Kamakura, N. Mori, K. Taniguchi, T. Zushi, T. Watanabe, "Coupled Monte Carlo Simulation of Transient Electron-Phonon Transport in Nanoscale Devices," Proc. International Conference Simulation of Semiconductor Processes and Devices, pp. 89-92, 2010.

## [図書] (計2件)

- ① 森伸也[編著], 鎌倉良成[分担執筆 1-2 章], "OHM 大学テキスト量子物理," オーム社,

- ② 大村泰久[編著], 鎌倉良成[分担執筆 1-3 章, 15 章], "OHM 大学テキスト半導体デバイス工学,", オーム社, 2012.

- 6. 研究組織

- (1)研究代表者

鎌倉 良成 (KAMAKURA YOSHINARI) 大阪大学・大学院工学研究科・准教授 研究者番号:70294022

- (2)研究分担者 なし

- (3)連携研究者

森 伸也 (MORI NOBUYA) 大阪大学・大学院工学研究科・准教授 研究者番号:70239614

渡邊 孝信 (WATANABE TAKANOBU) 早稲田大学・理工学術院・教授

研究者番号:00367153