# 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成 25 年 3 月 31 日現在

機関番号:10106

研究種目:基盤研究(C)研究期間:2010~2012課題番号:22560356

研究課題名(和文) 複素信号処理のための低電圧動作アナログ信号処理回路

研究課題名(英文) Low Voltage Operation Analog Signal Processing Circuits for

Complex Signal Processing

研究代表者

谷本 洋 (Hiroshi Tanimoto)

北見工業大学・工学部・電気電子工学科・教授

研究者番号: 20322886

研究成果の概要(和文): アナログ複素信号処理を微細 CMOS プロセス LSI で行う際に必須の,低電源電圧で動作する全差動演算増幅器を実現した. 電源電圧が 1V および 0.5V で動作する 2 種類の全差動演算増幅器を  $0.18\mu m$  CMOS プロセスで設計・試作し,それぞれ 82dB および 35dB の電圧利得と約 10MHz および 30MHz の帯域幅を,  $200\mu W$  および  $300\mu W$  の低消費電力で実現した. また,3 相アクティブ複素フィルタの構成法を研究し,必須とされていた同相抑圧が不要な回路形式を見出し,2 次の同フィルタを想定の 1/4 の  $270\mu W$  で実現した. これらの成果により,各種アナログ回路がより低電圧・低消費電力で実現可能になる.

研究成果の概要(英文):Fully-differential amplifiers operable from 1V or 0.5V power supply have been designed and fabricated. They show 80dB and 35dB of gain, 10HMz and 30MHz of bandwidth by  $200\mu W$  and  $300\mu W$  of power dissipation, respectively. A class of three-phase active complex filter architecture that does not require common-mode rejection has been found by the author and a test chip has been made successfully with low power dissipation of 1/4 than expected. These results are useful in realizing less power consuming analog circuits.

# 交付決定額

(金額単位:円)

|        | 直接経費        | 間接経費     | 合 計         |

|--------|-------------|----------|-------------|

| 平成22年度 | 100, 000    | 30,000   | 130, 000    |

| 平成23年度 | 2, 700, 000 | 810, 000 | 3, 510, 000 |

| 平成24年度 | 500, 000    | 150, 000 | 650, 000    |

| 年度     |             |          |             |

| 年度     |             |          |             |

| 総計     | 3, 300, 000 | 990, 000 | 4, 290, 000 |

研究分野:工学

科研費の分科・細目:電気電子工学,通信・ネットワーク工学

キーワード:電子回路網,アナログ複素信号処理

### 1. 研究開始当初の背景

(1) これまでのアナログ複素信号処理は周波数変換に関連した部分で利用されてきたが、アナログ複素信号処理は、I/Qの2系統の信号をそれぞれ差動信号として処理する「4相信号処理」で実現されることが殆んどであった。しかし、複素信号処理を行うには

理論的に「3 相信号処理」で十分であることが知られていた。3 相処理にすることでハードウェア量と消費電力が4 相信号処理の3/4に低減できる可能性が明らかであるにも関わらず、これを実際に行おうとする試みは筆者らの検討を除いて殆んど見られなかった。

(2) このようなアナログ複素信号処理回路を最先端のLSI技術で実現する場合に生ずるもうひとつの重大な問題として,アナログ回路に対する低電源電圧下における動作があり,最先端のLSI技術では電源電圧が従来のアナログ回路の動作下限電圧である1Vを下回るようになっていることが挙げられる.この問題は「IVの壁」と呼ばれ,克服は困難回あるとの声が根強かったが,複素信号処理回路を含むあらゆるアナログ回路分野で1V以下の低電源電圧で動作可能な回路の研究が行われる機運が出つつあった.

# 2. 研究の目的

このような状況から、単にアナログ複素信号処理回路の実現法を研究するだけでは十分でなく、高集積度・高速動作・低消費電力といった最先端LSI技術のメリットを享受するためには、それが1V以下の電源電圧で動作するようにしなければ意味がないと考え、次のような研究目的を掲げた.

- (1) アナログ複素信号処理を行うために必要な要素回路ブロック(演算増幅器,4相複素フィルタだけでなく,3相増幅器,3相複素フィルタ等)の回路実現法を研究する.

- (2) その際, 1 V以下の電源電圧でも動作可能な要素回路ブロックを実現し(0.5V動作の実現可能性も研究する), 実際にLSIとして試作・実証まで行う.

### 3. 研究の方法

- (1) 複素信号処理回路自体の研究 電源電圧の制約を受けない受動4相RCポリフェーズフィルタ(RCPF)の伝達関数の厳密設計手法,RCPFの寄生容量による高域減衰の補償法,可変RCPFの実現手法について理論的に検討した.特に,高域減衰の補償法について,キャパシタの下部電極の寄生容量を,drivenshield技法により打ち消す手法を提案した.

- (2) 1Vないし0.5Vで動作可能な演算増幅器の実現方法の研究 1V以下の電源電圧では従来広く使われてきた差動対による増幅器が満足に動作しない.これに代えて,より低い電源電圧でも動作可能なCMOSインバータを単位回路として全差動増幅器を実現する.ただし,CMOSインバータはシングルエンド増幅器(1入力1出力の増幅器)であるため、これを用いて全差動増幅器を実現するためには同相信号の抑圧方法導入が必須である.同相抑圧法としては,筆者らの提案になるFF-FB (Feedfoward-Feedback)構成を採用する.なお,設計と試作は0.18μm CMOSプロセスで行う.

- ① 1V 動作版:3 相複素フィルタの設計において必要となる 1V で動作するシングルエン

- ド増幅器を基に、その派生物として直流利得が 80dB 以上確保できる全差動演算増幅器を設計する手法を研究した.

- ② 0.5V 動作版:上記とは別に 0.5V で動作する全差動演算増幅器を設計する. 0.5V 動作を可能にする方法として,バックゲートを入力端子として利用する方法を採用する. 試作を行う  $0.18\mu m$  CMOS プロセスでは,標準的な関値電圧  $V_{th}$  が 0.4V 程度であるが,インバータが正常にアナログ動作するためには,最低る・ $V_{th}$  の 2 倍の電源電圧 (0.8V) が必要である・本研究では,通常は不都合を生ずる基板バイアス効果を逆用してバックが必須である。本研究では,通常は不都合を生ずる基板バイアス効果を逆用してバック方服することを試みた。同相抑圧法については 1V 版と同様とした・

# 4. 研究成果

- (1) 4相 RCPFの厳密設計手法に関する研究 筆者のこれまでの研究結果ならびに文献調査の結果に基づいて、従来断片的にしか知られていなかった厳密設計手法を集大成した。これにより、等リプル設計と最大平坦設計が伝達関数レベルだけでなく、素子値の決定を含めて系統的に行うことが可能となった。この成果は電子情報通信学会基礎・境界ソサイェティ英文論文誌の論文(2013年2月号)として発表した。

- (2) 1V~0.5V の電源電圧で動作する全差動 演算増幅器の設計と試作・評価

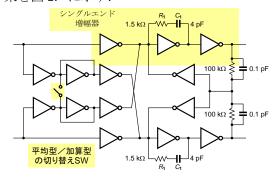

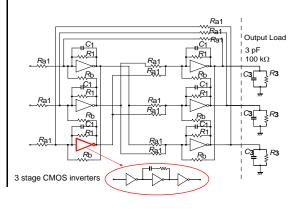

- ① 1V で動作する高利得 (80dB 以上) 全差動演算増幅器を,次のようなアイデアで設計した.まず,出発点として,CMOS インバータを3 段縦続接続し,2 段目にミラー補償を施した高利得のシングルエンド増幅器を設計する.これを2系統用意し,FF-FB 構成を適用した.回路構成を図1.に,試作・評価の結果を図2.に示す.

図1. 高利得型全差動演算増幅器の回路構成

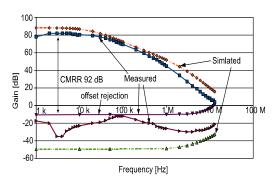

図 2. の結果から、電源電圧 1V (消費電流約 200µA) において差動利得が 82dB, 同相利得 は-10dB 以下が得られており、ユニティゲイン周波数も約 10MHz 得られ、通常の用途には

## 十分な性能が得られた.

図2. 差動利得と同相利得の周波数特性(実測結果)

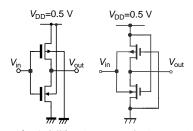

② 0.5V で動作する全差動演算増幅器の設計と試作・評価:電源電圧 0.5V の全域にわたる同相入力範囲を有する全差動演算増幅器を実現するため,要素回路としてバックゲート入力型 CMOS インバータ (図 3. 右)を用いる設計を採用し,試作チップを評価した結果,ほぼ設計どおりの特性が得られた.

図3. バックゲートを順バイアスにしたインバータ(左) と,バックゲートから入力するインバータ(右)

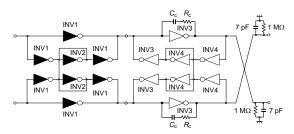

図 4. バックゲート入力型インバータ(黒)を用いた 0.5V 動作全差動演算増幅器の回路(2 段目は通常インバータ)

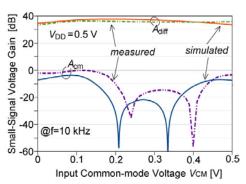

図 4. に回路図を示す. 図 5. に同相入力電圧を横軸に取った,差動利得と同相利得のシミュレーション結果と実測結果を示す.

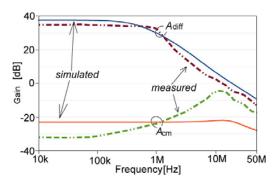

図5. 差動利得と同相利得の入力同相電圧依存性図5. より,設計値(シミュレーション結果)と実測値はよく合っており,同相入力電圧が電源電圧の半分の0.25Vのとき差動利得35dB,同相利得-32dBの値を得た.ユニティゲイン周波数は13MHzであり,消費電流が600μAなので消費電力は300μWに相当する.図6.に利得の周波数特性のシミュレーション値と実測値を示す.0.5Vの電源電圧の全範囲にわたって同相入力をキャンセルできる全差動演算増幅器の実現は,現状におけるチャンピオンデータと思われる.

図 6. 0.5V 動作演算増幅器の利得の周波数特性 (実測値)

以上の成果から,1V~0.5V程度の動作が可能な CMOS 全差動増幅器の実現可能性が明らかになった.今後の実用化に向けて,利得が低い点と,消費電流が電源電圧に依存しやすい点を改善する必要がある.

(3) アナログ複素フィルタの設計手法研究

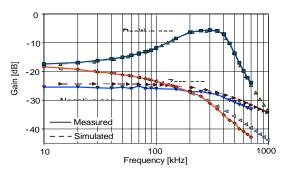

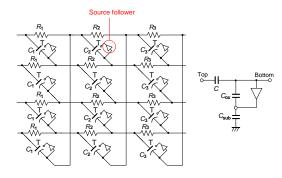

① 1V 動作する 3 相能動複素フィルタの設計と試作・評価 当初, 3 相増幅器を用いて実現する予定であったが,回路構成の工夫により,単相の増幅器でも零相抑圧効果を有する回路が構成可能であることを発見し,最も単純な 3 段縦続の CMOS インバータで 3 相複素能動フィルタを設計・試作した.評価の結果,ほぼ設計どおりの特性が得られ,消費電力を当初案の 1/4 以下の 270μWに低減できた.設計した 3 相能動複素フィルタの回路図を図 7.に、その利得の周波数特性を図 8.に示す.

図7.3 相能動複素フィルタの回路図

図8.3 相能動複素フィルタの周波数特性(実測値)

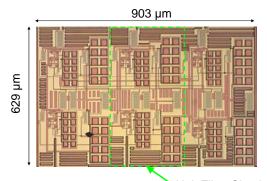

図8.より、設計値(シミュレーション結果)と実測結果がよく一致しており、複素フィルタ特有の性質である、正の周波数(Positive sequence)と負の周波数(Negative sequence)が異なる応答を示すことが確認できる。また、複素信号処理では不要な成分である零相(Zero sequence)の利得が通過域において20dB以上の減衰を受けていることも観察される。図9.にチップ写真を示す。

Unit Filter Circuit

図 9. 3 相アクティブ複素フィルタのチップ写真

② 可変4相RCポリフェーズフィルタの設計 測定・評価 比帯域を可変する場合に通過域 の等リプル性の変化を少なくする目的で,抵 抗と容量を同時に可変する方式を提案し,こ れに基づいた設計・試作を行った. さらに, 可変・非可変に関わらず,従来からRCポリ フェーズフィルタで問題となっていた寄生 容量による高域における利得低下をキャン セルする回路を発案し,設計・試作した.

評価の結果,可変機能は確認できたが,本体以外の測定用に組み込んだ回路の性能不足で,高域の利得低下キャンセルの効果は確認できたものの十分に評価・実証できなかった

キャパシタの下部電極の寄生容量の影響をキャンセルする回路を図10. (左)に示す. 同図中の寄生キャンセル回路の詳細を同図 (右)に示す.

図 10. キャパシタの下部電極寄生をキャンセルした RCPF(左)と,キャンセル回路の詳細(右)

#### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

#### 〔雑誌論文〕(計1件)

① <u>Hiroshi Tanimoto</u>, "Exact Design of RC Polyphase Filters and Related Issues," 查読有, *IEICE Trans. on Fundamentals*, Vol. E96-A, No. 2, pp. 402-414, Feb. 2013.

DOI: 10.1587/transfun. E96. A. 402

# 〔学会発表〕(計7件)

- ① Eiji Kuwahara, <u>Hiroshi Tanimoto</u>, Kazuhiro Shouno, "Design of Three-Phase Active Complex Filter Based on CMOS Inverters," Proceedings of ITC-CSCC 2012, B-W2-05, Sapporo, July 2012.

- ② Yuki Fujioka, <u>Hiroshi Tanimoto</u>, "Design of Fully Differential OTA Using Bulk-Driven CMOS Inverters Operating from 0.5V Power Supply," Proceedings of ITC-CSCC 2012, G-M1-05, Sapporo, July 2012.

- ③ Akitomo Tanaka, <u>Hiroshi Tanimoto</u>, "Design of Integrated Variable RC Polyphase Filter in 0.18 um CMOS Technology," Proceedings of ITC-CSCC 2012, G-M1-06, Sapporo, July 2012.

- ④ 田中昂友, <u>谷本洋</u>, 「抵抗と容量を同時に 可変する RC ポリフェーズフィルタの設 計」, 平成 23 年度電気・情報関係学会北 海道支部連合大会講演論文集, 8, 2011 年 10 月

- ⑤ 藤岡侑記, <u>谷本洋</u>, 「1 V で動作するカスコード型 FF+FB OTA の DC 評価」, 平成 23年度電気・情報関係学会北海道支部連合大会講演論文集, 7, 2011年 10月

- ⑥ 桑原英司,<u>谷本洋</u>,「CMOS インバータを 用いた3相複素フィルタの零相抑圧度の

検討」, 平成 23 年度電気・情報関係学会 北海道支部連合大会講演論文集, 6, 2011 年 10 月

- ⑦ 桑原英司,<u>谷本洋</u>,庄野和宏,「多相回路の素子感度解析に関する一検討」,電気学会電子回路研究会資料,ECT-11-049,2011年6月

- 6. 研究組織

- (1)研究代表者

谷本 洋 (Hiroshi Tanimoto) 北見工業大学・電気電子工学科・教授 研究者番号: 20322886