# 科学研究費助成事業(科学研究費補助金)研究成果報告書

平成 25 年 6 月 5 日現在

機関番号: 1 2 6 0 1 研究種目:若手研究(B) 研究期間:2010 ~ 2012 課題番号:22700053

研究課題名(和文) 次世代超低電力メニコア向けプログラム自動マッピングアーキテクチャ

の研究

研究課題名 (英文) Automatic Mapping Architecture for Ultra Low Power Many-core

Processor 研究代表者

中田 尚 (NAKADA TAKASHI)

東京大学・大学院情報理工学系研究科・特任助教

研究者番号:00452524

研究成果の概要(和文):次世代超低電力メニコアにおいて最大の課題となるデータ供給スループットの制約を解消するための、既存汎用プログラムを線形アレイ型プロセッサに自動的にマッピングする手法および最適なハードウェア構成の自動判定手法を提案した。また、ハードウェア規模を超える命令列を実行するための時分割実行機構および対故障機能を導入した場合の性能及びハードウェアコストの評価を行い、適用範囲の拡大を確認した。

研究成果の概要 (英文): Automatic mapping architecture has been proposed. It enables us to use existing programs on linear array processors, which can achieve high performance with limited data supply throughput. A tradeoff between performance and hardware cost is explored. Additionally, time division execution and fault tolerant mechanisms are proposed and their feasibility is evaluated. We have confirmed that wider range of application for linear array processors.

## 交付決定額

(金額単位:円)

|         |             |          | (亚州十四・11)   |

|---------|-------------|----------|-------------|

|         | 直接経費        | 間接経費     | 合 計         |

| 2010 年度 | 900, 000    | 270, 000 | 1, 170, 000 |

| 2011 年度 | 1, 100, 000 | 330, 000 | 1, 430, 000 |

| 2012 年度 | 900, 000    | 270, 000 | 1, 170, 000 |

| 年度      |             |          |             |

| 年度      |             |          |             |

| 総計      | 2, 900, 000 | 870, 000 | 3, 770, 000 |

研究分野:総合領域

科研費の分科・細目:情報学・計算機システム・アーキテクチャ キーワード:計算機アーキテクチャ、計算機システム、省エネルギー

#### 1. 研究開始当初の背景

高性能プロセッサ分野は、消費電力低減のために動作周波数追求から並列度追求へ大きく方向転換している。大まかには、数個のプロセッサを併置したマルチコア、GPGPUのような数十個以上のプロセッサを併置したメニコア、ADRES(IMEC)のような再構成型に分類することが出来る。

しかし、これらのプロセッサにはプログラミングモデルの転換や革新的自動並列化コンパイラ技術などのブレークスルーが必要であり、普及は困難を極めている。また、外部バス競合、コア間ネットワークの混雑、分割損の増大など、性能向上を妨げるとともに、性能予測を困難にする要因が山積している。そのため、最悪時を想定した過剰なハードウ

ェア投資を強いられ、結果として消費電力が さらに増大してしまう。

これまでに超高性能を実現した方式として、ベクトル型プロセッサがある。これは、多量のハードウェア資源を投入して実現した潤沢なメモリスループットと、多量のデータを保持するためのベクトルレジスタを備えており、最内ループを対象に連続したデータに対して同一の演算を繰り返し行うことに対して同一の演算を繰り返し行うことに対して同い性能を実現した。しかし、実行対象のアプリケーションは、専用の命令で表であるとともに、データの依存関係や命令の実行順序に強い制約があり、専用のコンパイラで作成したプログラムが必要である。

その一方で、本提案研究で注目する線形アレイ型プロセッサはループ内の命令をすべて演算器アレイに写像し、演算器ネットワークを構築する。構築した演算器ネットワークにデータを順次流し入れることにより、専用ハードウェアに匹敵する性能に加え、処理の複雑さによらず安定したスループットを実現できるという特徴を持つ。

### 2. 研究の目的

次世代メニコアにおいて、コア数や実装演算器数の大規模化により演算能力を飛躍的に向上させることは比較的容易である。その一方、プロセッサにデータを供給するメモリや外部バスの性能向上は圧倒的に緩やかであり、データ供給スループットの不足により、演算器の性能が発揮できないことが非常に大きな課題となっている。

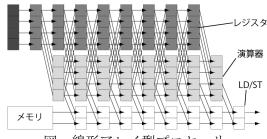

本研究課題では、既存のプロセッサ技術とは一線を画し、既存プログラムをほぼそのまま利用可能としつつ、高い性能と安定したスループットを実現する、線形アレイ型プロセッサ(図1)に注目する。

図:線形アレイ型プロセッサ

線形アレイ型プロセッサは、いくつかの典型的なアプリケーションに対しては非常に効果的であることが確認されている。また、演算器に対して命令を比較的長時間固定的に割り当てるために、動的に変化する部分が

最小限であり、クロックゲーティング等の低 消費電力技術との相性も良く、超低電力コン ピューティング実現の期待がある。しかし、 その評価はいまだ十分ではなく、特にソフト ウェア側の見地からの詳細な性能モデルや、 適応性の解析が必要不可欠である。このよう な状況に対し、本研究では線形アレイ型プロ セッサを詳細に解析することにより、その実 行モデルを明確にし、既存プログラムの自動 マッピング手法とマッピング後のプログラ ムの性能予測について研究を行う。マッピン グの手間は一般のメニコアなどと比較して 非常に少ないと考えられるが、これまでとは 大きく異なる実行モデルであるため、体系的 なマッピング手法の確立が重要である。また、 この解析結果を一般のメニコアなどの開発 にフィードバックすることにより、メニコア における諸問題の解決の一助となることが 期待できる。

#### 3. 研究の方法

本研究では、まず典型的ないくつかのアプリケーションを調査するとともに、手作業で変換したプログラムを用いて性能モデルの構築を目指す。ここでは、データ供給スループットをはじめとした各種制約条件下で、どこまでの性能が実現可能であるかの上限値を見極めることが重要である。

その後、自動マッピング手法の検討を行う。 モデル構築で利用したアプリケーションに 加えて、可能な限り多数のアプリケーション に提案手法を適用しその有効性を明らかに する。

さらに、解析結果を基に、個々の対象アプリケーションに対して、適正ハードウェア量の見積りを行う。この見積りを利用することにより、線形アレイ型プロセッサの利用者は事前に性能を予測することができるとともに、要求性能に対する過剰なハードウェア投資を防止する。

各研究項目について順に説明する。

## (1) 線形アレイ型プロセッサの正確な性能 予測

解析プログラム作成のために、典型的な複数のアプリケーションをソフトウェアシミュレータ上で実行することにより、その性能を測定する。この結果を幅広い角度から分析し、性能モデルを作成する。具体的には、対象アプリケーションに関しては、入力データサイズ、データの再利用性、ループ中の計算量および演算の種類、出力データサイズ、プログラム全体に対するアレイ実行可能な割合、プロセッサに関しては、入出力スループ

ット、アレイ幅および深さ、演算器構成についてそれぞれのパラメータを変化させた時の性能を測定する。また、同時に各種モジュールの動作率や動作間隔を測定することにより、クロックゲーティング等の低電力技術を適用した場合の効果を予測する。

ここでは、理論的な性能の上限を知る必要があるため、プログラムに手動で様々な変換手法を適用し、どのような変換を行えばハードウェアの性能を最大限引き出せるのかを調査する。

これらの結果を基に、さらなる性能向上の可能性を探り、ハードウェア機構の追加や既存のハードウェア機構の高度化を適用した場合の性能について検討する。具体的には、入力データのプリフェッチ、アレイ深さを超える長大ループへの対応などの検討を行う。

高効率コンピューティングのためには、各 モジュールの空き時間をできる限り削減することが重要である。究極的には、データの 入出力と演算の両方が絶え間なく実行されていることが望ましい。このためには、特に 入力データのプリフェッチタイミングがの 要であり、演算の実行中に次の演算のために データをキャッシュメモリに取り込むこと により、無駄な空き時間を削減することが きる。この手法を適用するためには演算に必 要なデータアクセスを妨げないタイミングを見極めることが重要である。

線形アレイ型プロセッサの有用性をさら に高めるためには、アレイの深さを超えれープへの対応が不可欠である。長大ループも実行可能なようにあらかじめアレイの 深さを大きくしておくことは性能に対投 は有効であるが、過剰なハードウェア投 は有効であるが、過剰ない。基本的には1 1である危険性が高い。そこで、基本的には1 でこの問題を解決する。具体的には1 でこの問題を解決する。具体的には1 でこの問題を解決する。具体的には1 でこのに実行することに り、演算スループットを犠牲にして、2 倍 きのループに対応することが可能と られる。しかし、演算器間にバッファレード となるためハードウェアコストのトレード オフを注意深く検討する必要がある。

(2) 既存プログラムの自動マッピング手法の提案

自動マッピングの基本的な考え方は、これまでに幅広く研究されてきた自動並列化コンパイラの知見を利用することができると考える。これにより、各ループに対して入出力データやその依存関係を解析し、アレイ化可能と判断した場合には、ループ開始命令とプリフェッチ命令の挿入を行なう。既存の自

動並列化では、データ分割やタスクスケジューリングのような非常に高度な処理を要求されるが、現在までに十分な性能の自動並列化コンパイラは実現されておらず、一般のメニコアにおけるアプリケーション開発レートきな障害となっている。一方、線形アレリをは、入出力解析のあとはヒント情報としてプリフェッチ命令を挿入するだけでよい。挿入すべきプリフェッチ命令を表れている。 終的な決定にはループ中のデータアクセスパターンの解析が必要であるが、これには必要に応じて動的プロファイリングの手法を用いる。

入出力スループットに制約のある条件では、計算の順序やプリフェッチの順序が性能に非常に大きな影響を与えるため、(1)で得られた解析結果とともに、プログラムが性能を最大限に発揮できる最適なソフトウェアとハードウェアのマッピング方式を検討する。自動でのマッピングが不可能または非効率的と判断した場合には、問題場所とその理由や、手動での変換方法などに関する情報をユーザに提供することが有用である。

(3) 特定ハードウェア構成における性能の 予測

(1)で得られた性能モデルを用いて、与えられたハードウェア構成で特定のアプリケーションプログラムを実行した場合の実性能と消費電力の見積りを提供する。これにより、ユーザは線形アレイ型プロセッサを採用した場合の効果を容易に予測できる。

初年度では与えられたハードウェア構成に 対する性能予測であったが、さらに拡張し 様々なハードウェア構成に対する性能や消 費電力を予測し、その結果から自動的に最適 なハードウェア構成を提案する。また、いく つかのパラメータに対して制約が与えられ ている場合にはその制約を満たす構成の中 で最適な構成を提案する。

#### 4. 研究成果

(1) 線形アレイ型プロセッサの正確な性能 予測

まず、RTLレベルのソフトウェアシミュレータを作成して、正確な性能予測を実現した。またHDL言語で対象プロセッサを設計し、電力シミュレーションを行った結果を基に作成した電力モデルを組み込みだ場合の正確な電力予測を実現した。また、この結果を用いて性能モデルを作成した結果高い一を開いて性能モデルを作成した結果高い一をを示し、対象プロセッサの性能が高い精度で予測可能であることがわかった。これにより、低速なシミュレーションを繰り返す必要

が無くなるため、研究の効率が飛躍的に高まった。

さらに、この高精度シミュレータを拡張し、 時分割実行および対故障機能を搭載した場 合の正確な性能予測に対応した。これにより、 より多くのプログラムに対して、適切なハー ドウェア構成を提案できるようになった。

(2) 既存プログラムの自動マッピング手法の提案

本計画については既存のコンパイラ(gcc)の拡張としてアセンブリ言語レベルのトランスレータを実装した。いくつかの典型的なプログラムに対しては全自動で変換が出来ることを確認した。これにより、専門的な知ることを確認した。これにより、専門的な知識が無くとも対象プロセッサを利用することが出来る。また、自動変換が困難な例も具体的に判明した。このようなプログラムは育動変換ではなくユーザにどういった点が障害になっているのかを適切に提示することが重要である。

また、ハードウェア規模を超える命令列を 実行するための方式を検討するとともに、そ の実現可能性を予備的に調査し、実現に向け た見通しを得た。

#### (3) 最適なハードウェア構成の検討

(1)で検討を行った時分割実行方式および 耐故障機能を搭載した場合の構成およびそ のハードウェアコストの評価を行った。これ らの成果を統合することにより、より多くの 構成候補から最適解を求めることが可能と なった。

## (4) まとめ

提案するソフトウェア自動マッピング手法は、既存のプログラムを数十〜数百の演算器を搭載した線形アレイ型プロセッサ上において、超高速、超高効率で実行を可能にする。また、解析結果からハードウェア構成に対する予測性能を出力することにより、アプリケーションに対する過剰なハードウェア投資を防止することが出来る。

将来的には本提案研究の結果を他のメニコア開発にフィードバックすることにより、 線形アレイ型プロセッサ以外の構成に対しても有意義な知見を与えられると考える。

以上のことから、本提案研究は次世代の超低消費電力メニコアプロセッサの可能を切り開くこととなり、極めて大きな意義がある。

# 5. 主な発表論文等 〔雑誌論文〕(計5件)

1. Yukihiro SASAGAWA, Jun YAO, <u>Takashi</u>

<u>NAKADA</u>, and Yasuhiko NAKASHIMA:

RazorProtector: Maintaining Razor DVS

Efficiency in Large IR-drop Zones by an

Adaptive Redundant Data-Path, IEICE

- TRANSACTIONS on Fundamentals of Electronics, Communications and Computer Sciences Vol.E95-A No.12 pp. 2319-2329 Dec. (2012)

- 齊藤光俊,下岡俊介,D.V.R. Naveen,大上俊,吉村和浩,姚駿,中田尚,中島康彦:線形演算器アレイ型アクセラレータを備えた高電力効率プロセッサの開発,電子情報通信学会論文誌 D, Vol. J95-D, No. 9, pp. 1729--1737, Sep. (2012)

- 3. 岩上拓也,吉村和浩,<u>中田尚</u>,中島康彦: 時分割実行機構による演算器アレイ型ア クセラレータの効率化,情報処理学会論 文誌コンピューティングシステム,Vol.5, No.4 (ACS39),pp. 13--23,Aug. (2012)

- 4. <u>中田尚</u>, 吉村和浩, 下岡俊介, 大上俊, Naveen, D. V. R., 中島康彦: 画像処理向け線形アレイアクセラレータの性能評価,情報処理学会論文誌コンピューティングシステム, Vol. 5, No. 3 (ACS38), pp. 74-85, May (2012)

- Kazuhiro Yoshimura, Takuya Iwakami, <u>Takashi Nakada</u>, Jun Yao, Hajime Shimada, Yasuhiko Nakashima: An Instruction Mapping Scheme for FU Array Accelerator, IEICE Transactions on Information and Systems, Vol. E94-D, No. 2, pp. 286-297, Feb. (2011)

## 〔学会発表〕(計12件)

- Yukihiro SASAGAWA, Jun YAO, <u>Takashi</u> <u>NAKADA</u>, Yasuhiko NAKASHIMA: "Improving DVS Efficiency by Tolerating IR-drops with an Adaptive Redundant Data-Path", WRA 2011: 2nd Workshop on Resilient Architectures, Dec. (2011)

- Naveen Devisetti, Takuya Iwakami, Kazuhiro Yoshimura, <u>Takashi Nakada</u>, Jun Yao, Yasuhiko Nakashima: "LAPP: A Low Power Array Accelerator with Binary Compatibility", HPPAC2011, pp. 849--857, May. (2011)

- 3. 岩上拓矢, 吉村和浩, <u>中田尚</u>, 中島康彦: "仮想化機構による演算器アレイ型アクセラレータの効率化", 先進的計算基盤システムシンポジウム SACSIS2011 論文集, pp. 136-143, May. (2011)

#### 6. 研究組織

(1)研究代表者

中田 尚 (NAKADA TAKASHI)

東京大学・大学院情報理工学系研究科・ 特任助教

研究者番号: 00452524