# 科学研究費助成事業 研究成果報告書

平成 26 年 6 月 10 日現在

機関番号: 14401 研究種目: 基盤研究(B) 研究期間: 2011~2013

課題番号: 23360155

研究課題名(和文)素子特性ばらつきの統計性に基づく微弱信号検出の線形性改善方法とその実現方式の探究

研究課題名 (英文 ) Study on Linearity Enhancement and Its Implementation in Stochastic Signal Detection

#### 研究代表者

松岡 俊匡 (MATSUOKA, TOSHIMASA)

大阪大学・工学(系)研究科(研究院)・准教授

研究者番号:80324820

交付決定額(研究期間全体):(直接経費) 13,900,000円、(間接経費) 4,170,000円

研究成果の概要(和文):無線通信機器の小型化、軽量化、及び多機能化・高性能化の要求に伴うCMOS集積回路の微細化、高速化、低消費電力化において、低電源電圧化による従来のA/D変換に基づくアプローチの限界を克服する必要がある。本研究では、自然界の生物の感覚器に見られる確率共鳴型信号検出の実用化の一歩として、確率的並列型A/D変換器の線形性改善を検討した。具体的には、コンパレータのオフセット電圧分布を意図的に操作することにより、分布の非線形性を低減できることを示した。この他、確率的A/D変換方式の応用の1つとして、マルチビット 変調器の量子化器への適用も検討し、内部D/A変換器誤差補正の可能性を示した。

研究成果の概要(英文): Demand for small-size light-weight multi-functional high-performance wireless communication systems requires small-size high-speed low-power CMOS integrated circuits. To realize them, brea k-through for limitation in design approaches based on conventional A/D converters is important. In this s tudy, as a step for stochastic signal detection seen in some creatures' sensory organs, linearity improvement of stochastic A/D converter was investigated. Concretely, by controlling distribution of comparators' offsets on purpose, nonlinearity originating from the offset's distribution was found to be reduced. In addition, as an application of stochastic A/D conversion, it was revealed that quantization based on the stochastic A/D converter can compensate error of internal D/A converter in a multi-bit Delta-Sigma modulator.

研究分野:工学

科研費の分科・細目: 電気電子工学・電子デバイス・電子機器

キーワード: 確率共鳴

# 1.研究開始当初の背景

近年、無線通信機器の小型化、軽量化、及び多機能化・高性能化の要求に従い、内蔵される集積回路にもさらなる微細化、高速化、低消費電力化が望まれる。現在、このような要望に応える技術として、デジタル回路を混載し小型化、低電力化に有利な CMOS デバイスによる無線通信用 RF・アナログ集積回路の研究開発が国内外で盛んに行われている。これらは CMOS デバイスの微細化に依る所が大きい。

研究代表者は無線通信用 RF・アナログ集 積回路の要素技術を研究開発しており、豊富 な研究開発の経験を持つ。0.5V という低電源 電圧対応に向けた無線通信用 RF・アナログ 回路要素技術に関して先駆的な研究成果 ("Low-Voltage Wireless Analog CMOS Circuits toward 0.5 V Operation," T. Matsuoka, J. Wang, T. Kihara, H. Ham, Taniguchi, and K. IEICE Trans. Fundamentals, E93-A(2), pp. 356-366, 2010.)も出している。これらは、弱反転動作 や順方向アクティブ・ボディ・バイアスなど のデバイス特性を活用して創出した回路技 術である。

しかし、将来を考えると、微細化に伴う低電源電圧化のため、従来の A/D 変換に基づくアプローチでは雑音、ミスマッチもしくは非線形歪みによる限界があり、回路・システム・レベルでの克服が期待される。

#### 2.研究の目的

このような背景を踏まえ、研究代表者は、 自然界の生物の感覚器が行っている信号検 出方法に範を求め、確率共鳴という非線形現 象に着目し、雑音やミスマッチの統計性を巧 みに利用することで、従来の限界を超える信 号 検 出 感 度 の 向 上 を 目 指 し て い る ("Application of Noise-Enhanced Detection of Subthreshold Signals for Communication Systems," H. Ham, T. <u>Matsuoka</u>, and K. Taniguchi, IEICE Trans. Fundamentals, E92-A(4), pp. 1012-1018, 2009.)。

本研究では確率共鳴型信号検出の実用化を究極的な研究目的に掲げ、比較器のオフセット電圧の分布に対するデジタル的補正方式などを展開し、それらを基礎として、懸案の線形性改善に向けて探究する。なお、本研究の信号検出器の出力はデジタル信号であることから、以後、広義のA/D変換器として扱うこととする。

### 3.研究の方法

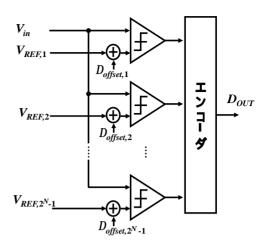

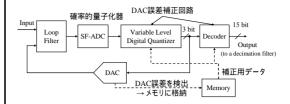

図 1 に示す確率的並列型 A/D 変換器 (SF-ADC) は、ランダムな閾値を持つフラッシュ型 A/D 変換器であり、参照電圧生成器が存在せず、コンパレータ・オフセットによって閾値が決定される。本研究で扱う CMOS デバイスに関しては、熱雑音よりもミスマッ

図 1 確率的並列型 A/D 変換器

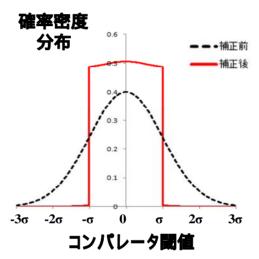

図2 コンパレータ閾値分布

チの影響の方が大きく、コンパレータで発生する誤差分をコンパレータの入力側に換算して表した時、その入力換算オフセットは素子寸法や回路のトポロジーなどによって決まり、一般的にガウス分布でモデル化される。つまり、SF-ADC 全体においてコンパレータ 閾値が図 2 の破線に示すようなガウス分布に従うことを意味し、コンパレータ出力を加算した出力はガウス累積分布に従う。 しかし、この場合、A/D 変換可能な最大入力電圧もオフセットに依存する。

入力電圧範囲を拡大するための非線形成 分を低減させる技術を以下に述べる。入力 電圧を印加した状態で全コンパレータの中 16%が 'high '出力になる場合、 その入 力電圧がコンパレータ群の閾値分布におけ る - σ( :標準偏差)に、 同様に 84% が 'high'出力になる入力電圧がその回路の にほぼ相当する。 そこで、 A/D 変換器として利用する前に、 閾値が  $-\sigma$  以下 であるコンパレータの参照電圧に +2 の電圧を加算し、閾値が より大きなコ ンパレータの参照電圧には - 2σ の電圧を 印加する。 このように補正を行うことで、 コンパレータ群の閾値分布が図 2 の実線 のようになり、 - ~ の間で一様分布 に近くなるため、コンパレータの閾値分布 の非線形性の影響が緩和される。

本研究では、この実現可能性を Verilog-A などの動作レベルで効果を検証した後、回路シミュレータなどで詳細な検討を行う。また、130nm CMOS プロセスなど、設計・試作の比較的容易なものを用いて、回路実装することまでを行うことを目指す。

#### 4.研究成果

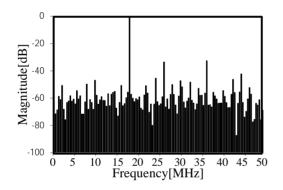

130nm CMOS プロセスを用いて、SF-ADC を設計した。コンパレータ数は511個、サンプリング周波数は100MHzとした。振幅44mV、周波数18.36MHzの正弦波入力に対する出力スペクトルを図3に示す。上述の非線形成分低減技術を用いており、SFDR32.7dB、SNDR28.9dBが得られた。これは、非線形成分低減技術を用いない場合に比べて、各々7dBの改善になっている。なお、この回路の電源電圧は1.2Vとし、消費電力は1.1mWである。

図 3 SF-ADC の出力スペクトルの シミュレーション結果

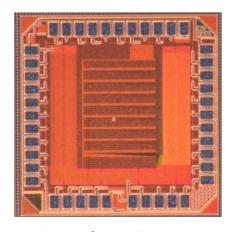

図 4 試作チップの写真(130nm CMOS Process)

図 5 SF-ADC を適用したマルチビット 変調器

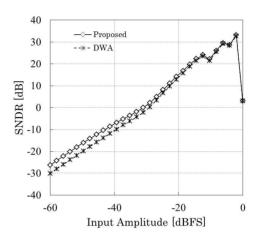

図 6 DWA と提案方式の比較

この設計結果に基づき試作した集積回路 の写真を図 4 に示す。チップは 1.4mm 角 程度の大きさである。基本的な動作の確認 はできており、今後、詳細な評価を実施す る予定である。

この他、SF-ADC の更なる応用を目指し て、マルチビット 変調器の量子化器へ の SF-ADC の適用も検討している。図 5 にその例を示す。マルチビット 変換器において、ミスマッチによる内部 D/A 変換器 (DAC) の非線形誤差が問題と なる。この誤差の分解能への影響を低減す る技術として、従来のダイナミック・エレ メント・マッチング (Dynamic Element Matching, DEM) に代わって、SF-ADC 出力に対して可変レベルのデジタル比較を 行うブロックを量子化器とし、DAC 出力レ ベルに応じた量子化を行うものである。な お、この補正により量子化器は非線形な特 性を持つことになるため、出力されるディ ジタルコードには非線形なアナログ値が対 応することになる。このため,デコーダに おいて少数コードを付加することでディジ タルコードとアナログ値の関係が線形とな るようにコードを補正することになる。量 子化特性の非線形化およびコードの補正は 起動時などに基準信号の入力により得られ た DAC 誤差の情報に基づいて行うことが できる。図6にシミュレーション結果の例

を示すが、低振幅信号入力に対して、従来の DEM の 一種 で ある DWA(Data Weighted Averaging)よりも良好な SNDR が得られることがわかる。

このように、SF-ADC は,他の A/D 変換器への応用も十分期待できるものであり、低電源電圧微細 CMOS RF・アナログ集積回路技術の根幹となる可能性も秘めており、近い将来、ナノエレクトロニクスの発展の礎ともなり得るものである。

## 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

### [雑誌論文](計2件)

ハム ヒョンジュ, <u>松岡俊匡</u>, 王軍, 谷口研二、"素子特性ミスマッチを用いた並列型確率 A-D コンバータ"、電気学会論文誌 C, Vol. 131-C、No. 11、pp. 1848-1857、Nov. 2011(査読有)

DOI: 10.1541/ieejeiss.131.1848

H. Ham, <u>T. Matsuoka</u>, J. Wang, and K. Taniguchi 、 "Design of a High-Speed-Sampling Stochastic Flash Analog-to-Digital Converter Utilizing Device Mismatch" 、 Electronics and Communications in Japan、Vol. 96、No. 1、pp. 51-62、Jan. 2013(查読無)

DOI: 10.1002/ecj.11411

#### [学会発表](計3件)

矢野 新也, ハム ヒョンジュ, <u>松岡 俊匡</u>、 "Stochastic Flash A-D コンバータの非線形 成分補正の検討"、平成 23 年電気関係学会 関西支部連合大会、2011 年 10 月 29 日~30 日、姫路

矢野 新也, ハム ヒョンジュ, 松岡 俊匡, 王 軍、チョウ イキュン、"非線形成分補正 機能を有した確率的並列型 A/D 変換器の設計"、電子情報通信学会集積回路研究会、 2012年10月18日~19日、盛岡

平井雄作,矢野新也,松岡俊匡、"マルチビット 変調器における確率的量子化器によるDAC誤差補正"、電気学会電子回路研究会、2013年10月3日~4日、奈良

## 〔産業財産権〕

出願状況(計1件)

名称: A/D 変換装置 発明者:松岡俊匡、平井雄作

権利者:株式会社半導体理工学研究センター

種類:特許

番号:特願 2013-098617

出願年月日:平成25年5月8日

国内外の別: 国内

取得状況(計0件)

# [その他]

ホームページ等

http://www.si.eei.eng.osaka-u.ac.jp/

## 6. 研究組織

#### (1)研究代表者

松岡 俊匡 ( MATSUOKA, Toshimasa ) 大阪大学・大学院工学研究科・准教授 研究者番号:80324820

(2)研究分担者 なし

(3)連携研究者 なし