# 科学研究費助成事業 研究成果報告書

平成 26 年 6月16日現在

機関番号: 25403 研究種目: 基盤研究(C) 研究期間: 2011~2013

課題番号: 23500066

研究課題名(和文) FPGAの動的部分再構成機能を利用した組合せ問題に対する高速ハードウェア解法

研究課題名(英文)Efficient Hardware Algorithms for Solving Combinatorial Optimization Problems by Using FPGAs with Dynamic Partial Reconfiguration

#### 研究代表者

若林 真一(Wakabayashi, Shin'ichi)

広島市立大学・情報科学研究科・教授

研究者番号:50210860

交付決定額(研究期間全体):(直接経費) 4,000,000円、(間接経費) 1,200,000円

研究成果の概要(和文):本研究では、部分再構成可能 FPGAを利用した組み合わせ最適化問題の解法について研究を行った。まず、大規模グラフに対する最大クリークを求めるハードウェア解法を提案した。提案解法は、部分グラフを複数生成することで、1つのFPGAで解を得ることができる。次に、充足可能性問題に対し、従来手法であるボトムアップ解法を基に、大きな論理式に対しても1つのFPGAで解が得られるように、FPGAの部分再構成機能を利用したハードウェア解法を提案した。最後に、任意の正規表現を扱うことができ、瞬時にパターン更新が可能であるという特長を保ちつつ、従来手法より回路面積を削減した正規表現マッチングハードウェアを提案した。

研究成果の概要(英文): In this research, we proposed several hardware algorithms to solve combinatorial o ptimization problems. First, we proposed a hardware algorithm to solve the maximum clique problem of larg e graphs by producing a set of small subgraphs, and show its implementation results using a dynamically pa rtially reconfigurable FPGA. Second, we proposed a new hardware satisfiability solver, which is based on the bottom-up solver proposed in our previous study. It can obtain a solution for a large instance of the problem. Third, we proposed a regular expression matching (REM) hardware engine. In the proposed method, the circuit size is reduced keeping the advantages that any RE can be handled and a pattern can be update d immediately.

研究分野: 総合領域

科研費の分科・細目: 情報学・計算機システム・ネットワーク

キーワード: FPGA 動的部分再構成 組合せ最適化 ネットワーク侵入検知

### 1.研究開始当初の背景

(1) FPGA (Field Programmable Gate Array)の回路構成の一部を実行中に動的に変更する機能を動的部分再構成という。この技術は2001 年頃から開発されており、2005 年頃からはハードウェア的には市販の FPGA チップで利用可能になっていたが、この機能をサポートする設計ツールが FPGA メーカーから正式提供されておらず、従って実用にも供されていなかった。しかし、平成22年(2010年)になって、 FPGA の大手メーカ (Xilinx社)がこの機能をサポートする設計ツールを正式にサポートすることになったため、動的部分再構成機能を活用した FPGA の応用が容易になった。

(2) 動的部分再構成機能を利用すれば、FPGA の応用範囲の拡大や問題解決の実行時間の 短縮が可能になると予想されているが、動的 部分再構成機能を前提とした FPGA の応用に 関する研究はまだ緒についたばかりであり、発表された研究成果は限られている。先行研究の例としては、正規表現マッチングに対するハードウェア解法や充足可能性問題(SAT)問題に対する解法などがあるが、例えば SAT 問題以外の NP 困難問題に対する解法は研究代表者が調べる限り、ほとんど発表されていない。本研究では、FPGA の動的部分再構成機能を利用した組合せ問題の高速ハードウェア解法を研究開発しようとするものである。

#### 2.研究の目的

本研究の目的は、動的部分再構成機能が搭載された FPGA を利用して、NP 困難問題に対する厳密解探索やネットワーク侵入検知における正規表現マッチングに対し、組合せ問題の最適解を短時間で高速に得るための新しいハードウェア解法を開発することである。提案手法により、組合せ問題の最適解をソフトウェアによる従来手法と比較して、高速にかつ低コストで求めることが可能にな

る。さらに、計算デバイスとしての FPGA の新しい可能性を実証することで、FPGA 応用に関する研究の進展に資することを目的とする。

### 3.研究の方法

(1) NP 困難問題に対するインスタンス依存八 ードウェア解法に関する研究代表者らの従 来研究の成果を、動的部分再構成機能を利用 したハードウェア解法に拡張する。従来研究 においては、インスタンスに依存しない部分 (基本回路と呼ぶ)も、インスタンスに依存 する部分(インスタンス依存回路と呼ぶ)も 一緒に論理合成・配置配線を行っていた。こ れを、基本回路を論理合成・配置配線し FPGA に実現した上で、基本回路とインスタンス依 存回路とのインタフェースを定義し、インス タンス依存回路を基本回路とは独立に論理 合成・配置配線が可能となるようにハードウ ェア解法の構成を変更する。本研究では、組 合せ問題としてグラフの最大クリーク問題 に注目し、この問題に対する新しいハードウ ェア解法を開発する。

(2) 論理式の充足可能性 (SAT) 問題に注目 し、SAT 問題に対するハードウェア解法を新 たに提案する。本手法は与えられた論理式を 複数の論理式に分割し、分割統治法に基づい てボトムアップに部分論理式の充足可能性 判定を行うことで、最終的に論理式全体の充 足可能性判定を行う手法である。回路は均一 の構造を持つ論理式評価回路を1次元配列状 に接続したものであり、FPGA への実現が容易 である。回路全体の構成は論理式に依存しな いが、部分論理式の評価回路は与えられた論 理式(インスタンス)に依存する。この特徴を 活かして、回路の基本機能をあらかじめ FPGA に実現しておき、インスタンスに依存する部 分は FPGA の動的部分再構成機能を利用して テンプレートで記述し、実行時に回路を再構 成することで効率よく解を求める。

(3) 研究代表者らはネットワーク侵入検知のための正規表現マッチングの研究を続けており、多くの研究業績を挙げている。我々が提案しているマッチング手法はシストリックアルゴリズムに基づくものであり、実行時にパターンを設定可能という特長を持つ。提案アルゴリズムはセルと呼ばれるプロセッシングユニットを1次元配列状に接続した回路として実現される。本研究では、FPGAの動的部分再構成機能を利用して複数種類の基本セルを基本回路として事前に応じて動的にマッチング回路を構成する。これにより、パターンに対応した回路を従来手法より少ないハードウェア資源で実現可能になる。

#### 4.研究成果

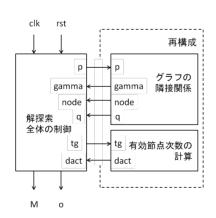

(1) 大規模グラフに対する最大クリークを 求めるハードウェア解法を提案し、提案解法 を部分再構成可能 FPGA 上に実装し、実験的 評価を行い、提案解法の有効性を確認した。 提案解法は従来手法では1つの FPGA で解く ことができない大規模グラフに対しても部 分グラフを複数生成し、FPGA の部分再構成機 能を用いることにより、1つの FPGA で解を得 ることができる。提案解法のハードウェア構 成を図1に示す。

図1 最大クリーク問題に対する提案回路

良く探索できるだけでなく、FPGA の部分再構成回数も削減することができる。提案手法を部分再構成機能を備えた FPGA 上に実装し、評価実験を行った。実験結果より、既存手法では得られなかった大規模グラフに対する解が高速に得られることを確認した。

- (2) 充足可能性(SAT)問題とは、与えられた 論理式の値が1となる (充足する)変数への真 理値割り当てが存在するか否かを判定する問 題であり、高速な解法を求めて多くの研究 が行われている。特に近年、FPGA によるハードウェア解法が注目されているが、大きな 論理式に対しては多くの既存解法は1つの FPGA に実装できず、解を得られない。そこで 本研究では、従来研究のボトムアップ解法を 基に、大きな論理式に対しても1つの FPGA で解が得られるように、FPGA の部分再構成を 用いたハードウェア解法を提案した。実験的 評価により、従来解法では解けなかった大き な論理式に対しても、提案解法では解けることが確認できた。

- (3) 正規表現マッチングとは、正規表現で表されたパターンと一致する文字列をテキストから検索する操作である。正規表現マッチングの応用として、データベース検索やネットワーク侵入検知システム(NIDS)などがある。これらの応用では、大規模なテキストデータに対する高速な正規表現マッチングが求められており、ハードウェア化に関する多くの研究が行われている。これまでに提案されている正規表現マッチングハードウェアの実装法は大きく分けて2つのアプローチに分類できる。

1つはパターン依存型であり、与えられた正 規表現パターンを非決定性有限オートマトン (NFA)に変換し、そのNFAをFPGAなどの再 構成可能デバイスに回路として実現する手法 である。パターン依存型は面積効率と処理性能 は非常に優れている。しかし、パターンが更新 される度に回路の再設計と再構成が必要となり、 パターン更新に時間がかかる。パターンが頻繁 に更新される NIDS 等の応用分野では、セキュ リティの観点から短時間でのパターン更新 が望ましく、この更新手法では大きな欠点 になりうる。

もう 1 つのアプローチはパターン非依存型である。これらの手法では、パターン更新時に回路の再設計や再構成が不要であり、瞬時にパターンを更新できる。しかし、1 つの回路で任意のパターンが扱えるように設計されているため、回路規模が大きくなるという欠点がある。回路規模縮小のため、扱える正規表現クラスを使用頻度の高い演算のみに制限した手法が提案されているが、頻繁に更新され続けるパターンに対して真に有効な正規表現の部分クラスをあらかじめ設定しておくことは非常に難しく、本質的な欠点の克服には至っていない。

本研究では、コンパクトな回路と高速なパターン更新の両方を実現するための第3のアプローチとして、FPGAの部分再構成機能を利用した新たな手法を提案した。提案手法は、正規表現の異なる部分クラスを扱う部分回路を複数用意しておき、与えられた正規表現パターンに適したコンパクトな回路構成をこれらの部分回路の組み合わせにより自動生成する。生成された回路構成は、変更箇所のみが部分再構成される。

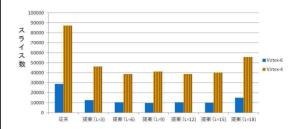

提案手法は、全てのパターンに対応可能な1つの回路を設計するパターン非依存型に比べ、コンパクトな回路を生成できる。またパターン依存型と違いパターンが更新された際に、時間のかかる回路の再設計を必要としないため、高速なパターンの更新が可能である。実験結果より、提案手法は既存のパターン非依存型手法と比べ、パターン更新時間をほとんど増加させることなく、回路面積を64%削減できた(図2)。

図2 提案手法と従来手法の回路面積

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

#### 〔雑誌論文〕(計2件)

若葉陽一,<u>若林真一</u>,<u>稲木雅人</u>,<u>永山忍</u>, シストリックアルゴリズムとNFAに基づくパ ターン非依存正規表現マッチングハードウェア,電子情報通信学会論文誌 D,査読有, Vol.J96-D, No.10, pp.2139-2149, 2013.

Yoichi Wakaba, <u>Shin'ichi Wakabayashi</u>, <u>Shinobu Nagayama</u>, <u>Masato Inagi</u>, An Area Efficient Regular Expression Matching Engine Using Partial Reconfiguration for Quick Pattern Updating, IPSJ Transactions on System LSI Design Methodology, 查読有, Vol.13, 2014 (印刷中).

## [学会発表](計9件)

Yoichi Wakaba, An Efficient Hardware Matching Engine for Regular Expression with Nested Kleene Operators, 21st International Conference on Field Programmable Logic and Applications, 2011年9月5日, Porto Platanias (Chania, Greece).

永山忍, ネットワーク侵入検知のためのパターン非依存NFA とシストリックアルゴリズムを組み合わせた正規表現マッチング, 第10回情報科学技術フォーラム, 2011年9月9日, 函館大学(函館市).

若葉陽一, パターン非依存正規表現マッ

チングエンジンに対する先読み演算の実現,電子情報通信学会VLSI設計技術研究会,2012年3月7日,ビーコンプラザ(別府市).

Yoichi Wakaba, A Matching Method for Look-ahead Assertion on Pattern Independent Regular Expression Matching Engine, 17th Workshop on Synthesis And System Integration of Mixed Information technologies, 2012年3月9日, ビーコンプラザ(別府市).

Yoichi Wakaba, A Practical FPGA

Implementation of Regular Expression

Matching with Look-ahead Assertion, 2012

Int. Conf. on Engineering of

Reconfigurable Systems and Algorithms

(ERSA2012), 2012年7月16日, Monte Carlo

Hotel (Las Vegas, USA).

三浦智香子,動的部分再構成可能FPGAを 用いた最大クリーク問題のハードウェア解法, IEEE広島支部学生シンポジウム,2012年11月 17日,岡山県立大学(総社市).

三浦智香子,大規模グラフの最大クリーク問題に対する部分再構成可能FPGAを用いたハードウェア解法,電子情報通信学会リコンフィギャラブル研究会,2012年11月26日,九州大学(福岡市).

Yoichi Wakaba, A Flexible and Compact Regular Expression Matching Engine Using Partial Reconfiguration for FPGA, EUROMICRO Conference on Digital System Design, 2013年9月4日, Hotel Santemar (Santander, Spain).

若葉陽一,高速なパターン更新のための FPGAの部分再構成を利用したコンパクトな正 規表現マッチングハードウェア,第26回回路 とシステムワークショップ,2013年7月29日,淡路夢舞台国際会議場(淡路市).

### 6. 研究組織

## (1)研究代表者

若林 真一(WAKABAYASHI, Shin'ichi) 広島市立大学・大学院情報科学研究科・教 授

研究者番号:50210860

## (2)連携研究者

永山 忍 (NAGAYAMA, Shinobu) 広島市立大学・大学院情報科学研究科・准 教授

研究者番号: 1 0 4 0 5 4 9 1 稲木 雅人(INAGI, Masato) 広島市立大学・大学院情報科学研究科・助教

研究者番号:50468302