# 科学研究費助成事業 研究成果報告書

平成 26 年 6月11日現在

機関番号: 3 4 3 1 5 研究種目: 基盤研究(C) 研究期間: 2011 ~ 2013

課題番号: 23500070

研究課題名(和文)動的再構成による自律制御システムのための開発プラットフォーム

研究課題名(英文)A developer's platform for autonomous control system utilizing dynamic reconfiguration technology

#### 研究代表者

泉 知論(Izumi, Tomonori)

立命館大学・理工学部・准教授

研究者番号:30303887

交付決定額(研究期間全体):(直接経費) 2,100,000円、(間接経費) 630,000円

研究成果の概要(和文):動的再構成を活用した自律制御システムのための開発プラットフォームについて、次の要素項目の研究開発を行った。 試作環境の実例として、動的再構成可能なFPGAとカメラを搭載したロボットカーを製作した。 開発プラットフォームとして、ソフトコアプロセッサと動的再構成スロットからなるシステムアーキテクチャを提案した。 当該プラットフォーム向けの基本モジュールとして、制御用プロセッサ、アクセラレータ間通信モジュール、動的再構成制御モジュール、また、画像処理向けのラインバッファライブラリなどを開発した。 高位合成技術を活用し、認識・自律制御のアルゴリズムのハードウェアアクセラレータを開発した。

研究成果の概要(英文): A designer's platform for autonomous control system is proposed. A robot car system is implemented so as to accept various trial designs aiming for recognition and autonomous control utilizing the feature of dynamic reconfigration. A system architecture is proposed consisting of a softcore processor and dynaically reconfigurable accelerator slots. For prototyping, basic units such as a control processor, network node, reconfiguration controller, and libraries for image filters are developed. Discussions to hardware design of algorithms for image recognition utilizing high-level synthesis technology are presented.

研究分野: 総合領域

科研費の分科・細目: 情報学・計算機システム・ネットワーク

キーワード: リコンフィギャラブルシステム 動的再構成 高位合成 組込みシステム 画像認識

#### 1. 研究開始当初の背景

災害・事故・火災現場、宇宙・深海・地下、 原子力施設、など、人間が踏み込むことが困 難な環境下での作業には、自ら認識・判断し 制御する機器の実現が期待される。機械的観 点からは、人間の遠隔操作による救助ロボット、深海作業船、宇宙機器などが実用化され ており、既に一定の技術レベルに達している と言えるだろう。自律制御という点では、惑 星/小惑星/衛星探査車などでは実現しれ ており、一般への普及にはまだ道のりは遠い。

自律制御の論理的基盤となるのは、認識と 自律制御のアルゴリズムである。古典的なア ルゴリズムとして、パタンマッチングによる 画像認識、比例項・積分項・微分項による制 御 (Proportional, Integral, Derivative Control)などが挙げられる。アルゴリズムが 比較的単純であり、それほど性能が高くない 組込みプロセッサによるソフトウェア処理 でも実現可能な半面、認識・制御の性能は限 られる。近年の急激な計算機の高性能化を追 い風として、AdaBoost による認識アルゴリ ズム、Particle Filter による追従制御、 Neural Network による学習と制御など、数 を頼みにした確率統計的な手法が提案され てきた。これらの手法はアルゴリズムレベル では好結果が得られているものの、膨大な計 算を要し、単純な実装では機器の大型化、電 池性能不足、発熱の増大といった問題を招く。

高負荷計算に対する実装上の常套手段として、処理のハードウェア化が挙げられる。特に、これら確率統計的な手法では、処理単位相互の独立性が高く、並列動作による高効率な高速化が期待される。(ただし全体を集約する処理も存在し、工夫を要する。)一方で、専用ハードウェア化は、開発にかかる時間と経費が大きいため少量生産品への適用は難しく、さらに機能が固定であるため環境ごとの変更、状況に応じた作業時の変更ができない。これは、現在から近い将来にかけての自律制御機器の需要や使われ方に適する方法とは言い難い。

ハードウェアの性能とソフトウェアの柔軟性を併せ持つデバイスとして再構成可能ハードウェアの利用が考えられる。特に、近年(2008年頃~)のデバイスは、回路の容量、速度、消費電力が大幅に改善され、実製品での利用も進んでいる。また、回路の動作中に回路の一部を書き換えることが可能な技術利用可能となっている(Xilinx 社 Virtexシリーズの動的部分再構成など)。この技術により、動作中に状況に応じてその機能や性能を変えるような自律制御機器の実現が期待される。

動的再構成技術はデバイスとして発表されて10年ほどになるが、これまで研究のトピックとしては注目を集めつつも、実用には至っていない。その大きな要因は、設計支援

技術にある。動的再構成可能デバイスが発表された当初は、デバイスの詳細アーキテクチャを熟知した設計者が再構成にかかる細部を人手で設計することでその機能を活用していた。それでは一般に普及すべくもなく、"おもしろい"動的再構成アーキテクチャを携えて起業したベンチャ企業の多くが、実機に(ほとんど)搭載されることなく消えていった。

一方で、再構成可能デバイスの大手企業ではデバイスとしては1990年代後半から動的部分再構成に対応していたものの、その詳細は一般には非公開とし、一部の大学や研究機関にのみ公開し設計支援ツールを提供していた。2000年前後には詳細配線まで人手で設計していたものが、2002年頃からはモジュール化設計に対応するようになり、2006年頃からはグラフィカルなユーザ・インターフェースが利用できるようになり、通常の設計支援ツールとは別ライセンスではあるが、一般に公開されることとなった。設計支援ツールの熟成に10年以上の歳月を要した(かけた)ことになる。

最新版の設計支援ツールでは、動的部分再 構成を行う領域を指定し、動的部分再構成す る回路群を指定し、全体(部分再構成を行わ ない)部分と動的部分再構成するそれぞれの 部分を個別にコンパイルすることで、動的再 構成回路を設計できる。再構成の制御ユニッ トも組込み部品としてライブラリに登録さ れている。これにより、レジスタ転送レベル と呼ばれるディジタル回路設計の基本的な 記述法で論理設計を行い、領域指定等一部物 理的な指定を行うのみで、詳細アーキテクチ ャを考慮した物理レベル設計を行うことな く、設計することが可能となった。しかし、 設計者の立場からすると、詳細物理レベル設 計からは解法されたとはいえ、動的部分再構 成の論理的振る舞いやタイミングを詳細に 設計せねばならないことには変わりはなく、 ディジタル回路設計に熟練者し、かつ、適応 的アルゴリズムを深く理解したものでなけ れば活用は難しいであろう。広く一般に普及 させるにはさらに設計を容易化する必要が ある。

開発環境についてソフトウェアの場合と 対比してみると、詳細物理設計まで人手で化 うことがハンドアセンブルに、モジュロロアセ 設計などが可能となったことがマクロアセ ンブラに、そして、記述から論理合成ツパセ に任せて設計可能となったことがの機能であるう。一方で、その機に相当するであろう。一方で、そのな使いない。基本的な部品群ピコンピ は提供されていない。基本的な部品群ピムコンは提供されたコンピーティング・システムがあるのは、 整備されてない状態に相当するであろう。こ のような状況で目下求められるのは、抽象化 された運用モデルと基本的な部品群であり、 実アプリケーションの研究開発の試行と得られた知見のフィードバックによる進化の スパイラルを進めていかねばならない。

#### 2. 研究の目的

本課題では、自律制御機器、認識・制御アルゴリズム、ハードウェアの動的再構成を柱として、アルゴリズムの応用、ハードウェア・アルゴリズム、機器構成、そして実装について研究開発を進める。

本課題の研究開発目的は機器の研究開発のためのプラットフォームの構築である。対象アプリケーション領域は、画像認識と自律制御を行う機器であり、それは環境・状況で実現する。実装上の制約として、自律動作、実現する。実装上の制約として、自律動作、実明間動作、小型、電池駆動を掲げる。プラマブル・ハードウェアの動的再構成のよりでは、I. アルゴリズムのハードウェア化を支援が、I. 動的部分再構成の運用モデル、I. 力チンオームとしてのシステム・アクチャ、IV. 基本ライブラリ群の開発が鍵となる。

その中で、本課題では動的再構成を利用した(1)画像認識・自律制御システムの試作機の実装、(2)開発プラットフォームとしてのシステム・アーキテクチャの提案、(3)当該プラットフォーム向けの基本モジュールの開発と例示、(4)認識・自律制御のハードウェアアクセラレータの開発を目標とする。

本課題の特色は、小型・低消費エネルギーな画像認識・自律制御の実時間処理を狙いとしたものであり、動的再構成技術による環境・状況への適応、運用モデル、設計支援ツール、ライブラリなどを含めた実装技術にした点にある。自律制御機器を必要としているさまざまな分野において、高度な機をの研究開発を容易化することにより、普及を促進し、より安全、安心、快適、便利な社会の実現に貢献することが期待される。

#### 3. 研究の方法

前述の4つの項目について、研究開発を進めた。

(1) 画像認識・自律制御システムの試作機 の実装

提案プラットフォームの応用展開の実例として動的部分再構成可能なデバイスを搭載した自律移動ロボットカーの試作機を製作する。準備段階で製作していた初号機に対して、次のような改良を施した。

- アルミフレームの設計・製作

- 電源モジュールの再設計・製作

- モーター駆動回路の再設計・政策

● 確認用モニタの制御回路の設計と搭載

(2) 開発プラットフォームとしてのシステム・アーキテクチャの提案

認識・自律制御システムを実現する際、処理の流れを体系化し、処理実体に割り付けていく。その共通化された受け皿となる、システム・アーキテクチャを提案する。本課題では、次の2点について研究開発を進めた。

- プロセッサとアクセラレータの基本構成の策定

- ▼クセラレータ間接続網の研究開発

- (3) 当該プラットフォーム向けの基本モジュールの開発と例示

以下の、プラットフォームの基幹をなすプロセッサや通信網、また画像認識のための基本的なモジュールについて、研究開発を進めた。

- 制御用ソフトコアプロセッサ

- ▼クセラレータ間通信網のノードとインターフェース

- 動的再構成制御モジュール

- 画像フィルタ開発支援ライブラリとテンプレート

- (4) 認識・自律制御のハードウェアアクセラレータの開発

認識・自律制御の実現に向けて、画像認識、 機械学習、人工知能に関する要素アルゴリズムのハードウェア化の検討を進めた。ここで は次のアルゴリズムを取り上げ、研究開発を 進めた。

- 画像認識のための特徴量検出・記述アルゴリズム

- 対象物の追跡アルゴリズム

- 人物の検出・認識アルゴリズム

- 4. 研究成果

- (1) 画像認識・自律制御システムの試作機の実装

改良した自律移動ロボットカーの試作機を 開発した(図1)。動的再構成可能な FPGA チップを搭載したボード、カメラ、モーターお よび制御回路、モニタを搭載している。 FPGA チップを再構成することで様々なシステム を構築することができ、これまで色を認識し てボールを追いかけるなど、基本的な動作を 確認している。

図1:改良した自律移動ロボットカー

(2) 開発プラットフォームとしてのシステム・アーキテクチャの提案

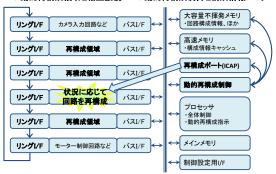

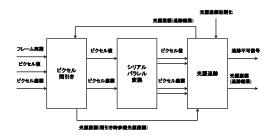

制 御 用 ソ フ ト コ ア プ ロ セ ッ サ COMET-II(改)と動的再構成スロットからなるシステムアーキテクチャ(図 2)を規定した。また、ハードウェアアクセラレータ間の相互接続網としてトークンリングを採用し、動的再構成スロットの基本構成(図 3)を規定した。(学会発表④⑥)

a.動的再構成領域と相互接続 b.動的再構成制御と構成情報メモリ

図2:提案システム・アーキテクチャ

図3:再構成スロットの基本構成

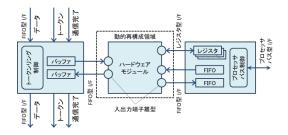

(3) 当該プラットフォーム向けの基本モジュールの開発と例示

制御用ソフトコアプロセッサ:公的試験で採用・公開されている COMET II プロセッサを制御用ソフトコアプロセッサとして設計し(図4)、割込機能などの拡張を行った。各FPGAベンダ専用のプロセッサに対して、動作周波数は半分程度であるが、規模も半分程度に小さく、ベンダ非依存に実装できる。(学会発表④)

図4:設計した COMET II (改) のブロック図

アクセラレータ間通信網のノードとインターフェース、動的再構成制御モジュール:アクセラレータ間のトークリング通信網のノードであり、かつ動的再構成スロットとのインターフェースとなる通信モジュール(図2右上から3、4番目)を設計した。Xilinx社FPGA XC5VLX50 に実装し、回路規模は117Slices,最大動作周波数は339MHzであった。また、同的再構成制御モジュール(図3左)を設計し、規模は34Slicesで最大動作周波数は853MHzであった。実際にFPGAボードで動作を確認し、これらは十分に小さく、高速である。(学会発表⑥)

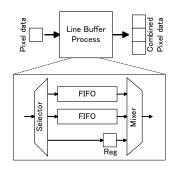

高位合成向けラインバッファライブラリと 畳み込みフィルタテンプレート:画像処理の 基本フィルタである畳み込みフィルタにつ いて、高速かつ高効率に処理するためにライ ンバッファ、ウィンドウバッファを用いたパ イプライン構成をとることが多い。その基本 部品であるラインバッファ、ウィンドウバッ ファをライブラリとして設計(図5)し、ま た、様々なタイプの畳み込みフィルタ、ある いは近傍から算出するフィルタを開発する ためのテンプレートを作成した。旧来のハー ドウェア記述言語による設計に対して、最大 動作周波数では 30%劣るものの、回路規模は 同等で、数行の変更で様々なフィルタに改造 することができ、シミュレーションは21倍 高速である。(学会発表⑤)

図5:ラインバッファの構成

(4) 認識・自律制御のハードウェアアクセラレータの開発

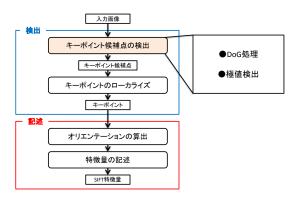

特徴量検出・記述アルゴリズムのハードウェア向けアーキテクチャの提案:SIFT は画像認識等に用いられる特徴量検出・記述アルゴリ

ズムのひとつであり(図6)、拡大縮小、回転、光源変化に強いとされている。SIFT アルゴリズムの中で、計算負荷の高いDoG(Difference of Gausian)画像の生成と極地検出(図6右上)について、高位合成によるハードウェア化を検討し、アーキテクチャを提案した。SIFT は、組込みシステムで使われる比較的廉価な FPGA でも、監視カメラなどで一般的な VGA サイズに対して、100MHz程度の動作周波数で10fps程度の性能を見込む。(学会論文③)

図6:SIFTアルゴリズムの概要

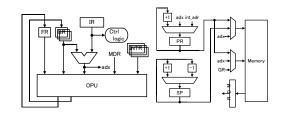

動画像中の光点追跡アルゴリズムのハードウェア化:高速で移動する物体を追跡するための高速カメラ向けの対象物追跡ハードウェアを設計した。システムを、大量だが一様なフロントエンドの処理を行うハードウェアと、頻度は低いが緻密な推定を行うバックエンドのソフトウェアに分割し、効率の良いシステムを構成する。ハードウェアにおいても、近傍を切り出し、また処理を並列化、パイプライン化することにより、さらなる高速化をはかった(図7)。Xilinx 社 FPGA XC5VLX30を対象に設計し、100Mpixes/sec 以上の高速画像に対して最大16個の光点を350nsのレイテンシで追従することができる。(学会発表②)

図7:光点追跡ハードウェアのブロック図

表情認識アルゴリズムの検討:より高度な認識に向けて、人物の表情を認識するアルゴリズムの基礎検討を行った。 AAM (Active Appearance Model) と局所的な Gabor

DIrectional Pattern に基づいた表情認識を 行う手法を提案した。ソフトウェアとして実 装し、94%の認識率を達成した。(雑誌論文①)

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## 〔雑誌論文〕(計 1件)

①. 著者名: A.Higashi, Y.Fukumizu, <u>T.Izumi</u>, H.Yamauchi、論文標題: Expression Recognition Using LGDPHS Based Facial Key Parts、雑誌名:画像 電子学会誌、査読:有、巻:41、号:5、 発行年:2012、ページ:496-505

## 〔学会発表〕(計 8件)

- ①. 発表者名:河合遼,城圭太,泉知論,白木善史,鎌本優、発表標題:高速カメラによる広帯域光無線通信のための光源追跡ハードウェアの検討、学会等名:情報処理学会第76回全国大会1A-6、発表年月日:2014年3月11日、発表場所:東京電機大学(東京都)

- ②. 発表者名: N. Murata, Y. Fukumizu, T. Izumi, H. Yamauchi、発表標題: Human detection using histograms oriented gradients with background subtraction based mixture-of-Gaussians human behavior recognition、学会等名: 2014 International Workshop Nonlinear Circuits, Communications and Signal Processing、発表年月日: 2014 年 3 月 3 日、発表場所: Honolulu (U.S.)

- ③. 発表者名:荒川尚久,孟林,泉知論、発表標題:高位合成による FPGA 実装向け SIFT アルゴリズムの構成法の基礎検討、学会等名:電子情報通信学会 技術研究報告 RECONF2013-59、発表年月日:2014年1月28日、発表場所:慶應義塾大学(神奈川県)

- ④. 発表者名:木本慧, 泉知論、発表標題: 公的検定用プロセッサ COMET II の組込 み向けソフトコアとしての設計と評価、 学会等名:電子情報通信学会 技術研究 報告 VLD2012-156、発表年月日:2013 年3月5日、発表場所:沖縄県青年会館 (沖縄県)

- ⑤. 発表者名:荒川尚久,<u>泉知論</u>、発表標題:画像処理用ラインバッファの高位合成系向けライブラリ化設計、学会等名:電子情報通信学会 技術研究報告RECONF2012-83, VLD2012-129,CPSY2012-78、発表年月日:2013年1月17日、発表場所:慶應義塾大学(神奈川県)

⑥. 発表者名:水野友和,木田義彰,上出亮, 寺田慎,徳田充祥,<u>泉知論</u>、発表標題: 組込みシステムにおける動的部分再構成の活用のためのモジュール相互接続網と再構成制御部の一設計、学会等名: 電子情報通信学会 技術研究報告 RECONF2012-12、発表年月日:2012年5月29日、発表場所:沖縄県男女共同参画センター(沖縄県)

[図書] (計 0件)

[産業財産権]

- ○出願状況(計 0件)

- ○取得状況(計 0件)

[その他]

ホームページ等

http://www.ritsumei.ac.jp/se/re/izumilab/research/KakenC23500070.html

- 6. 研究組織

- (1)研究代表者

泉 知論 (IZUMI TOMONORI)

立命館大学・理工学部・准教授

研究者番号:30303887