# 科学研究費助成事業 研究成果報告書

平成 26 年 6 月 30 日現在

機関番号: 5 1 6 0 1 研究種目: 基盤研究(C) 研究期間: 2011 ~ 2013

課題番号: 23500072

研究課題名(和文)メムリスタを含む回路の動作解析とメムリスタの応用に関する研究

研究課題名 (英文) Research on the analysis of the behaviour of circuits including memristors and its a

pplications

#### 研究代表者

大槻 正伸(OHTSUKI, Masanobu)

福島工業高等専門学校・その他部局等・教授

研究者番号:20203846

交付決定額(研究期間全体):(直接経費) 1,500,000円、(間接経費) 450,000円

研究成果の概要(和文):本研究では、メムリスタとよばれる、2008年に新しく発見された電気回路素子を用いた応用について調べ、(1)不揮発性2値メモリシステム、(2)不揮発性多値メモリシステム、(3)従来よりも外部入力制御信号数が非常に少なくてすむ可変論理回路の3つのメムリスタを用いたデバイス構成法を提案した。この方法で構成されたLSIシステムは、現在のコンピュータシステムにそのまま組み込めるものである。

研究成果の概要(英文): In this study we researched the applications of the Memristor which is the new ele ctrical circuit element found in 2008. We have proposed the constitution methods for constructing the fol lowing three new devices, (1)a nonvolatile 2-values memory system, (2) a nonvolatile multi-valued memory system, (3) a variable logic circuit with less input control signals than before. In each case the LSI system made with the proposed ways can be directly embedded into the present computer systems.

研究分野: 総合領域

科研費の分科・細目: 情報学、計算機システム・ネットワーク

キーワード: メムリスタ 不揮発性メモリ 多値メモリ 可変論理回路

#### 1. 研究開始当初の背景

メムリスタは「電圧を印加し、電流が流れると、抵抗が変化する。そして電圧印加を中止すると、その時点での抵抗値を保持する」という性質をもつ電気回路素子である。これは 1971 年に Leon Chua によって存在が予言されたが、その存在がその後確認できなかったものである。しかし 2008 年に HP(ヒューレットパッカード) 社の 研究者 Stanley Williams らが、 $TiO_2$  (二酸化チタン)を Pt (プラチナ)でサンドイッチする構造の素子として、その存在を示した。

発見後、新しく存在が確認されたメムリスタを用いて様々な応用の研究がされ始まった。この時点では、様々なデバイスに応用できるであろうということが多く予想されてはいたが、ほとんどが具体的な設計方法の提案、具体的な設計図なしのまま提案されているという状況であった。

#### 2. 研究の目的

メムリスタを用いた具体的な応用について研究し、提案していくことにより、メムリスタの応用可能性を明らかにすることを目的とした。

そして、今回はできる限り具体的に、実際に構成法まで明らかにして、メムリスタを用いたデバイスを提案することとした。

## 3. 研究の方法

メムリスタそのものはナノメートルスケールのオーダーの素子であり、現実に入手することが困難である。

したがって、今回の研究では、

- (1) メムリスタを用いたデバイスを机上で設計すること。

- (2) 机上で設計するための種々の計算(電 圧印加時間と電圧の関係等)をコンピュータ を用いて行い、設計の正確性を確保すること

- (3)作成したデバイスの動作(部品であるメムリスタそのものの電圧―電流特性、メムリスタを含むデバイス全体の動作等)をシミュレーション等を通して確認すること、の3つの方法によって研究を進めた。

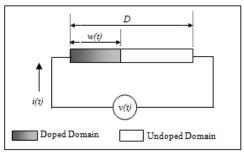

特に今回は、メムリスタのうち Fig.1 のように、低抵抗領域( $Doped\ Domain$ )と高抵抗領域( $Undoped\ Domai$ )が連結され、低抵抗領域の長さ w(t)が下記微分方程式により時間変化するモデルを用いることとした。

Fig1 The coupled variable-resistor model

$$\begin{cases} v(t) = \left\{ \frac{w(t)}{D} R_{on} + \frac{D - w(t)}{D} R_{off} \right\} i(t) \\ \frac{dw(t)}{dt} = \mu_{V} \frac{R_{on}}{D} i(t) \end{cases}$$

#### 4. 研究成果

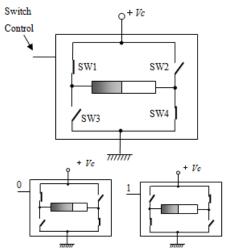

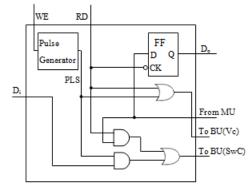

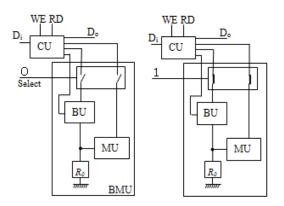

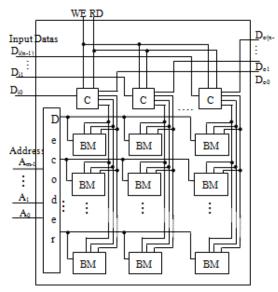

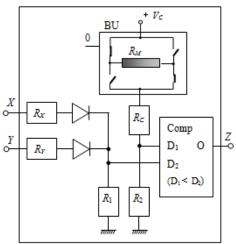

(1) メムリスタを用いて、その全抵抗値が最大の状態を1、最小抵抗の状態を0に対応させることにより、2値の不揮発性メモリが構成できることを示し、実際にその具体的構成法を明らかにした。ここではFig.1のメムリスタを用いて、Fig.2~Fig.6のように階層的に不揮発性2値メモリが構成できることが明らかになった。

Fig.2 The Basic Unitl (BU)

Fig.3 Construction of CU

Fig.4 Construction of MU

Fig.5 The Control Unit (CU) and the Basic Memory Unit (BMU)

Fig.6 Construction of a Memory System (C:CU, BM:BMU)

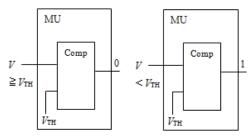

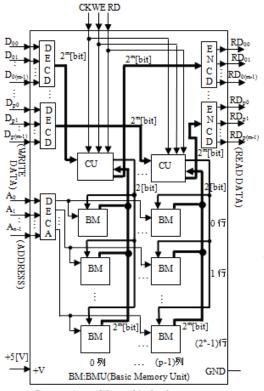

(2) 印加電圧および印加時間を一定にしたときの抵抗値の変化により、その抵抗値をいくつかに分割し、その抵抗値の状態と0,1,2,3…等を対応させることにより、多値メモリが構成できることを示し、その具体的構成法を明らかにした。

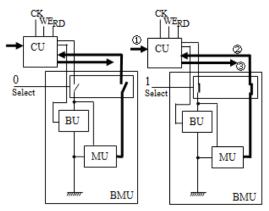

ここでは、(1)と同様の基本デバイスをもとに、階層的にFig.7,Fig.8のように不揮発性多値メモリの構成法が具体的に明らかになった。

O Write Data O Read Data from BU O Read Data from CU

The Control Unit (CU) and

Fig.7 the Basic Memory Unit (BMU) (-: Moits Data)

Fig.8 Construction of the multivalued memory system

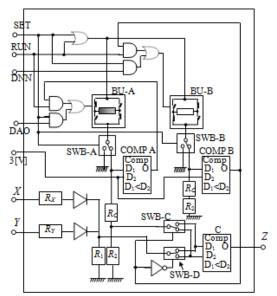

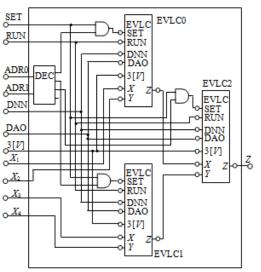

(3)「メムリスタを用いた可変論理回路」の構成法を明らかにした。これは一回製作したハードウェアは変えることなく、それに含まれるメムリスタの抵抗値の状態により、AND回路になるか、OR回路になるかが制御できる回路である。従来の可変論理回路は、外部からの制御信号が、論理素子(AND, OR等)数が多くなるとそれにつれて多くなるのが弱点であったが、メムリスタを用いた可変論理回路では、一定数の外部制御信号で実現可能であることが示された(Fig. 9~Fig. 11)。

Fig. 9 The Basic Variable Logic Circuit (BVLC)

Fig. 10 The Extended Variable Logic Circuit(EVLC)

(2-Inputs Variable Logic Circuit System)

Fig.11 The Multi-Inputs Variable Logic Circuit System

(MVLC System)

これらの3つの応用デバイスは、基本的に5[V]で動作する現在のコンピュータに、そのまま組み込める形式となっている。例えば、上記(1)の2値メモリであれば、現在のコンピュータのメモリと置き換えができる形式の構成法となっている。

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者には下線)

〔雑誌論文〕(計 3件)

①大槻 正伸、一ノ瀬 智浩、西内 拓也

メムリスタを用いた不揮発性メモリシステムの構成、福島高専研究紀要 第52号、査読有、PP19-24

②大槻 正伸、一ノ瀬 智浩、西内 拓也 メムリスタを用いた不揮発性多値メモリシ ステムの構成、福島高専研究紀要 第53号、 査読有、PP1-6

③大槻 正伸、メムリスタを用いた可変論理 回路の構成、福島高専研究紀要 第54号、査 読有、PP37-42、

[学会発表](計 件)

〔図書〕(計 件)

[産業財産権]

○出願状況(計 件)

名称: 発明者: 権利者: 種類: 番号: 田願年月日: 国内外の別:

○取得状況(計 件)

名称: 発明者: 権類: 種類: 番号: 取得年月日: 国内外の別: 〔その他〕 ホームページ等 6. 研究組織 (1)研究代表者

大槻 正伸 (OHTSUKI Masanobu) 福島工業高等専門学校 電気工学科教授

研究者番号: 20203846

(2)研究分担者

( )

研究者番号:

(3)連携研究者

( )

研究者番号: