# 科学研究費助成事業 (科学研究費補助金) 研究成果報告書

平成25年5月20日現在

機関番号:32689

研究種目:研究活動スタート支援

研究期間: 2011 ~ 2012 課題番号: 23860052

研究課題名(和文) FTVとSHV向けの超高速視差/動き予測アーキテクチャの研究

研究課題名(英文) Ultra-high-speed Disparity/motion estimation architecture for FTV and SHV

研究代表者

周 大江 (ZHOU DAJIANG) 早稲田大学・理工学術院・助教

研究者番号:10607336

研究成果の概要(和文): HDTVとステレオ3DTVの実用化が可能になったことで、FTV(自由視点テレビ)とSHV(スーパーハイビジョン)の二つの新しいビデオアプリケーションは、現在、次世代ビデオ応用の研究対象となってきている。これらの新しいアプリケーションを実用化させるために、差分/動き予測(DME)をキーコンポーネントとした超高スループットのビデオエンコーダVLSIの実現が極めて重要である。FTVとSHVの要件を満たすためには、この研究は、従来最先端の設計より10倍も早い、2Gピクセル/秒のスループットを持つDMEアーキテクチャを開発した。

研究成果の概要(英文): FTV (Free-viewpoint Television) and SHV (Super Hi-Vision) are two promising research targets for the next-generation video services. To achieve these targets, a crucial technology is ultra-high-throughput video encoder VLSI, with disparity/motion estimation (DME) as its core component.

To meet the requirement of FTV/SHV, we developed a 2Gpixels/s DME architecture design, which is near 10 times faster than the state-of-the-art works.

#### 交付決定額

(金額単位:円)

|       | 直接経費      | 間接経費    | 合 計       |

|-------|-----------|---------|-----------|

| 23 年度 | 1,300,000 | 390,000 | 1,690,000 |

| 24 年度 | 1,200,000 | 360,000 | 1,560,000 |

| 年度    |           |         |           |

| 年度    |           |         |           |

| 年度    |           |         |           |

| 総計    | 2,500,000 | 750,000 | 3,250,000 |

研究分野:システム工学 科研費の分科・細目:

キーワード: SHV、スーパーハイビジョン、FTV、自由視点テレビ、動き予測

### 1. 研究開始当初の背景

最近の10年間で画像処理は2つの急速な変化を遂げている。1つは画素数の増大である。1280x720であったものが、フルハイビジョンと呼ばれる1080p(19

$20 \times 1080$ ) へ増加し、現在は $4 \times (3840 \times 2160)$  が実用化しつつあるだけではなく、スーパーハイビジョンと呼ばれる  $8 \times (7680 \times 4320)$  への挑戦がなされている。もう1つは従来の $2 \times \pi$ ではなく、多数のビュー(視点)から画像が見られる3

Dあるいはフリービューと呼ばれる自由な 視点画像を扱うようになったことである。これらの処理のために画像データが大規模化 し演算も膨大となり、新しい圧縮手法の開発 が強く望まれている。

これまで1994年に開発されたMPEG2により約1/50までデータの圧縮が実現し、ハイビジョン放送が可能となり現在のTV放送で実用化され、2004年に開発されたH.264では約1/100の圧縮が実現し、現在のワンセグ放送や、ビデオカメラやDVDにおける記憶方法として採用され実用化が行われているなど、画像圧縮技術は、昨今の情報社会において欠かせない技術の一つと言っても過言ではない。

#### 2. 研究の目的

フルハイビジョンとステレオ 3 D T V の実用化が可能になったことで、F T V (自由視点テレビ)と S H V (スーパーハイビジョン)の二つの新しいビデオアプリケーションは、現在、次世代ビデオ応用の研究対象となっョンを実用化させるために、差分/動きを超している。これらの新しいアプリケーションを実用化させるために、差分/動き超点のからでデオエンコーダ V L S I の所でが極めて重要である。 F T V と S H V の 要件を満たすためには、この研究は、従来して砂のスループット(7680 x 4320/60 f p s)を持つDMEアーキテクチャを目指している。

#### 3. 研究の方法

超高速視差/動き予測(DME)エンジンを開発することであり、以下の主要な2つの技術課題を解決することを目指す。

(1)メモリバンド幅を削減した予測アーキテクチャの開発。

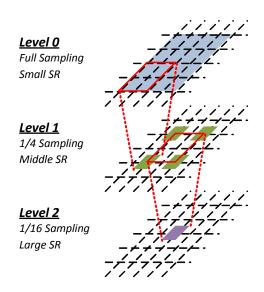

8 Kのような超大規模画像データにおいては、DMEでの探索領域(SR)が非常に大規模となり、演算時間とメモリバンド幅のボトルネックとなる。本提案では階層的探索手法により、解決を図ることを考えている。階層的探索手法では、粗いピクセルから細かいピクセルレベルまでの階層的なサンプル画像を用意し、MEを段階的に実行することで、高速な処理が可能となる。具体的には

ア)各階層における参照サンプル画像のデータの依存性と異なる階層間のデータの依存性と異なる階層間のデータの依存性を考慮して、参照サンプル画像の最適化を図る。DRAMには最適化されたデータを格納することで、40%~60%のメモリバンド幅削減が可能と考えている。

イ) 演算量とメモリバンド幅を更に削減す

るために、各階層に演算の打ち切り(ターミネート)手法を導入する。小さな動きの画像や複雑な画像をもつフレームはレベル0の探索を、大きな動きのあるフレームは高位レベルの探索を行い、予測手法を導入することで、各階層での演算を早めに打ち切れることが可能である。

図1. 階層的サーチ手法

以上の方法の導入することで、双方向探索に必要なクロックは一つのマクロブロック当り、150クロックサイクルで処理可能であり、300MHzで、4K/が可能になると予測している。

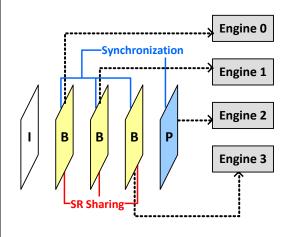

図2、フレームレベルの並列化

(2) フレーム並列化エンジンの開発

8 Kのような大規模画像データでは、1つのDMEエンジンで高スループットを達成することは難しく、複数のDMEエンジンを並列に動作させてスループットを上げることが必要となる。従来はスライスレベルでの並列化が行われてきたが、本提案ではフレー

ムレベルの並列化を導入して高速化を図る予定である。各 ME エンジンは 1 フレームを処理する。フレーム間で探索領域の共有化を行うことにより、ME のメモリバンド幅を 5 0 %~ 7 0 %削減が可能である。

以上の2つ方式の導入と、GOP構造に対して、動的にMEエンジンを割り当てることも行うことで、300MHzで8K/60f psが達成できると予測している。

#### 4. 研究成果

H23年度では、我々は主にDMEアーキテ クチャに適用できるアルゴリズムの提案に 取り組んだ。データ解析サーバに、レファレ ンスソフトウェア(JMVC)に基づくソフ トウェアモデルを確立した。このソフトウェ アモデルの性能を評価するには、様々な拡張 マルチビューとモノスコピックのビデオシ ーケンスは使用された。我々は、ビデオデコ ーダのために提案した手法に対し、DME に 使用できるように調整をしてから、新しいビ デオエンコーダのために開発したアルゴリ ズム(インタレース予測範囲の割り当て方式、 水平スライディング動き予測中心方式、ひし 形検索ウィンドウなど)に、上記のモデルを 用いて評価した。これらの技術の効果的な部 分を統合し、最終的に総合フレームワークを 提案した。ソフトウェアモデルの評価より、 目標スループット(2Gピクセル/秒)が達成 できることを確認した。

H24年度では、我々は主にDMEエンジン の回路設計のに取り込んだ。前年度確立した ソフトウェアモデルを基にして、DMEエン ジン用の予測アルゴリズムを統合し、最終的 に総合フレームワークを決定した。総合フレ ームワークをもとに、ハードウェア設計の課 題(パイプライン処理、データ依存性)に取 り組み、最大のスループットを達成するアー キテクチャも決定した。また消費電力とDR AMバンド幅の削減に向けて、フレームデー タのオンライン再圧縮方式と複数の DME エ ンジン間で探索領域を再利用が可能なアー キテクチャを開発した。得られたアーキテク チャを基にして、HDLコードを記述し、R TLシミュレーションと検証を行った。DM Eエンジン機能のLSIプロトタイプの実 装にも取り込んだ。DMEエンジンの予測ア ルゴリズムとハードウェアアーキテクチャ について、得られた結果を取りまとめ、著名 な国際学会(VLSIシンポジウム)へ投稿、 採択された。

#### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

〔雑誌論文〕(計2件)

- [1] Gang He, <u>Dajiang Zhou</u>, Wei Fei, Zhixiang Chen, Jinjia Zhou, Satoshi Goto, "High-performance H.264/AVC intra prediction architecture for Ultra-HD video applications", IEEE Transactions on Very Large Scale Integration (VLSI) Systems (TVLSI), 2013.

- [2] Xuena Bao, <u>Dajiang Zhou</u>, Peilin Liu, Satoshi Goto, "An advanced hierarchical motion estimation scheme with lossless frame recompression and early level termination for beyond high definition video coding", IEEE Transactions on Multimedia (TMM), Vol. 14, No. 2, pp. 237-249, April, 2012.

#### 〔学会発表〕(計7件)

- [1] Jinjia Zhou, <u>Dajiang Zhou</u>, Gang He, and Satoshi Goto, "A 1.59Gpixel/s motion estimation processor with -211-to-211 search range for UHDTV video encoder",

- Symposium on VLSI Circuits (VLSI), Kyoto, Japan, June, 2013.

- [2] <u>Dajiang Zhou</u>, Gang He, Wei Fei, Zhixiang Chen, Jinjia Zhou, and Satoshi Goto, "A 24.5-53.6pJ/pixel 4320p 60fps H.264/AVC intra-frame video encoder chip in 65nm CMOS", Asia and South Pacific Design Automation Conference (ASP-DAC), Yokohama, Japan, January, 2013.

- [3] Jinjia Zhou, <u>Dajiang Zhou</u>, and Satoshi Goto, "Interlaced asymmetric search range assignment for bidirectional motion estimation", IEEE Int'l Conference on Image Processing (ICIP), Orlando, USA, pp. 1557-1560, September, 2012.

- [4] Gang He, <u>Dajiang Zhou</u>, Jinjia Zhou, and Satoshi Goto, "A 1991 Mpixels/s intra prediction architecture for Super Hi-Vision H.264/AVC encoder", European Signal Processing Conference (EUSIPCO), Bucharest, Romania, pp. 1054-1058, August, 2012.

- [5] Heming Sun, <u>Dajiang Zhou</u>, and Satoshi Goto, "A low-complexity HEVC intra prediction algorithm based on level and mode filtering", IEEE International Conference on Multimedia and Expo (ICME), Melbourne, Australia, pp. 1085-1090, July, 2012.

- [6] <u>Dajiang Zhou</u>, Gang He, Wei Fei, Zhixiang Chen, Jinjia Zhou, and Satoshi Goto, "A 4320p 60fps H.264/AVC intra-frame encoder chip with 1.41Gbins/s CABAC", Symposium on VLSI Circuits (VLSI), Honolulu, USA, pp. 154-155, June, 2012.

- [7] Zhenyan Guo, <u>Dajiang Zhou</u>, and Satoshi Goto, "An optimized MC interpolation

architecture for HEVC", IEEE Int'l Conference on Acoustics, Speech, and Signal Processing (ICASSP), Kyoto, Japan, pp. 1117-1120, March, 2012.

〔その他〕 ホームページ等 http://www.aoni.waseda.jp/zhou

## 6. 研究組織

## (1)研究代表者

周 大江 (ZHOU DAJANG)

早稲田大学・大学院情報生産システム研究

研究者番号:10607336