# 科学研究費助成事業 研究成果報告書

平成 27 年 5 月 17 日現在

機関番号: 13901 研究種目: 基盤研究(C) 研究期間: 2012~2014

課題番号: 24500058

研究課題名(和文)階層型組み込みメニーコア向けタスク配置手法の研究

研究課題名(英文)Task Mapping for Hierarchical Many-core Processors in Embedded Systems

研究代表者

枝廣 正人(EDAHIRO, MASATO)

名古屋大学・情報科学研究科・教授

研究者番号:50578854

交付決定額(研究期間全体):(直接経費) 4,000,000円

研究成果の概要(和文):階層型メニーコアアーキテクチャに対し、階層構造を考慮したタスク配置手法を提案した。 提案手法はLSI配置向けに提案された階層クラスタリング法をもとにしているが、タスクマッピング問題に適用するため、タスク間通信量や、アーキテクチャ内の配線の使用頻度の偏り等を考慮している。従来手法と比較した結果、通信コスト、アプリケーション完了時間を削減し、通信コストの最小化によってアプリケーション自体の実行時間が削減できるということを示した。

研究成果の概要(英文): In this research, we proposed a task mapping method that considers features of task graphs and performance characteristics of hierarchical many-core architectures. We proposed the "HCME" toward task mapping method for "CMesh" which is a type of hierarchical many-core architectures. We also proposed a merge technique required when there are more number of tasks than the number of cores.

We compared our proposed mapping method with existing algorithms. As a result of evaluation experiments, our proposed method reduced communication cost and application completion time.

研究分野: 組込みシステム

キーワード: 組込みシステム マルチコア メニーコア タスク配置

## 1.研究開始当初の背景

半導体微細化の進展により、一つの LSI 上に複数のプロセッサ・コアが搭載されたマルチコアや、グラフィックスのような特定用能 数百のプロセッサ・コアが搭載されたメニーコアが広く使われている。数位は、単体プロセッサの動作周で性的上による方法と比較して低消費電力で問題では、りている。しかしながら、実際にその性能を受するためには、ソフトウェアに含まともれている。といる、フトウェアに含まともいるのタスク(スレッド、プロセスなどもよばれる)をプロセッサ・コアに割り付けてい要がある。

現在発表されている汎用用途向けメニーコアはタイル型とよばれるアーキテクチャであるが、さらにプロセッサ・コアが増えた時には階層化し、階層型メニーコアになると考えられている。そのため、タスク配置は階層構造を考慮し、プロセッサ・コアに割り付けていく必要がある。

## 2. 研究の目的

我々は LSI 回路設計において、回路を LSI 上に小面積、高性能に配置するため、回路のグラフ構造を LSI 上に配置するためのアルゴリズムについて研究し、回路を階層化することにより効率の良い配置を行う「階層クラスタリング法」を提案した[1]。

タスクは、タスク間に依存関係を持つ場合が多く、タスクグラフとよばれるグラフ構造を持つ。本研究では、階層型メニーコアアーキテクチャの性能特性も考慮しつつ、階層クラスタリング法を階層型メニーコアおよびタスクグラフ向けに発展させ、階層型メニーコア上で効率よく並列実行できるようなタスク配置の実現を目的とした。

LSI 配置問題とタスク配置問題は、接続する要素を近くに配置するという意味で基本は同じである。しかしながらタスクには実行順序があり、大きく異なっている。

これらをふまえ、現状のアルゴリズムを発展させ、階層型組み込みメニーコア上のタスク配置向けの新しいアルゴリズムを考案することが本研究の目的である。

#### 3.研究の方法

# (1) アーキテクチャの持つ階層に合わせたタ スククラスタリング

最終的にタスクを階層型メニーコアに配置していくため、タスクのクラスタ化は全合していくため、タスクのクラスタ化整と会に出ることが望まれる。しかしながらランとが望まれる。しかしながらランとはアーキテクチャの持つ階層構造とも階合しない。そのため、ターゲットときる階層とはアーコアで効率よいて研究を進めたとうスタは階層的には2クラスタに関係的には2クラスタに関連を表したより、アーキテクチャ上で制整をで記した。ことにより、アーキテクチャ上で制整することにより、アーキテクチャ上で制整することもで配置する。

# (2) アーキテクチャ性能特性に則したタスク配置

タスク間 (クラスタ間) 通信は、実際のアーキテクチャ上での通信となるため、通信性能特性を考慮しながらタスク (クラスタ)を配置していく必要がある。具体的に言えば、通信が遅い場合にはタスク (クラスタ) 粒度を大きくし、通信オーバーへッドの割合を小さくする必要があり、通信が速い場合には手なるがまた、アーキテクチを関層に応じて通信性能は異なるため、そを略層に応じて通信性能は異なるクラスタを階層型メニーコアアーキテクチャに配置づいて研究を進めた。

## 4. 研究成果

- (1) 提案アルゴリズム

- 提案手法は三つの部分からなる。

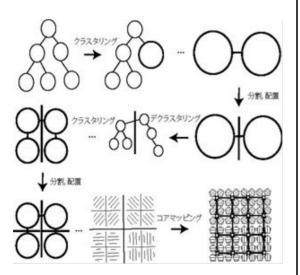

- a. クラスタリング:タスクグラフをクラス タ化し、階層構造を構成

- b. 分割:クラスタを均一に分割

- c. 配置:分割結果の位置関係を決定

既存手法では「分割」と「配置」によって 配置問題を解いているが、提案手法では前述 の階層クラスタリング法の特徴を反映し、ク ラスタリングステージを追加した。

#### a. クラスタリング

階層クラスタリング法では、構成要素を接続するエッジ数に関してクラスタリング法を分が行われていた。階層クラスタリング法をタスク配置手法に拡張するため、エッジ数では入り配置手法に拡張するため、エッジ数ではなりでを行うものとした。通信量の多いエッジを持つ2つのタスクを次々に結合していく。結合が進むたびにタスクの数は1つずつ減り、最終的には2つのクラスタとなる。クラスタリングを行う目的としては、分割において多リングを行う目的としては、分割においてあり、対している。通信が同一コアクラスタ内にマッピングは通信が同一コアクラスタ内にマッピングされやすい等の利点がある。

#### b. 分割

分割のステージではタスククラスタ内に分割線を挿入し、分割線を横切る通信を考慮してタスククラスタを分割する。この分割では、通信コストの削減を狙う他、プロセッサアーキテクチャを考慮し、全体的なコアクラスタ間の通信を減らし、通信の分散を狙う目的もある。

## c. 配置

配置のステージでは分割されたクラスタの位置関係を決定する。配置のステージで実現するのは通信コストの最小化と通信の分散の2点である。配置を決定する際にも分割時と同様のモデルを導入する。

### d. 全体のアルゴリズム

クラスタリング、分割、配置を繰り返し、 最終的なマッピングを決定する。アーキテク チャの形に応じて分割、配置のパラメタを調 整する事によって、様々なアーキテクチャに 対応できる。以下が提案手法のアルゴリズム である。

(クラスタリング) 1つのタスクにつき 一回結合できるものとして、通信の重み が大きいタスクを、結合できる箇所が存 在する限り、順に結合。

(クラスタリング) 1 つのクラスタを 1 つのタスクとみなす。 、 を繰り返し、 最終的に 2 つのクラスタにする。

(分割)内包タスク数が同数になるよう クラスタを分割。

(配置)分割後のクラスタを配置。 配置されたクラスタをデクラスタリング し、タスクグラフとする。

分割されたそれぞれのクラスタにおいて 1 クラスタずつ ~ を繰り返す。十分 に分割され、配置が完了したら終了。

アルゴリズムは図1のように進行する。図 の簡単化のため、タスクの数を6としている。

図1.アルゴリズム全体のイメージ

## (2) 実験

#### 実験手法

既存手法としては、貪欲法、グループ化法の大きく二つに分けられるが、これらの方法および元の階層クラスタリング法[1]と提案手法の比較を行う。貪欲法からは NN Embed法[2]、Topo-LB 法[3]を選択し、グループ化法からは Cluster-Based ILP法[4]を選んだ。ここで、これら 3 つの既存手法は階層を持つアーキテクチャを想定していないため、アーキテクチャ情報においてクラスタ内のコア間距離を 0 と設定することにより、階層に対応したアルゴリズムに拡張した。

タスクグラフはグラフ生成ツールを用いたものとセンサレスモータ制御から生成されたタスクモデルを用いた。グラフ作成ツールは TGFF[5]を用い、16 タスクから 1024 タスクのタスクグラフをランダムに各 10 種類作成した。プロセッサアーキテクチャとしては集中メッシュトポロジを用いた。各マッピング手法を用いてマッピングを決定し、通信コスト、負荷の分散、実行時間、アプリケーション完了時間によって評価を行った。

モータ制御についてはセンサレスモータ 制御アルゴリズムより生成したタスクグラ フを用いた。実験には以下の PC を使用した。 OS: Windows7 Professional 64bit

CPU: Intel Xeon W5590 3.33GHz(2 ソケット) メモリ: 24GB

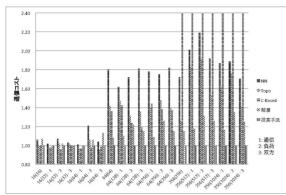

# 実験結果(通信コスト)

通信コストでの比較は図2のようになった。このグラフは提案手法の通信コストを1とした場合の各手法の通信コストのグラフである。グラフの×軸の値は「コア数(マージ前のタスク数)・マージ法の種類」である。マージ法の種類は1が通信コストのみを考慮したもの、2が負荷分散のみを考慮したもの、2が負荷分散のみを考慮したものである。なお、今回は実行時間である。なお、今回は実行時間である。なお、今回は実行時間にといる。グラフでは C-Based ILP 法の256 コアへのマッピングが結果無しとはこれる。

提案手法と NN Embed 法を比較した場合、NN Embed 法では、マッピング決定時に多くのランダム要素が入り、アーキテクチャ全体の情報を考慮していないのに対し、提案手法にはランダム性が無く、局所的なアーキテクチャ情報だけでなく、全体的なアーキテクチャの情報を考慮しているため、大きな差が生まれている。

Topo-LB 法は最初に配置されるコアの位置をもとに処理が進むが、その初期配置がTopo-LB 法の評価関数の仕様上、毎回のトポロジの中心付近になる。最適マッピング解を考える場合、最初に選ばれたタスクが配置されるべき場所が中心付近でなく、端に近い部

図2.通信コスト

分であった場合、その時点で最適解に到達す る事が不可能となるという欠点がある。一方、 提案手法では一つのタスクをあるコアにマ ッピングし、そのコアを中心として処理が進 むという性質は無く、全体のマッピング結果 が決定されて初めてコアへのマッピングが 行われる。つまり、各タスクはそれぞれふさ わしいコアにマッピングされるのである。し かし、16 コアへのマッピングでは、提案手法 を Topo-LB 法が上回っている点が見られる。 これは、提案手法内で使用している KL法[6] では、分割決定の評価関数が通信コストより も同数での分割ということに重きを置いて おり、このことによるコストの悪化が前述し た Topo-LB 法の問題点によるコストの悪化 を上回ってしまったためであると考えられ

Cluster-Based ILP 法に関しては、線形計 画法の特性上、一度に広い範囲のマッピング 問題を解く事が不可能である。つまりマッピ ング問題の対象が 12 タスクを超えると実用 的な時間でマッピング問題を解けなくなる。 そのため、今回の実験では線形計画法で解く 範囲を 8 タスク 8 コアのマッピングとし た。そのため、マッピング解の大部分がグラ フカット手法である KL 法によって決定され ており、その点がコストの悪化に繋がったと 考えられる。また Cluster-Based ILP 法内で 用いられている KL 法には、グループを崩し ながらタスクの交換を行うという機能は無 いため、局所最適解に陥りやすいこともコス トの悪化の一因になっていると考えられる。 KL 法の介入が少ない 16 コアへのマッピング では優れた通信コストを見せてはいるもの の、線形計画法を用いてマッピング問題を解 く手法は大規模なアーキテクチャへのマッ ピングには不向きであると考えられる。

元の階層クラスタリングを改良したものでは、内包タスク数に差を許して分割を行い、分割後にクラスタ間でタスクを移動するというクラスタリング部の差、そして配置法として NN Embed 法を用いているという配置部の差がこの通信コストの差に繋がっている。

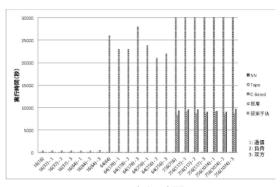

# 実験結果(実行時間)

各マッピング手法とマージ法の組み合わせによる実行時間のグラフを図3に示す。 C-Based ILP による 256 コアへのマッピング部分は、実行に8時間以上かかったため値無しとしてグラフの値を最大値としている。 IN Embed 法と Topo-LB 法のオーダはタスクグラフのエッジの数を|E|とした場合、O(|E|)であり、対象アーキテクチャのコア数を|v|とした場合、KL 法 $(O(|v|^3))$ がコア数オーダで出される提案手法と階層クラスタリンング法は $O(|v|^4)$ となっている。この計算については、アルゴリズム実装上の工夫である。

図3.実行時間

ただし、組込みアプリケーションにおいては、組込みプロセッサ上で同じアプリケーションが数年から数十年も作動し続けるという事が起こる。そういった場合、優れたマッピング結果によって実行時間が低減できるのであれば、数時間程度の計算時間は許容範囲であると考えられる。元の階層クラスタリングを改良したものでは、タスク数の差を許してクラスタを分割するという性質上、通信コストは悪くなるが、実行時間が小さいという性質を示した。

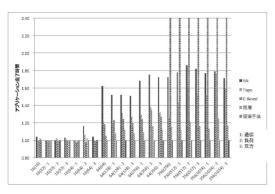

# 実験結果(アプリケーション完了時間)

アプリケーション完了時間での比較は図4のようになった。なお、クラスタ間通信に掛ける定数は10とした。このグラフは提案手法の完了時間を1とした場合の各手法の完了時間のグラフである。グラフではC-Based ILP法の256コアへのマッピングが結果無しとなっており、見やすさのためにグラフの値を最大値としている。

通信コストの比較と同様の傾向が見られる事が分かり、通信コストの最小化によってアプリケーション自体の実行時間が削減できるということを示している。ただし、タスクグラフのクリティカルパスが通信量の小さいエッジを多く含む場合、アプリケーション完了時間が削減しにくいという欠点があり、クリティカルパスとなりうるタスク群を事前に調査し、補正を掛けてマッピングする等の解決策が必要であると考える。

図4.アプリケーション完了時間

# 実験結果(モータ制御)

センサレスモータ制御[7]から生成した110 タスクのタスクグラフを用いて、通信コスト、アプリケーション完了時間、実行時間を指標として評価を行った。110 タスクのタスクグラフを、通信コストのみを考慮したマージ方法によって64 タスクにマージし、64コア集中メッシュトポロジにマッピングした。図5にその結果を示す。

| 通信コスト (提案手法を1に正規化)        |      |         |      |      |  |  |

|---------------------------|------|---------|------|------|--|--|

| NN                        | Торо | C-Based | 階層   | 提案手法 |  |  |

| 1.31                      | 1.26 | 1.10    | 1.05 | 1    |  |  |

| アプリケーション完了時間 (提案手法を1に正規化) |      |         |      |      |  |  |

| NN                        | Торо | C-Based | 階層   | 提案手法 |  |  |

|                           |      |         |      |      |  |  |

| 実行時間(秒) |      |         |       |       |  |  |

|---------|------|---------|-------|-------|--|--|

| NN      | Торо | C-Based | 階層    | 提案手法  |  |  |

| 0.16    | 0.31 | 260000  | 39.02 | 42.24 |  |  |

# 図5.モータ制御モデルにおける比較

通信コストとアプリケーション完了時間の比較では、提案手法の通信コストを 1 とけた場合の各手法の割合を示しており、実行時間は各手法の実行時間(秒)である。ランダム生成したタスクグラフにおける結果と同様の差が全体的に縮まっている。これは、セランスモータ制御のタスクグラフの通信と考えられる。およそ 40 秒の処理時間で、と考えられる。およそ 40 秒の処理時間で、過信コストにおいて平均 15%、アプリケーシと考えられる。およて 40 秒の処理時間で、ション完了時間において平均 8%の削減値は、ションカスク配置としては優れていると言える。

#### <引用文献>

[1] Edahiro, Masato and Yoshimura, Takeshi, New Placement and Global Routing Algorithms for Standard Cell Layouts, ACM/IEEE Design Automation Conf. (DAC), 642 - 645, 1990.

- [2] Lo, Virginia M., et al., OREGAMI: Tools for mapping parallel computations to parallel architectures, International Journal of Parallel Programming, Vol. 20, No.3, 1991, pp.237-270.

- [3] Agarwal, Tarun, et al., Topology-aware task mapping for reducing communication contention on large parallel machines, Parallel and Distributed Processing Symposium, 2006.

- [4] Tosun, Suleyman, Cluster-based application mapping method for Network-on-Chip, Advances in Engineering Software, Vol.42, No.10, 2011, pp.868-874.

- [5] http://ziyang.eecs.umich.edu/~dickrp/ tgff/

- [6] Kernighan, Brian W. and Shen Lin, An efficient heuristic procedure for partitioning graphs, Bell system technical journal, Vol.49, No.2, 1970, pp.291-307.

- [7] Akimatsu, Ryunosuke and Doki, Shinji, Improvetorque response using the inverter overmodulation range in position sensorless control system of PMSM, Industrial Electronics Society, IECON 2013 -39th Annual Conference of the IEEE Digital Object Identifier, 2013.

## 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

## 〔雑誌論文〕(計1件)

油谷 創, <u>枝廣 正人</u>, 階層構造を持つメニーコアアーキテクチャへのタスクマッピング, 情報処理学会論文誌, 査読有, Vol.56, No.8, 2015, 掲載予定.

## [学会発表](計1件)

油谷 創, 枝廣 正人, 階層構造を持つメニーコアアーキテクチャへのタスクマッピング,情報処理学会第34回組込みシステム研究会,2014年9月17日, 札幌.

## 6. 研究組織

(1)研究代表者

枝廣 正人(EDAHIRO, Masato) 名古屋大学大学院情報科学研究科 研究者番号:50578854

- (2)研究分担者 なし

- (3)連携研究者 なし

- (4)研究協力者 油谷 創(ABRADANI, Sou)