# 科学研究費助成事業 研究成果報告書

平成 2 8 年 6 月 1 日現在

機関番号: 11301

研究種目: 基盤研究(B)(一般)

研究期間: 2013~2015

課題番号: 25280011

研究課題名(和文)高安全知能システム応用ユニバーサルVLSIプラットフォームの構築

研究課題名(英文)Design of a Universal VLSI Platform for Highly-Safe Intelligent Systems

Applications

研究代表者

亀山 充隆 (Kameyama, Michitaka)

東北大学・情報科学研究科・教授

研究者番号:70124568

交付決定額(研究期間全体):(直接経費) 9,800,000円

研究成果の概要(和文): リアルワールド応用の高品質化と共にソフトウェア開発コストを激減するため,入力画像の特徴量及び高位記述情報フィードバックにより,環境に最も適するアルゴリズムを自律的に選択できるプラットフォームの開発を行った.また, 複数種類の危険に応答する高安全知能システムのハードウェアプラットフォームとして,非同期方式パワーゲーティング,チップ内パケット転送,細粒度から粗粒度の階層構造,直接アロケーションなどを新しいアーキテクチャを駆使することにより,転送ボトルネックの解消,コンフィグレーション・コントロールメモリサイズの減少,低電力化などの特徴を有するダイナミックリコンフィギャラブルVLSIの開発を行った.

研究成果の概要(英文): A computing platform for real-world intelligent systems is desired to contribute to low-cost implementation as well as high-quality and high-performance processing. As real-world applications, we consider advanced intelligent systems such as a highly-safe system. A universal platform for real-world intelligent systems are developed that from a set of training samples learns to select the best algorithm, so that it provides adaptive algorithm selection capability according to real-world environment conditions. Also, new dynamic reconfigurable VLSIs superior to the conventional FPGAs are developed based on new-concept architectures such as hierarchical structure which leads to seamless integration from coarse-grain to fine-grain reconfiguration, based on direct allocation of a control data flow graph which leads to reduction of interconnection and switch-box complexity, micropacket data transfer scheme which leads to configuration/control memory size reduction.

研究分野: 情報学

キーワード: 高安全知能システム リアルワールド応用 VLSIプラットフォーム アルゴリズム選択 ダイナミック リコンフィギャラブルVLSI マイクロパケット転送 コンフィグレーション/コントロールメモリ

#### 1.研究開始当初の背景

VLSI 化による知能システム応用の実現においては、コスト削減が大きな課題の1つとなっており、いかに高付加価値をもつ製画の鍵となっている。また人間生活に密業再の鍵となっている。また人間生活に密制を変全支援を行う、リアルワールド応用は今後の応用製品の有力な候補となり得る。そのため、センサでは直接認識できない情報も知にしながら、行動計画まで行う機能を持つカまりステム構築を目指した VLSI プラットフォームを開拓する。

### 2. 研究の目的

リアルワールド応用の典型である,人間に ふりかかる複数の重大な危険にリアルタイ ムで応答し,適切な行動支援を与える高安全 知能システム応用のための VLSI プラットフ ォームを構築する.産業界でのシステム VLSI 開発コストを大きく低減化可能なアプ ローチとして,応用機能要求及びリアルワー ルド環境に応じて,リアルタイムで適応的に 選択する「アルゴリズム選択機構」を開拓し た.この VLSI プラットフォームとして,コ ンフィグレーション / コントロールメモリ サイズを激減可能なパケット転送制御方式, 非同期方式パワーゲーティング,最適マッピ ングなどの革新的要素技術を駆使した,高性 能・低電力なダイナミックリコンフィギャラ ブル VLSI を開発する.これにより,高品質 な処理のみならず,現在深刻な問題である開 発コストを大幅に減少できる,高性能・低電 力な VLSI の産業復興に多大の貢献をするこ とを目的とする.

以上により,リアルワールド環境認識,予測,行動計画からなる処理モジュールを実行するユニバーサル VLSI プラットフォームの総合的評価を行い,その有用性を実証することができた.

#### 3.研究の方法

人間にふりかかる複数の重大な危険に応答し、適切な行動支援を与える高安全システム知能システム応用に必要とされる処理でルゴリズムの開発を行う・また、産業界でのソフトウェア開発コストを大きく低減及で可能なアプローチとして、応用機能要求化びリアルワールド環境に応じて、リアルタイが関係である・さらに、VLSIプラットコントで関拓する・さらに、VLSIプラットコントではメモリサイズを大幅に減少できる・ボラブル、VLSIアーキテクチャを検討し、パケット

転送による制御方式,非同期方式によるパワーゲーティングなどの革新的要素技術も駆使したダイナミックリコンフィギャラブル VLSIの設計・評価を行う.

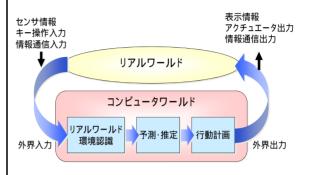

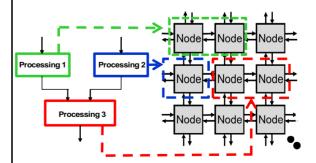

以上により、図1に示されるように、リアルワールド環境認識、予測、行動計画からなる処理モジュールを実行するユニバーサルVLSIプラットフォームの総合的評価を行い、その有用性を実証することができた。

図<u>1</u> リアルワールド応用知能システムの モデル

#### 4. 研究成果

リアルワールド応用の典型である,人間にふりかかる重大な危険に応答し,適切な行動支援を与える高安全知能システム応用 VLSI プラットフォームを構築するため,以下のような特徴を有する高安全知能システム応用 VLSI コンピューティングの基盤技術を開拓することができた.

# (1)優先順位に基づく危険事象の選択

実世界環境には多様な危険事象が存在しているため、全ての危険事象に対して、リアルタイムで応答可能なシステムの構築は困難である.従って、個々人固有の状況に応じた統計データを利用して各危険事象が引き起こすリスクの期待値の大きさによって、優先順位を決定し、ある個数に限定した危険事象を選択する.

(2)高安全知能システムの危険事象検出 画像情報を用いて危険要素の抽出を行う. 入力画像から特徴抽出を行い,画像表現手法 である Bag-of-Features などの画像認識手法 に基づき,サポートベクターマシンを用いて 入力画像の識別を行う.例えば強盗検出や歩 行者の交通事故の応用を開拓した.

## (3)自律的アルゴリズム選択

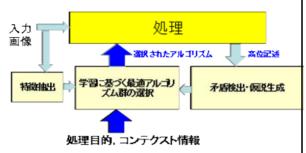

リアルワールド応用知能システムにおいては,環境に応じた高品質処理と共に,ソフトウェア開発コストを激減するため,入力特

徴情報と共に,高位記述情報のフィードバックにより,環境に最も適する処理アルゴリズムの自律選択機構を有するユニバーサルなプラットフォーム構築が望まれる.図2はその概念図である.

図2 アルゴリズムの自律選択機構

これに基づき,リアルワールド環境での知能処理アルゴリズム群の中から,実環境において最も適切となるアルゴリズム要素の部分集合とそれらの入出力接続関係を自律的に選択・決定する方法を,モジュール選択機能の実用性をシミュレーションにより行った.

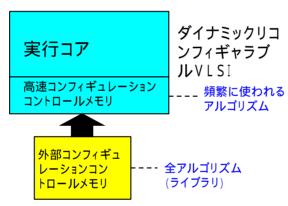

図3 ダイナミックリコンフィギャラブル VLSI におけるソフトウェアリコン フィグレーション

(4) VLSI プラットフォームでのダイナミックリコンフィギャラブル VLSI

アルゴリズム選択機構は,ダイナミックリコンフィギャラブルVLSIにおける,ソフトウェアリコンフィギュレーションとの親和性があり,この様子を図3に示す.複数種類の処理を切り替えていく必要があるため,各処理を動的に再構成可能な VLSI アーキテクチャが有用である.

開発したダイナミックリコンフィギャラブル VLSI の主要な構成概念は以下の通りである.

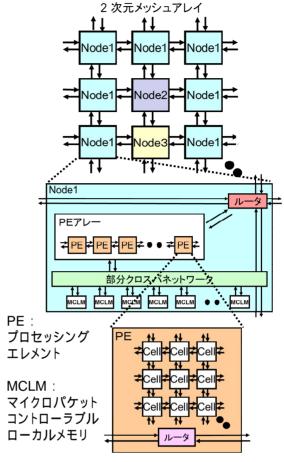

階層構造を有するダイナミックリコンフィギャラブル VLSI

図4は,粗粒度から細粒度の階層構造を有する提案するダイナミックリコンフィギャラブル VLSI である.

図4 階層構造を有するダイナミックリコン フィギャラブル VLSI アーキテクチャ

各階層でのコントロールデータフローグ ラフ(CDFG)の直接アロケーションによる 処理

上位階層の CDFG における直接アロケーションの例を図 5 に示す.このように,各階層において直接アロケーションを導入することにより,データ転送はほとんど隣接するノード間で済むようになる.

<u>図5</u> ノードレベル CDFG における直接アロ ケーション

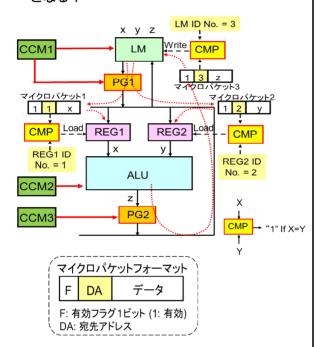

マイクロパケット転送に基づくコンフィ グレーションメモリサイズの減少

図6 マイクロパケット転送方式

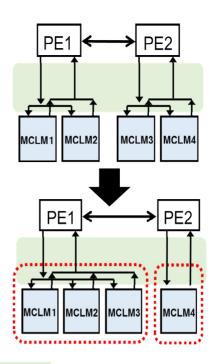

マイクロパケットコントローラブルロ-カルメモリ(MCML)の動的再構成

MCLM の動的再構成の例を図7に示す.各 PEとメモリ間のデータの転送は,複数の近傍メモリに接続切り替え可能な部分クロスバタットワークを介して行う.MCLM には,各 PEにおける占有 MCLM と複数の PE にとなりにおける占有 MCLM と複数の PE にとなれての MCLM となり得る接続切り替え可能となれずを制御することにより,どの PE にるながである。アプリケーションの中でにるよりなる。アプリケーションの中でによりスケジューリングやアロションの自由度が増し,処理時間の短縮が可能となる.

:部分クロスバーネットワーク MCLM:マイクロパケットコントローラブルローカルメモリ

図<u>7</u> マイクロパケットコントローラブル ローカルメモリの動的再構成

# (5)今後の展望

危険要素抽出等の処理の高品質化,ソフトウェアリコンフィグレーション及び動的再構成可能である VLSI プラットフォームは,種々の危険に対するユニバーサルな高安全知能システムの構成に有用となる.

今後は,実際の大規模な処理である CDFG に対して,直接アロケーションに基づく階層 構造に基づくダイナミックリコンフィギャラブル VLSI への自動マッピング等の自動設計ソフトウェアを開発する意義がある.また,提案した VLSI コンピューティングプラットフォームは,高安全知能システムのみではなく,より広いリアルワールド知能システムの応用にも適用可能になると思われる.

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

### 〔雑誌論文〕(計17件)

Lukac, Kamila Abdiyeva, Martin Yoshichika Fujioka and Michitaka Kameya<u>ma</u>, "Algorithm Selection Platform in Real-World Intelligent Systems", Proceedings of the 28th International Conference on Computer Applications in Industry Engineering, 査読有, pp.227-234, 2015.

Yasuhiro Takei, Hasitha Muthumala Waidyasooriya, Masanori Hariyama and M<u>ichitaka Kameyama</u>, "Data-Transfer-Aware Design of an FPGA-Based Heterogeneous Multicore Platform with Custom Accelerators", IEICE Transaction on Fundamentals, 查読有, Vol.E98-A, No.12, pp. 2658-2669, 2015.

DOI: 10.1587/transfun.E98.A.2658) Martin Lukac. Kamila Abdiyeva and Michitaka Kameyama, "Symbolic Algorithm Segmentation Using Selection and Semantic Feedback", the Scene Proceedings of Understanding Workshop 2015, 查読有, 2015.

URL:http://sunw.csail.mit.edu/2015/posters.html

Martin Lukac, Kamila Abdiyeva and Michitaka Kameyama, "Evaluation of Algorithm Selection Approach for Semantic Segmentation Based on High-Level Information Feedback", Proceedings of the International Conference on Information and Digital Technologies, 査読有, pp.212-218, 2015.

Zhengfan Xia, Masanori Hariyama, Michitaka Kameyama, "Asynchronous Domino Logic Pipeline Design Based on Constructed Critical Data Path", IEEE Transactions on Very Large Scale Integration Systems, 查読有, Vol.23, No.4, pp.619-630, 2015. DOI:10.1109/TVLSI.2014.2314685

Martin Lukac, <u>Michitaka Kameyama</u>, "Bayesian-Network-Based Algorithm Selection with High Level Representation Feedback for Real-World Information Processing", IT in Industry, 查読有, Vol.3, No.1, pp.10-15,2015.

Martin Lukac and Michitaka Kameyama, "Bayesian-Network-Based Algorithm Selection with High Level Representation Feedback for Real-World Intelligent Systems", Proceedings of the 9th International Conference on Information Technology and Applications, 査読有, 2014.

URL:http://www.icita.org/2014/papers.htm

Yoshiya Komatsu, Masanori Hariyama and Michitaka Kameyama, "An Asynchronous High-Performance FPGA Based on LEDR/Four-Phase-Dual-Rail Hybrid Architecture", Proceedings of the 5th International Symposium on Highly-Efficient Accelerators and

Reconfigurable Technologies , 査読有, pp.111-114,2014.

Martin Lukac, Michitaka Kameyama and Yoshichika Fujioka, "Automatic Algorithm Selection for Real-World Intelligent Systems Platform", Proceedings of the 23rd International Workshop on Post-Binary ULSI Systems, 査読有, pp.7-14, 2014. Martin Lukac, Michitaka Kameyama and Yoshichika Fujioka, "VLSI platform

Yoshichika Fujioka, "VLSI platform for Real-World Intelligent Integrated Systems based on Algorithm Selection", IADIS International Journal on Computer Science and Information Systems, 查読有 Vol. 8, No. 2, pp.72-90, 2013.

Zhengfan Xia, Masanori Hariyama, <u>Michitaka Kameyama</u>, "A Low-Power FPGA Based on Self-Adaptive Multi-Voltage Control", Proceeding of the International SoC Design Conference, 查読有, pp.166-169, 2013.

Martin Lukac and Michitaka Kameyama, "Bayesian Network for Algorithm Selection: Real-World Hierarchy for Nodes Reduction", Proceedings of the International Conference on Awareness Science and Technology, 查読有, pp. 69-74, 2013.

DOI 10.1109/ICAwST.2013.6765411

Yoshiya Komatsu, Masanori Hariyama, Michitaka Kameyama, "Architecture of an Asynchronous FPGA for Handshake-Component-Based Design", IEICE Transaction on Information and Systems, 查読有, Vol.E96-D, No.8, pp.1632-1644, 2013.

DOI:10.1587/transinf.E96.D.1632

Xu Bai, <u>Michitaka Kameyama</u>, "A

Bit-Serial Reconfigurable VLSI Based

on a Multiple-Valued X-Net

Data Transfer Scheme", IEICE

Transactions on Information and

Systems, 查読有, Vol.E96-D,No.7,

pp. 1449-1456 2013

pp.1449-1456,2013. DOI 10.1587/transinf.E96.D.1449 Yoshiya Komatsu, Masanori Hariyama Michitaka Kameyama, "An Area-Efficient Asynchronous FPGA Architecture for Handshake-Component-Based Design", Proceeding of International the Conference Engineering on ٥f Reconfigurable Systems Algorithms, 查読有, pp. 15-18, 2013. Martin Lukac, Michitaka Kameyama and Yoshichika Fujioka, "VLSI Platform for Real-World Intelligent Integrated Systems Based Algorithm on

Selection", Proceedings of the IADIS Theory and Practice in Modern Computing, 查読有, pp.27-34, 2013.

Xu Bai, Michitaka Kameyama, "An Area-Efficient Multiple-Valued Reconfigurable VLSI Architecture Using an X-Net", Proceedings of the 43th IEEE International Symposium on Multiple-Valued Logic, 查読有, pp.272-277,2013.

DOI 10.1109/ISMVL.2013.13

# [学会発表](計 11件)

<u>亀山充隆</u>, "リアルワールド応用知能システムとその VLSI コンピューティングプラットフォームの展望",電子情報通信学会技術報告,ICD2015-46,pp.37-42,2015年10月20日,作並一の坊,宮城.大河原茂樹,<u>亀山充隆</u>,"危険要素抽出に基づく高安全システムの高品質化とVLSI プラットフォーム",FIT 情報科学技術フォーラム,C-017,2015年9月17日,愛媛大学工学部棟,愛媛.

大河原茂樹,<u>亀山充隆</u>,藤岡与周,"高 安全知能システムの高品質化と VLSI コンピューティングプラットフォーム", 多値論理研究ノート,Vol.38,No13, pp.13-1 - 13-6,2015年9月13日,北海 道大学大学院情報科学研究科,北海道. 大河原茂樹,<u>亀山充隆</u>,藤岡与周"高安全 知能システム用リコンフィギャラブルプロセッサのアーキテクチャ",電気関係学 会東北支部連合大会,2012,2015年8月28日,岩手県立大学,岩手.

Michitaka Kameyama, "Prospects of Computing Platform for Real-World Intelligent Systems", The International Conference on Information and Digital Technologies 9 July, 2015, Zilina, Slovakia. 大河原茂樹,亀山充隆, "危険要素抽出の 高精度化に基づく高安全知能システムの 構成",情報処理学会第77回全国大会, 3T-02, pp.2-473~2-474,2015年3月18 日.京都大学吉田キャンパス,京都. 大河原茂樹, Lukac Martin, 亀山充隆、 危険要素の抽出に基づく高安全知能シス テム",電気関係学会東北支部連合大 会,2H20,2014年8月22日,山形大学工

小松与志也,張山昌論,<u>亀山充隆</u>,"LEDR/4相2線ハイブリッドアーキテクチャに基づく高性能非同期 FPGA",電子情報通信学会技術報告,RECONF2014-6,pp.27-302014年6月12日,東北大学さくらホール,宮城.

学部キャンパス,山形.

白 旭,<u>亀山充隆</u>, "電流モード論理に基 づく多値細粒度リコンフィギャラブル VLSI の新概念アーキテクチャ", 電子情報通信学会技術報告,ICD2013-81, Vol. 113, No. 236, pp.59-64,2013 年 10 月 8 日, 弘前大学コラボ弘大 八甲田ホール,青森.

原田伸太郎,白旭,藤岡与周,<u>亀山充隆</u>, "ビットシリアルパケット転送に基づく ロジックインメモリ多値リコンフィギャ ラブル VLSI",多値論理研究ノート, Vol.36,No.9,pp.9-1 - 9-6,2013年9 月14日,姫路市市民会館,兵庫. 原田伸太郎,白 旭,藤岡与周,亀山充

原田伸太郎,白 旭,藤岡与周,<u>亀山充隆</u>、"パケット転送制御に基づくロジックインメモリ構造多値リコンフィギャラブル VLSI",電気関係学会東北支部連合大会,1006,2013年8月23日,会津大学キャンパス,福島.

### 6. 研究組織

# (1)研究代表者

亀山 充隆 (MICHITAKA KAMEYAMA) 東北大学・大学院情報科学研究科・教授 研究者番号:70124568