# 科学研究費助成事業研究成果報告書

平成 29 年 8 月 10 日現在

機関番号: 5 4 5 0 2 研究種目: 若手研究(B) 研究期間: 2013~2016

課題番号: 25871039

研究課題名(和文)欠陥への電子捕獲により動作するグラフェンメモリの原理解明と性能向上に関する研究

研究課題名(英文) Investigation of elucidating a mechanism and the improvement of a performance in graphene memory which operate by electron trap to defects

### 研究代表者

市川 和典 (Ichikawa, Kazunori)

神戸市立工業高等専門学校・その他部局等・准教授

研究者番号:90509936

交付決定額(研究期間全体):(直接経費) 3,500,000円

研究成果の概要(和文):当初の目的であるグラフェンメモリの基礎となる単層グラフェンおよび多層グラフェンの作り分け技術を確立することができた。特に水素ガスの効果は重要であり、昇温時の水素はグラフェン核形成を促し、冷却時の水素はエッチング効果がある。水素によりグラフェンの形成した後すぐに欠陥導入をできるようになり、より再現性の高いメモリを作製することができた。欠陥の量が多くなるとメモリの性能が上がり、また電子の方が欠陥に捕獲されやすいことも明らかとなった。これらの結果から欠陥へ電子を捕獲することで動作するグラフェンメモリの動作と原理を明らかにすることができた。

研究成果の概要(英文): We established the fabricating monolayer and multilayer graphene technology for basic to graphene memory. Especially the effective of hydrogen gas was important. Hydrogen gas in raising period promotes graphene nuclear growth and its in cooling period etched graphene. We fabricated graphene memory with a high performance because some defects were fromed by hydrogen gas immediately after graphene fabrication. Memory performance increased with an the number of the density of defects increased. Furthermore, electrons tended to be trapped to the defects. From the results obtained in these investigations, we revealed the memory operation and principle in graphene memory which operate by electron trap to defects.

研究分野: 半導体工学

キーワード: グラフェン フラッシュメモリ 熱CVD

# 1. 研究開始当初の背景

フラッシュメモリはスマトーフォンに代表される携帯端末用メモリとして現在欠かくにつれて半導体中の欠陥に電子が捕獲発した。その中でグラフェンはその形成のおきととなりをフランはそのではないかと考えた。予備実験としてより欠陥を導入したがあるのではないかと考えた。予備実験フラッシュメモリとすると、わずかにこの新しい原理で動作するメモリの動作解をあるが発出に欠陥とメモリの動作解を明に欠陥をメモリの大路をフラッシュが現れメモリとして動作した。明まり詳細に欠陥とメモリの性能の関係をあため本科研費に申請した。

# 2. 研究の目的

これまで欠陥に電子を捕獲することで機能する新原理のフラッシュメモリの動作を予備研究で実証し、新たなグラフェンの性能には劣ること、層数により動作原理が異なのとなった。を見いまないかとなった。本研究のはその課題が明らかとなった。本研究のはその課題解決とグラフェンの構築および詳細な原理解明をである。計画している具体的な保件へには、①欠陥のないグラフェンの形成条件のよと層数制御、②多層・単層グラフェンの形成条件へには、①欠陥のないグラフェンの形成条件へに対した。とを関するメモリ性能への影響、④詳細な原理解のよとメモリ性能への影響、④詳細な原理解のよとメモリ性能への影響、④詳細な原理解のよるメモリ性能への影響、④詳細な原理解のよるメモリ性能への影響、④詳細な原理解のよるメモリ性能への影響、④詳細な原理解のよる。

#### 3. 研究の方法

研究期間において以下の研究を行う①欠陥のないグラフェンの形成条件の検討と層数制御、②多層・単層グラフェンへの欠陥導入③メモリデバイス作製と層数によるメモリ性能への影響、④原理解明とトランジスタとメモリの形成を明らかにする。

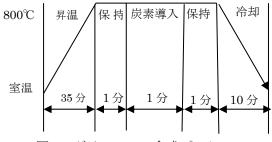

グラフェンの合成プロセスを図1に示す。 まず Si 基板をアセトン、メタノール用いて有 機洗浄し、酸素 100%中で 1000℃、1 時間熱 酸化を行い基板上に SiO2層を 100 nm 形成し た。次に、マグネトロンスパッタにより Ni を 400 nm の膜厚で蒸着し、RTA 装置により グラフェンを以下の条件で合成した。H<sub>2</sub>の流 量は、450 sccm に対して 1~20%とし H<sub>2</sub> と Ar の混合ガスを流しながら、室温から合成温 度の 800℃までこれまでの本研究で最も早い 昇温時間である 35 分で昇温した。そして温 度安定とガスの切り替えのため 800℃で Ho の供給を止め 1 分間保持後、C<sub>2</sub>H<sub>2</sub>と Ar を 1: 1の割合で各 100 sccm の流量で 1 分間導入し た。その後 C<sub>2</sub>H<sub>2</sub> の供給を止め、冷却準備の ため Ar のみを 450 sccm 流し1分間保持後、 急冷(約 10 分間) により 150 ℃程度まで冷却 を行いグラフェンを合成した。グラフェンの 層数、結晶構造、欠陥の評価は励起波長 532 nm の UV ラマン分光測定によりそのスペクトルから解析を行った。またデバイス特性にはトランジスタおよびメモリを作製し評価を行った。

図1 グラフェンの合成プロセス

### 4. 研究成果

研究期間全体を通して以下のことが明らかとなった。

① Ni 触媒が厚くなるにつれてグラフェンの 層数が薄くなる。

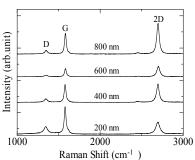

図2 様々なNi 膜厚上に作製したグラフェン のラマンスペクトル

アセチレンガスと窒素ガスと 3 %の水素ガス雰囲気中, Ni の膜厚 200, 400, 600, 800 nm で合成した.この G バンドと 2D バンドとの強度比である  $I_G/I_{2D}$  から,合成されたグラフェンの層数は Ni 膜厚が 200 nm の時に最も多く,800 nm の時に最も少なくなるため Ni の膜厚を厚くするにつれてグラフェンの層数が少なくなる。

②冷却時間は窒素中でできるだけ早く下げることで欠陥が低下する。

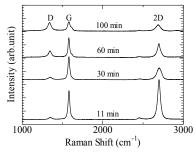

図 3 様々な降温時間で合成したグラフェンのラマンスペクトル

ラマンスペクトルから計算した 11,30,60,100 min のドメインサイズは 240,107,120,

69 nm であり冷却速度を速くすることでドメインサイズを大きくすることができる. また11 min で冷却して合成したグラフェンは単層となり、冷却するにつれて層数が最も少なり、欠陥も減少する。

③アセチレンと窒素の量を1:1の流量比により均一性が向上する。

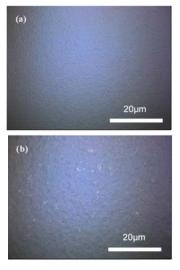

図3 (a)1:1 (b)4.5:1 で合成したグラフェン表面の顕微鏡像

$N_2:C_2H_2=4.5:1$  の割合でグラフェンを成長した場合は多層のグラフェンが形成されていたが、1:1 の場合、均一性が高く 2 層のグラフェンが形成され、比率を下げるにつれてグラフェン層が薄くなることが明らかとなった。この結果から、アセチレンと  $N_2$  の流量は 1:1 が均一で薄い層のグラフェンを成長させることができることが明らかになった。

④昇温時の水素濃度を多くすると厚く、少なくすると薄い層ができ、水素の濃度で層数を制御することができる。

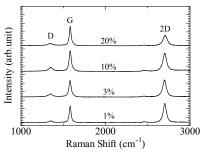

図 4 様々な昇温時の水素濃度で合成したグラフェンのラマンスペクトル

$H_2$  濃度が高くなるにつれて層数が厚くなることが分かった。 $H_2$  を入れない条件でもアセチレンに含まれる  $H_2$  によってグラフェンが形成されるが、表面は均一にはならなかった。このことからグラフェンの成長には水素は必要であり、立ち上がりの水素の濃度が層

数制御に重要であることが明らかとなった。

⑤Ni に固溶した炭素は冷却によってすべて 析出せず一部 Ni 内に留る。

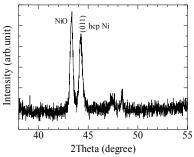

図 5 グラフェン除去後の XRD 測定結果

グラフェンの除去を確認後、残った Ni の XRD (X-ray diffraction) の測定を行うと、NiC のメインピークである 44.7°の(011)ピークが現れていることから、今回の Ni 薄膜は六方最密充填(hcp)構造をしていることが分かる. よってこれまで純 Ni と考えられていたグラフェン合成後の Ni には炭素が含まれており、Ni 薄膜を触媒とした CVD においてグラフェンを急冷にて合成する場合では、一度 Ni に固溶した炭素原子は冷却によりすべて析出せず、いくらかは Ni 中に留まることが明かとなった.

⑥冷却時の水素によりグラフェンに欠陥を 導入することができる。それにより同一チャンバー内でグラフェンの合成と欠陥導入が 可能となり、このグラフェンを熱酸化膜が形 成された Si 基板へ転写することで、欠陥層が 浮遊ゲートになりメモリとして動作した ⑦電子は欠陥に捕獲されやすく正孔側に比 べ欠陥の影響を受けやすい。

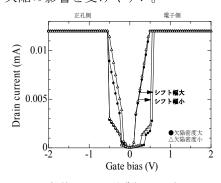

図 6 欠陥導入後に作製したグラフェンメモリの電気特性評価

水素中で冷却を行い欠陥を導入したメモリを作製し評価すると、メモリ動作を示すヒステリシス曲線が現れた。このことから欠陥により電子が捕獲されメモリとして動作していることが分かった。また正電圧側の方が負電圧側に比べてヒステリシス幅が大きいため電子の方が欠陥に捕獲されやすいことが明かになった。

⑧チャンバー内の残留酸素により転写しなくてもデバイス化が可能である。

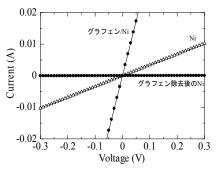

図 7 グラフェン/Ni, Ni, グラフェン除去 後 Ni の電流-電圧測定

Ni 上に合成したグラフェン,合成前の Ni,合成後グラフェンを除去した Ni のそれぞれの I-V (電流-電圧) 測定を行った. 今回は 2端子法を用い,これら 3種類の基板に 2本のプローブ (プローブ間距離  $10~\mu m$ ) を接触させ I-V の測定を行った. グラフェンの除去後の Ni の電流値は大幅に減少し,抵抗値がグラフェン除去前や純 Ni に比べ大幅に増加した.すなわち形成後のグラフェン及び Ni では大きな抵抗の差が生じるため,転写せずとも電気特性評価は可能であると言える。

以上の結果から当初の目的であった欠陥へ電子を捕獲することで動作するグラフェンフラッシュメモリの動作と原理解明に成功したことに加え、新たな研究テーマも見つかり、この研究を発展させ新たに 2016 年度から科研費基盤 C に採択されるなど、今後につながる充実した研究期間であった。

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

〔雑誌論文〕(計1件)

# [雑誌論文]

1.  $\lceil$  Influence of nickel catalyst film thickness and cooling condition for synthesis of monolayer graphene by thermal chemical vapor deposition at  $800~^{\circ}\text{C}\,\rfloor$

Kazunori Ichikawa, Hiroshi Akamatsu, Yoshiyuki Suda, Yoshiyuki Nonoguchi, Yukiharu Uraoka, Journal of Materials Science and Engineering B, 9, pp.341-346,査読あり

〔学会発表〕(計12件)

- 1. 「水素ガスにより膜厚制御した単層グラフェン FET の特性評価」小野 誠,市川 和典, 赤松 浩, 須田善行,高専シンポジウム 2016, Pa-004、(2016.1.23)

- gas in nitrogen/hydrogen gas mixture during temperature rising period in chemical vapor deposition K. Ichikawa, H.Akamatsu and Y. Suda, The 37th International Symposium on Dry Process (DPS2015), P-36, (2015.11.5)

- 3. 「Synthesis of monolayer and multilayer graphene on nickel catalyst film by thermal chemical vapor deposition using acetylene gas at 800 °C」 K. Ichikawa, H. Akamatsu and Y. Suda Irago Confernce, 2015, P30, (2015.10.22)

- 4.「プロセスガス制御によるグラフェンの層数制御および FET の作製」 松原 暉,市川和典,赤松 浩,須田善行 応用物理学会関西支部,P-33 (2015.2)

- 5.「グラフェンの成長における熱 CVD 法条件の研究」松原暉,市川和典,赤松浩,須田善行,産学官金技術フォーラム 14, OB-1-1 (2014.11)

- 6.「プロセスガスの制御による単層および多層 CVD グラフェンの作り分け技術」松原暉,市川和典,赤松浩,須田善行,第 11 回薄膜材料デバイス研究会,31P11 (2014.10)

- 7. 「グラフェン -歴史・現状・将来-」市川 和典、電気情報通信学会 ソサイエティ大会, (2014.9)

- 8.「熱 CVD 法による欠陥 0 を目指した単層グラフェンの成長条件の検討」市川 和典, 第1回 出雲薄膜材料デバイスミニ研究会, pp.1 (2014.3.4)

- 9. 「Evaluation of two Si layers simultaneously crystallized LTPS-TFT memory using high dielectric constant material for the tunnel oxide」 Kazunori Ichikawa, Akira Matsubara, Hiroshi Akamatsu, Koji Yamasaki, Masahiro Horita, Yukiharu Uraoka, ITC2014, pp.100 (2014.1.23)

- 10. 「グラフェンの成長に及ぼす水素および 金属触媒膜厚の影響」松原 暉, 市川 和典, 赤松 浩, 須田 善行, 第 10 回薄膜材料デバ イス研究会, pp.179~182 (2013.10.31)

- 11.「グラフェンを用いたフラッシュメモリの 実証研究」市川 和典, STARC ワークショップ, pp.80~81 (2013.9.12)

- 12.「電子デバイス応用に向けたグラフェンの 合成条件の評価」松原 暉, 市川 和典、平 成 24 年度分高専連携教育研究プロジェクト 学生成果報告会, 2, 26, (2013.8.23)

〔図書〕(計0件)

[産業財産権]

- ○出願状況(計0件)

- ○取得状況(計0件)

[その他]

ホームページ等

http://www.kobe-kosen.ac.jp/~ichikawa/

# 6. 研究組織

(1)研究代表者

市川 和典(ICHIKAWA, Kazunori) 神戸市立工業高等専門学校 電気工学科・

准教授 研究者番号:90509936

- (2)研究分担者 なし

- (3)連携研究者 なし

- (4)研究協力者

須田 善行 (SUDA, Yoshiyuki)

豊橋技術科学大学 電気電子情報系·

准教授 研究者番号:70301942

浦岡 行治 (URAOKA, Yukiharu)

奈良先端科学技術大学院大学 物質創成科

学研究科·教授 研究者番号: 20314536