# 科学研究費助成事業 研究成果報告書

平成 27 年 6 月 8 日現在

機関番号: 17102

研究種目: 研究活動スタート支援

研究期間: 2013~2014 課題番号: 25889041

研究課題名(和文)金属ソース・ドレイン型ゲルマニウムスピンMOSFETの創製

研究課題名(英文) Invention of a metal-source/drain-type Germanium spin-MOSFET

#### 研究代表者

笠原 健司 (Kasahara, Kenji)

九州大学・システム情報科学研究科(研究院・特任助教

研究者番号:00706864

交付決定額(研究期間全体):(直接経費) 2,100,000円

研究成果の概要(和文):原子層レベルで急峻な界面を持つ高規則度L21 - Co2FeSi電極をスピン注入・検出電極に用いることで、従来電極(Fe/MgOトンネル接合電極など)よりも二桁近く高いGe中へのスピン生成効率(~0.12)を実現し、その検出温度を100 K以上も上昇させることに成功した。また、硫化アンモニウム水溶液によるp - Ge(111)基板の表面処理が、原子整合した体心立方構造金属/Ge(111)接合によるフェルミレベルピニングの影響の緩和効果を大幅に安定化させることを見出した。更に、金誘起層交換成長(GIC)法を改善して大粒径化させたGe結晶粒を用い、300 以下という低温で薄膜トランジスタの作製に成功した。

研究成果の概要(英文): Using the lateral spin-valve devices with the highly-ordered L21- Co2FeSi/n+-Ge Schottky tunnel contacts, we have realized the spin generation efficiency of ~0.12 which is about two orders magnitude larger than that for the previously reported devices with the Fe3Si/MgO tunnel barrier contacts, and succeeded that the spin-valve signals can be obtained at 275 K. We also have demonstrated that by using a (NH4)2S treatment on the Ge surface, a reduction in Fermi-level pinning can reproducibly be achieved at atomically matched bcc-alloy/Ge(111) interfaces. In addition, we have fabricated the Ge thin film transistors (TFTs) below 300 oC by using a modulated gold-induced-crystallization.

研究分野: スピントロニクス

キーワード: スピンMOSFET ゲルマニウム

## 1. 研究開始当初の背景

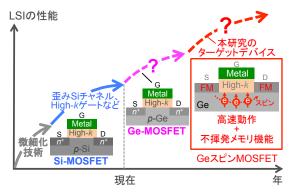

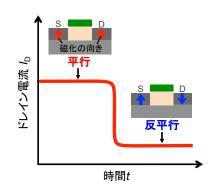

近年の Large Scale Integration (LSI)には、 その性能向上のために歪み Si チャネルや high-k ゲート技術など、「単なる微細化に留 まらない新しい技術」を用いて作製された Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET)が次々と導入されて おり、今後はSiよりもキャリア移動度が高い Ge チャネルを用いた MOSFET の積極的な 導入が予想されている(図 1) $^{\odot}$ 。一方、LSI の 超低消費電力化には、その不揮発化が有効と されており①、これを実現し得る次世代デバ イスとして、菅原と田中によって提案された 『スピン MOSFET』の創製に期待が高まっ ている[図 1, 2] $^{2}$ 。このデバイスは、MOSFET のソース・ドレイン(S/D)電極を従来の P/N 接合電極から強磁性金属(FM)電極に置き換 えた構造をしており、ゲート電圧( $V_G$ )の変調 だけでなく FM-S/D 電極における磁化配置の 変更(平行・反平行)でもドレイン電流(I<sub>D</sub>)の変 調が可能である<sup>②</sup>。このためこのデバイスは、 従来の MOSFET が元々持っているスイッチ ング機能に加えて「不揮発性メモリ機能」と いう別の機能も有している。もし、Ge チャ ネルを有したスピン MOSFET、即ち Ge スピ ン MOSFET が創製されれば、「Ge チャネル による LSI の高速動作化」と「不揮発性メモ リ機能による LSI の超低消費電力化」の両立 が実現し、Ge-MOSFET の創製をも上回る LSI の性能向上が期待される(図 1)。

図 1. LSI の性能向上に対する本研究の位置 付け。

図 2 . Ge スピン MOSFET における FM-S/D 電極の磁化配置による不揮発メモリ機能。

#### 2. 研究の目的

- (1) Ge スピン MOSFET の実現には、FM 電極から Ge チャネル中にスピンを電気的に注入し、そのスピンを電気的な手法により検出できなければならない。これまでに Fe/MgO トンネル接合®や  $Fe_3Si$ ®をスピン注入・検出用の FM 電極として用いて Ge 中におけるスピン注入・伝導を示唆する結果が報告されているが、これらの研究では FM 電極のスピン注入・検出効率が低いたのもこ、その観測は 200~K 以下に留まっていた。本研究では、Fe や  $Fe_3Si$  よりもる  $Co_2FeSi(CFS)$ ®を FM 電極としずの検出温度の高温化を試みた。

- (2) もう一つの課題は、FM/Ge 接合にお ける電気伝導特性制御の困難さである。ほ とんどの金属/p-Ge 接合はフェルミレベルピ ニング(FLP)と呼ばれる現象のために正孔に 対するショットキー障壁高さ(ΦB)が金属の 仕事関数( $\Phi_{\rm M}$ )にほとんど依存せず、極端に低 くなることが知られている<sup>®</sup>。このため何の 対策も講じなければ、金属ソース・ドレイン 型 Ge スピン MOSFET はゲート電圧が OFF の状態でもリーク電流をほとんど抑制でき ず、MOSFET としての動作ができない。研 究代表者はこれまでに、原子整合した体心立 方構造(bcc-)金属/p-Ge(111)接合が FLP の影 響を緩和する現象を見出しているが、この効 果は、試料間で大きくばらつき、全く安定し ていないことが課題であった<sup>©</sup>。この FLP 緩 和効果における不安定性の原因は、金属 /Ge 界面の欠陥であると考えられる。そこ で本研究では、p-Ge(111)基板に表面処理を 行い、上記の FLP 緩和効果の安定化を図っ た。

- (3) また近年では、超軽量、超低消費電力かつコンパクトなフレキシブルシステムインディスプレイが注目を集めており、これを実現するためにフレキシブル基板(軟化温度: ~300  $^{\circ}$ C)上への高キャリア移動度を有する半導体材料の低温形成技術の開発が盛んに行われている。研究代表者は、ごく最近開発された金誘起層交換成長(GIC)法 $^{\circ}$ と呼ばれる Ge の低温結晶化技術に着目し、これを用いてフレキシブル基板の軟化温度(~300  $^{\circ}$ C)以下で作製できる薄膜トランジスタ(TFT)の開発を試みた。

### 3. 研究の方法

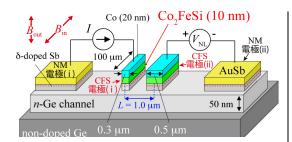

(1) 本研究では、スピン注入・伝導の検出法として一般的な 4 端子非局所磁気抵抗測定法及び 4 端子ハンル効果測定法を行った。まず、低温分子線エピタキシー(MBE)法を用いて  $CFS/n^+$ - $Ge/n^-$ Ge(111)構造を作製し<sup>®</sup>、電子線リソグラフィー法及び  $Ar^+$

図3. 本研究で Ge 中におけるスピン注入・ 伝導を検出するために作製した横型スピンバ ルブ素子の概略図。

イオンミリング法を用いてサブ  $\mu m$  オーダーの極微細な横型スピンバルブ素子を作製した(図 3)。このデバイスの CFS 電極(i)-非磁性(NM)電極(i)間に定電流 I を流した状態で、面内若しくは面直方向に磁場(それぞれ  $B_{\rm in}$ 若しくは  $B_{\rm out}$ )を掃引し、CFS 電極(ii)-NM 電極(ii)間における電圧(非局所電圧)の変化量  $\Delta$   $V_{\rm NL}$  から算出される非局所磁気抵抗  $\Delta$   $R_{\rm NL}$ (=  $\Delta$   $V_{\rm NL}$  I)を測定した。

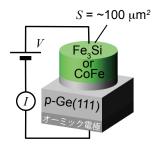

(2) 本研究では、Ge 基板の表面処理方法 として、Ge 基板を硫化アンモニウム ((NH<sub>4</sub>)<sub>2</sub>S)水溶液に浸漬する方法(Sトリー トメント)を用いた。絶縁体/Ge 接合では あるが、この方法を用いることで界面準 位の低減に起因した電気伝導特性の改善 が報告されており®、本研究の原子整合し た bcc-金属/Ge(111)接合においても界面 欠陥の低減が期待できると考えた。まず、 表面の自然酸化膜を薄いフッ酸水溶液で 除去した p-Ge(111)基板を約 80 ℃に加熱 した(NH<sub>4</sub>)<sub>2</sub>S 水溶液に 20 分間浸漬し、純 水リンスの後、直ぐに MBE 装置の真空チ ャンバーに投入した。低温 MBE 法を用い て bcc-金属の Fe3Si, Co20Fe80, Co60Fe40 若しくは Co75Fe25 をそれぞれ 25 nm ずつ 堆積した。これらを電子線リソグラフィ 一法及び Ar+イオンミリング法を用いて 縦型構造の素子(接合面積: S = ~100 μm²) に加工し、縦方向の電流(I) - 電圧(V)特性 を測定した(図 4)。

図 4. 作製した縦方向電気伝導測定素子の模式図。

- c-Geの形成 (GIC法, ~250 °C).

- c-Geの薄膜化 (CMP法, 室温).

- Geチャネルの形成 (ウェットエッチング, 室温).

- Hf S/D電極の形成 (スパッタ法, 300 °C).

- ◆ Ge表面酸化とSiO₂保護層堆積 (ECRプラズマ法, 室温).

- ♦ Al₂O₃膜の堆積 (ALD法, 300 °C).

- ◆ TiNゲート電極の形成 (スパッタ法, 300 °C).

図 5. 本研究で用いた薄膜トランジスタ構造のプロセスフロー。

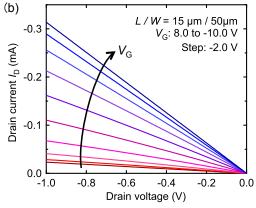

(3) GIC 法によりガラス基板上に成長した結晶性 Ge 薄膜(成長温度: 250  $^{\circ}$ C)を、図 5 のようなプロセスを用いて TFT 構造に加工した。本プロセスは、フレキシブル基板の軟化温度よりも低い 300  $^{\circ}$ C以下で行った。このデバイスを用いて、ドレイン電流( $I_D$ ) - ドレイン電圧( $V_D$ )特性を測定した。

#### 4. 研究成果

(1) 図 6(a)に、T = 150 K における I = 1.0mA のときの 4 端子非局所磁気抵抗測定 の結果を示す。ここでマゼンタ色及び緑 色の曲線は、それぞれ、負方向から正方 向へ、及び正方向から負方向へ Bin を掃引 したときの $\Delta R_{\rm NL}$ と $B_{\rm in}$ の関係である。 $\Delta$  $R_{\rm NL}$  は、 $B_{\rm in}$  の掃引方向に依存して明瞭な ヒステリシス曲線を描いており、Ge 中で のスピン注入・伝導を示唆する CFS 電極 の磁化配置に対応したスピンバルブ信号 を得ることに成功した。その信号の大き さは約  $100 m\Omega$ にも達しており、同じ温 度で観測されている Fe/MgO トンネル接 合電極③のスピンバルブ信号よりも1桁近 く大きい。これは、本研究の CFS 電極の スピン注入・検出効率が、Fe/Mg トンネ ル接合電極<sup>③</sup>や Fe<sub>3</sub>Si 電極<sup>④</sup>のそれよりも 高いことを示唆する結果である。次に、 図 6(b)に 4 端子ハンル効果測定の結果を 示す。ここで青円及び赤円は、CFS 電極 の磁化配置がそれぞれ、平行(↑↑)及び反 平行( $\uparrow\downarrow$ )のときの $\Delta R_{\rm NL}$ と $B_{\rm out}$ の関係を 示している。CFS 電極の磁化配置(平行・ 反平行)に対応して、 $\Delta R_{\rm NL} = 0$ の軸に対 称な上向き及び下向きのハンル信号が観 測されている。この信号は、Ge チャネル 中を伝導しているスピンが Bout により歳 差運動していることを示唆しており、 $T \ge$ 150 K での観測は本研究が初めてである。 この結果を一次元拡散モデルにより解析 したところ、CFS 電極のスピン生成効率 は~0.12と算出され、これまでに報告のあ る Fe/MgO トンネル接合電極のそれより も二桁近く高い値を有していることが

図 6. CFS 電極を有した横型スピンバルブ素子を用いて測定した(a) 4 端子非局所磁気抵抗測定及び、(b) 4 端子ハンル効果測定の結果。

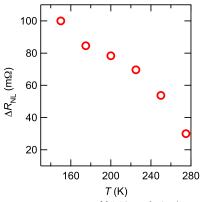

わかった。そこで、 $\Delta R_{\rm NL}$ の温度特性を調 べ、スピンバルブ信号の温度依存性を図7 にまとめた。スピンバルブ信号は温度の 上昇とともに単調に減少しているものの、 なんと  $T \ge 275 \text{ K}$  まで観測されることがわ かった。これは、これまでに報告されて いる Ge 中におけるスピン注入及び伝導の 電気的な検出として世界最高の温度であ る。即ち研究代表者は、スピン注入・検 出効率が高い CFS 電極を用いることによ り、Ge チャネル中におけるスピン注入・ 伝導の電気的な検出の検出温度を大きく 上昇させることに成功した。この成果は、 次世代 LSI の構成素子として期待される Geスピン MOSFET の創製に欠かせない強 磁性 S/D の開発を飛躍的に推進させる成 果である。

図 7. スピンバルブ信号の大きさ $\Delta R_{\rm NL}$  と 測定温度 Tの関係。

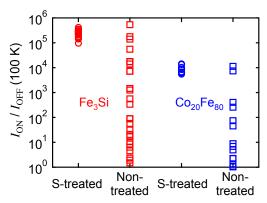

図 8. Fe<sub>3</sub>Si/p-Ge 構造(赤)及び Co<sub>20</sub>Fe<sub>80</sub>/p-Ge 構造(青)における(NH<sub>4</sub>)<sub>2</sub>S トリートメントを行った素子( $\bigcirc$ )と行っていない素子( $\bigcirc$ )の T=100 K の  $I_{\rm ON}/I_{\rm OFF}$ 比

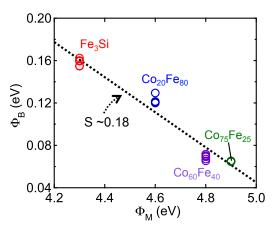

(2) Fe<sub>3</sub>Si/p-Ge 構造(赤)及び Co<sub>20</sub>Fe<sub>80</sub>/p-Ge 構造(青)について、S トリートメントを行っ た素子( $\bigcirc$ )と行っていない素子( $\square$ )の T=100K における  $I_{ON}/I_{OFF}$  比を図 8 にまとめた。 Fe<sub>3</sub>Si/p-Ge 構造及び Co<sub>20</sub>Fe<sub>80</sub>/p-Ge 構造のど ちらにおいても、(NH<sub>4</sub>)<sub>2</sub>S トリートメントを 行っていない素子では Ion/IoFF 比の値がそれ ぞれの素子間で大きくばらついているが、S トリートメントを行った素子では Ion/Ioff 比 の値が高い値で収斂することがわかった。こ こには載せていないが、同様の現象は Co<sub>60</sub>Fe<sub>40</sub>/p-Ge 構造及び Co<sub>75</sub>Fe<sub>25</sub>/ p-Ge 構 造においても観測された。高い値の  $I_{ON}/I_{OFF}$ 比は FLP 現象が緩和していることを示唆し ており、これらの結果は、原始整合した bcc-金属/Ge(111)接合による FLP 緩和効果の安 定性が(NH<sub>4</sub>)<sub>2</sub>Sトリートメントによって向上 されたことを示唆している。 IoFF の温度特性 から熱電子放出伝導の理論式<sup>®</sup>を用いて Φ<sub>B</sub> を算出し、各金属材料の  $\Phi_{\rm M}$  でまとめた(図 9)。 $\Phi_B$ の値は各々の金属材料ごとに収斂して おり、且つ  $\Phi_{\rm M}$ の増大とともに単調に減少し ていることがわかる。そこで、FLP の強さの 指標となる  $\Phi_{\rm B}-\Phi_{\rm M}$  の傾きの大きさ、いわ ゆるSパラメータを、図9のグラフから直線 フィッティングを行うことにより求めた(図 9の破線)。このSパラメータは $0 \le S \le 1$ の 値をとり、0に近いほど FLP の影響が強く、 1に近いほどFLPの影響が弱いことを意味し ている。直線フィッティングの結果から、S パラメータの値は  $S \sim 0.18$  と算出され、 FLP の緩和を明瞭に示唆する結果を得るこ とに成功した。これまで金属/p-Ge 直接接合 におけるSパラメータの算出は本研究以外に 報告例がなく、(NH<sub>4</sub>)<sub>2</sub>S トリートメントによ って様々な bcc-金属材料で FLP 緩和効果を 安定的に得られた結果、S > 0 という値が得 られたものと考えられる。この成果は、次世 代の半導体チャネル材料として期待されて いる Ge と金属材料との接合界面の電気伝導 特性を制御する上で、新しい制御技術方法を 提案する画期的な成果である。

図 9. S トリートメントした素子のショットキー障壁高さ $\Phi_B$  と金属の仕事関数 $\Phi_M$  の関係。

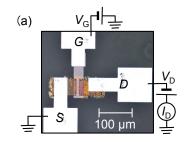

(3) 図 5 のような作製フローに従って加工 した Ge-TFT 構造のノマルスキー顕微鏡写真 を図 10(a)に示す。図のような電流-電圧配置 において、ゲート電圧(V<sub>G</sub>)を変調させながら  $I_{\rm D} - V_{\rm D}$ 特性を測定した(図 10(b))。 $V_{\rm G} = 8.0$ ~ -10.0 V の範囲において、 $V_G$ の減少とともに チャネルコンダクタンスが明瞭に上昇して おり、p型トランジスタ動作を明瞭に観測す ることに成功した。即ち石英基板上ではある が、結晶性 Ge の成長から含めて全て30 0 ℃以下というフレキシブル基板の軟化温 度よりも低い温度でp型の結晶性 Ge-TFT を 作製することに成功した。この成果は、フレ キシブルシステムインディスプレイを実現 する上で欠かせない高速 TFT の低温作製技 術の開発として第一歩となる重要な成果で ある。

図 10. (a)作製した Ge-TFT 構造素子の / マルスキー写真と(b)その  $I_D$ ・ $V_D$  特性。

## <引用文献>

- 国際半導体技術ロードマップ 2013 年版, http://semicon.jeita.or.jp/STRJ/ITRS/2013/

- ② S. Sugahara and M. Tanaka, Appl. Phys. Lett. **84**, 2307 (2004).

- ③ Y. Zhou et al., Phys. Rev. B 84, 125323 (2011).

- 4 K. Hamaya et al., J. Appl. Phys. 113, 183713 (2013).

- (5) T. Kimura *et al.*, NPG Asia Materials **4**, e9 (2012); K. Hamaya *et al.*, Phys. Rev. B **85**, 100404(R) (2012).

- 6 T. Nishimura et al., Ext. Abs. SSDM 2006, 400 (2006); T. Nishimura et al., Appl. Phys. Lett. 91, 123123 (2007).

- K. Kasahara et al., Phys. Rev. B 84, 205301 (2011).

- 8 J.-H. Park et al., Appl. Phys. Lett. 103, 082102 (2013).

- ① D. Lee et al., Jpn. J. Appl. Phys. 51, 04DA06 (2012).

- S. M. Sze, Physics of Semiconductor Devices, 2nd ed. (Wiley, New York, 1981).

#### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

# 〔雑誌論文〕(計 4件)

- ① <u>笠原健司</u>,他5名,"Greatly enhanced generation efficiency of pure spin currents in Ge using Heusler compound Co<sub>2</sub>FeSi electrodes", Applied Physics Express, Vol. 7, pp. 033002-1 033002-4, 2014,査読あり.

- DOI: 10.7567/ APEX.7033002

- ② <u>笠原健司</u>,他6名, "Reliable reduction of Fermi-level pinning at atomically matched metal/Ge interfaces by sulfur treatment", Applied Physics Letters, Vol. **104**, pp. 172109-1 172109-4, 2014,査読あり.

- DOI: 10.1063/ 1.4875016

4

- 3 パクジョンヒョク, <u>笠原健司</u>, 他 3名, "High carrier mobility in orientation-controlled large-grain (≥ 50 µm) Ge directly formed on flexible plastic by nucleation-controlled gold-induced-crystallization", Applied Physics Letters, Vol. **104**, pp. 252110-1 252110-4, 2014, 査読あり. DOI: 10.1063/1.4885716

- 東英実, 笠原健司, 他 9 名, "A pseudo-

single-crystalline germanium film for flexible electronics", Applied Physics Letters, Vol. **106**, pp. 041902-1 – 041902-5, 2015, 査読あり. DOI: 10.1063/1.406612

〔学会発表〕(計 7件)

- ① <u>笠原健司</u>, 他 5 名, "Co<sub>2</sub>FeSi ホイスラー合金電極を用いた n型 Ge 中のスピン 伝導検出", The 18th Symposium on the Physics and Applications of Spinrelated Phenomena in Semiconductors, 2013 年 12 月 9 日~ 10 日, 大阪府.

- ② 朴ジョンヒョク, 笠原健司, 他3名, "層交換法による大粒径 Ge 結晶/プラスチックの直接成長 -フレキシブル基板上における高移動度の実現-",第61回応用物理学会春季学術講演会,2014年3月17日~20日,神奈川県.

- ③ 藤田裕一, <u>笠原健司</u>, 他 4 名, "High efficient detection of pure spin currents in *n*-Ge using *L*2<sub>1</sub>-Co<sub>2</sub>FeSi Heusler-compound electrodes", 第 61 回応用物理学会春季学術講演会, 2014年 3 月 17 日 ~ 20 日, 神奈川県.

- ④ <u>K. Kasahara</u>, 他 5名, "Generation and detection of pure spin current in *n*-Ge using *L*2<sub>1</sub>-ordered Co<sub>2</sub>FeSi electrodes", Intermag 2014, 2014年5月4日~8日, Dresden.

- ⑤ 東英実, <u>笠原健司</u>, 他 9 名, "フレキシブル基板上への擬似単結晶 Ge 薄膜の形成", 第62回応用物理学会春季学術講演会, 2015 年 3 月 11 日 ~ 14 日, 神奈川県.

- ⑥ 中野茉莉央, 東英実, 笠原健司, 他3名, "金誘起層交換成長法で作製した擬似単 結晶 Ge の電気伝導特性", 第62回応用 物理学会春季学術講演会, 2015年3月 11日~14日, 神奈川県.

- ⑦ <u>笠原健司</u>,他 7名,"300 ℃以下プロセスで作製した結晶性 Ge チャネル TFT",第 62 回応用物理学会春季学術講演会,2015年3月11日~14日,神奈川県.

〔図書〕(計 0件)

[産業財産権]

- ○出願状況(計 0件)

- ○取得状況(計 0件)

〔その他〕 ホームページ等 なし

- 6. 研究組織

- (1)研究代表者

笠原 健司 (KASAHARA, Kenji) 九州大学・大学院システム情報科学研究院 ・特任助教 研究者番号:00706864

- (2)研究分担者 なし

- (3)連携研究者 なし