### 研究成果報告書 科学研究費助成事業

6 月 15 日現在 平成 30 年

機関番号: 12601

研究種目: 基盤研究(B)(一般)

研究期間: 2014~2017

課題番号: 26280012

研究課題名(和文)レジリエンス指向コンピュータシステムに関する研究

研究課題名(英文) Research on Resilience-Oriented Computer Systems

### 研究代表者

坂井 修一(Sakai, Shuichi)

東京大学・大学院情報理工学系研究科・教授

研究者番号:50291290

交付決定額(研究期間全体):(直接経費) 13,200,000円

研究成果の概要(和文):情報社会の飛躍的発展の中で、ITシステムの信頼性・安全性をこれまでより高い水準で確保することは喫緊の課題である。本研究では、ITシステムに故障や侵入があった場合でも、被害を最小限に食い止め、正常動作を続けさせるか、最小限のオーバヘッドで機能回復をする技術の研究開発を行った。具体的には、タイムボローによる遅延隠蔽、オンデマンドの細粒度部分再構成、ストリーム指向の防御、実時間的な異常予知などの新しい要素技術を提案・検証し、さらにこれらを統合して効率的に動作させるレジリエンス指向コンピュータを検討・提案し、テストベッドによってその有効性を示した。

研究成果の概要(英文): Our information society is developing so rapidly that it is a pressing issue to keep the reliability and safety of IT systems at a much higher level than before. In this research, we have developed innovative technologies to minimize the damage and keep the correct operation or to restore functions with minimal overhead even if there is a breakdown or intrusion in the IT system. Specifically, we proposed and verified new element technologies such as delay concealment by time borrow, fine-grained partial reconstruction on demand, stream-oriented protection against attacks, real-time abnormality prediction, and integrated them to realize a resilience-oriented computer which efficiently operates all the functions. In addition, we have developed a testbed to prove its effectiveness.

研究分野: 情報システムとその応用

キーワード: レジリエンス 信頼性 安全性 タイムボロー ストリーム指向制御 異常予知 アーキテクチャ 可用性

### 1.研究開始当初の背景

第4期科学技術基本計画の中では、第3期に引き続いて「安全、かつ豊かで質の高い国民生活を実現する国」が最重要の基本理念の1つとして据えられている。この理念を実現するためには、情報インフラが「安全・安心」であることが必須であり、このことは、日本だけでなく地球規模で日々その重要性を増している。

情報技術の最も基本にあるのが情報処理 技術と通信網の技術であり、端的にそれはコ ンピュータとインターネットの技術である。 すなわち、「安全・安心なコンピュータとイ ンターネットを構築すること」が、今の情報 技術に最大の課題といってよい。ここでは、 このうち前者の「安全・安心なコンピュータ」 の構築をめざし、アーキテクチャ技術とソフ トウェア技術を中心に研究する。

「安全・安心」は、信頼性・安全性・可用性・堅牢性などの複合したものである。過去においても、コンピュータのこれらの機能を向上させることは重要なテーマであり、を向上させることは重要なテーマであり、信息とが図られてきたが、(1)ソフトクェアの複雑化とブラックボックス化、(2)ゲート規模の爆発的増加によるLSIの複雑化、(3)ネット社会の急激な進展による攻撃のウウト規模の影響の増大、(4)通信やソフト文化の浸透、の4点によって、近年になって、の浸透、の4点によって、近年になっている。に問題が複雑化・大規模化・多様化している。

このような現状を受けて、国内外の多く の研究機関で、コンピュータの信頼性や安全 性をアーキテクチャ技術・ソフトウェア技術 によって向上させる試みがなされている。代 表例を示せば、(1)タイミング故障耐性を向上 させるミシガン大学の Razor や九州大学の Canary、(2)タンパ耐性をもつアーキテクチ ャとしてスタンフォード大学の XoM、MIT の AEGIS、東芝 L-MSP、(3)アタック耐性を もつアーキテクチャとして MIT の DIFT、プ リンストン大学の RIFLE、九州大学の実行監 視方式、(4)インジェクションアタックを防ぐ 方式としてのスタンフォード大学の Raksha などがこれである。これらは、プログラムレ ベルやスレッドレベル、命令レベル、アーキ テクチャレベルにおいて信頼性・安全性を向 上させる優れた要素技術を提案しているが、 故障や侵入を完全に防ぐことができるわけ ではなく、万が一に故障や侵入があった場合、 被害を最小限に食い止めたり、最小限のオー バヘッドで機能回復したりすることが十分 に考えられているわけではない。

研究代表者は、コンピュータのアーキテクチャおよびソフトウェアを中心課題として、30年以上に渡って研究を行ってきた。1980年代から今日まで、研究代表者は、マイクロプロセッサの効率化・省電力化の研究を行い、データフロー方式の改良、大規模データパスプロセッサの提案・評価、スーパス

カラ方式の究極的高性能化、省電力チップマルチプロセッサのアーキテクチャおよび最適化コンパイラの提案などの研究開発を行った。提案したマイクロプロセッサは、実際に EMC-R、RICA-1 など VLSI チップ上に実装され、あるいは詳細レベルのシミュレーション評価によって高い効率が検証された。成果は国内外で高い評価を得ており、IEEE Outstanding Paper Award、日本 IBM 科学賞など、多数の賞を受賞している。

以上の研究を通じて高性能で低消費電力のコンピュータの研究開発を行い、高性能・省電力コンピュータアーキテクチャの確立という点で大きな成果をあげたが、一方で性能、消費電力、信頼性・安全性の3者はトレードオフの関係になることが多く、性能と消費電力の2つだけを扱うことの限界を認識せざるをえなかった。結果として、コンピュータにおける信頼性・安全性の研究の必要が痛感されたのであった。

2000 年代に入り、以上の成果をふまえ、 また上記(1)(2)(3)(4)で述べた問題認識のもと に、性能・省電力と並ぶ第三の軸として、信 頼性・安全性について特に深く研究すること となった。具体的には、JST CREST プロ ジェクト「ディペンダブル情報処理基盤」(申 請者が代表)において、プロセッサアーキテ クチャ、OS、応用ソフトウェアまでのセキュ リティおよび信頼性の基本技術を研究開発 した。本プロジェクトによって、近未来の IT に必要な高信頼化・高い安全化技術が新規に 提案され一部検証された。この成果を受けて、 JST CREST プロジェクト「アーキテクチ ャと形式的検証の協調による超ディペンダ ブル VLSI (申請者が代表) において、高信 頼化の研究を進める(2007年10月~2012年 9月)とともに、STARC 共同研究「超ディペ ンダブルプロセッサの研究」(2007年4月~ 2010年3月)、科研基盤(B)「超セキュアプ ロセッサに関する研究」(2010年4月~2013 年3月)において、マイクロプロセッサのセキ ュリティを飛躍的に向上させる研究を行っ た。これらにおいて、タイミング故障、永久 故障、インジェクション攻撃などに高い耐性 をもつコンピュータの新規提案・評価検証を 行い、国内外での論文発表や国際特許などの 成果をあげた。一方で、故障や攻撃への「完 全な防御」は不可能であり、従来の防御や緩 和技術に加えて、故障や侵入があった場合で も、被害を最小限に食い止め、正常動作を続 けさせるか、最小限のオーバヘッドで機能回 復する技術の研究開発が重要であることを 痛感した。

### 2. 研究の目的

本研究では、IT システムに故障や侵入があった場合でも、被害を最小限に食い止め、正常動作を続けさせるか、最小限のオーバヘッドで機能回復する技術の研究開発を行う。 従来、故障対策は多重化によるものが、攻撃 対策はパターンマッチによる侵入検知と暗 号化によるものが主流であった。本研究では、 予測・検知が困難でこれまでは防ぐことが困 難であった故障や攻撃に耐性のあるコンピュータシステムの構築をめざす。そのために、 タイムボロー、オンデマンドの細粒度部分再 構成、ストリーム指向の防御、異常予知など の新しい要素技術を提案する。さらに、これ らを統合して効率的に動作させるレジリエ ンス指向コンピュータを検討・提案し、テス トベッドを試作して動作を実証する。

特にここでは、対象を現在最も重要と思 われる(1)タイミング故障、(2)永久故障、(3) インジェクション攻撃、(4)ゼロデー攻撃の 4つに絞って、コンピュータのレジリエンス (耐久力・復元力)を飛躍的に高める技術を 研究開発する。特に、防止・防御がむずかし い故障・攻撃に対して、効率的に縮退運転を する技術や最小限のオーバヘッドで機能回 復をする技術の研究開発を行う。具体的には、 新規要素技術を提案し、プロセッサ・シミュ レータや FPGA 上での実装、ソフトウェア開 発を行って機能を検証し、あわせて動作性能 および消費電力についても評価する。その上 で、提案した技術を統合的に扱うための制御 機構を提案し、シミュレーションおよび FPGA などによる実装、ソフトウェアの動作 試験などによって機能を検証する。さらに、 4種類のレジリエンスをもつプロセッサの テストベッド実装と動作検証、性能と消費電 力の全体シミュレーション評価までを行う。

### 3.研究の方法

レジリエンス要素技術として、タイムボローによる遅延隠蔽、オンデマンドの細粒度部分再構成、ストリーム指向の防御、実時間的な異常予知のそれぞれの研究を行い、成果を提案者が開発した詳細シミュレータ「鬼斬

」に新規機能を組み込む、ソフトウェアを 開発するなどして評価し、さらにプロトタイ プ実装などによって実証的に検証する。さら に、これらを統合管理するレジリエンス・マ ネジャの機能・機構を明らかにし、レジリエ ンス指向コンピュータの全体を設計する。コ ンピュータの中心となるプロセッサについ ては、「鬼斬 」を改良する形で詳細シミュ レータを作成し、FPGA テストベッドによる実 装を行い、さらに必要に応じて VDEC などを 使ったカスタム VLSI 実装を行う。最後に、 スタンドアロンな情報システムとしてのレ ジリエンス指向コンピュータの動作検証、達 成される信頼性・安全性の検証、実行効率測 定、消費電力測定などを行い、本研究成果の 有効性を検証する。

### 4. 研究成果

# 4.1 タイミング・フォールトの緩和

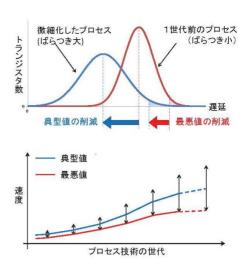

VLSI のワーストケース設計では、素子遅延のばらつきによって、回路本来の実行速度が得られなくなっている(図1)。研究代表者ら

図1. VLSI の世代と遅延の典型値・最悪値

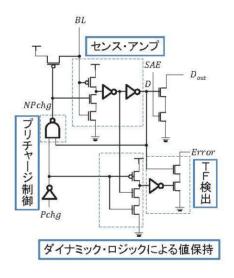

図2.提案手法の回路実装

は、ワーストケースではなく、実際の回路遅延に基づいた動作の実現を目的として、新しいクロッキング方式を提案、これを検証してきた。

本科研費の研究では、以下のことを行った。

# (1) ダイナミック・ロジックへの動的タイミ ング・フォールト検出手法の適用

ダイナミック・ロジックでは、プリチャージ動作がタイミング・フォールトをは適用であため、従来のフォールト検出手法は適用できない。そこで、ダイナミック・ログラーを制御することによって、検出手法の適用を制にする提案を行った(図2)。そして、本提案を適用したレジスタファイルをトランジスタ・レベルで設計し、SPICEシミュレータ・レベルで設計し、SPICEシミュレーを検出できることを確認した。

(2) 動的タイム・ボローイングを可能にする

クロッキング方式のための二相ラッチ生 成アルゴリズム

研究代表者らの提案するクロッキング方式を、具体的なディジタル回路に適用する手法について、二相ラッチ化のアルゴリズムを提案した。

二相ラッチ化の要件は、全てのパスに逆相ラッチがそれぞれ1つだけ挿入されていることである。二相ラッチ化の目標は、挿入スの逆相ラッチの数を少なくすることと、パスるの遅延ができるだけ二分されるように立らとである。二相ラッチ化のアルゴリズムることである。二相ラッチが挿入されるとでパスをイテレートして挿入対象本をを探索することで二相ラッチを挿入するのにさせる。また、各逆相ラッチを挿入するのにコストが必要だとみなして、コストの総理が最小となるものを探索することで、目標達成をはかる。

本アルゴリズムを、規模の異なるキャリルックアヘッドに適用した結果、効率良く二相ラッチ化回路が生成されることが示された。

本アルゴリズムは、回路素子の静的解析を 用いるなどの改良によって、さらに良い回路 を効率的に生成することが可能になった。さ らに、積和回路に改良アルゴリズムを適用し、 効果を確認した。

アルゴリズムのさらなる改良、より複雑な 回路への適用などが今後の課題となってい る。

### 4.2 ストリーム指向の攻撃検知・防御

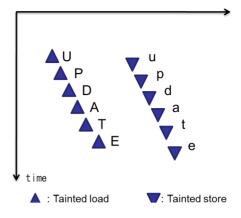

IT システムへの様々な攻撃を検知・防御するための機構として、文字列操作単位でテイント伝播を追跡する手法である SWIFT を考案している(図3)。本科研費の研究では、SWIFT について以下のことを行った。

# (1) SWIFT によるゼロデイアタック検出

SWIFTの実現例であるPHP-SWIFTについて、ゼロデーアタックなどの未知の攻撃に対して適応できるかどうかの評価を行った。最初に、WordPress 上に SQL インジェクションに対する脆弱性のある環境を再現し、攻撃を仕掛けることで評価を行った。その結果、SWIFTの機構は有効に機能し、多くの場合でゼロディアタックの検出に成功した。一方で、SWIFTでも防ぐことができなかった攻撃も発討がでも防ぐことができなかった攻撃も発討が必要であることがわかり、改良を進めている。また、ディレクトリ・トラバーサルやクロスサイト・スクリプティングに対しても耐性をもつかどうか、現在研究中である。

(3) Android におけるプロセスベースのテイント伝播を用いた個人情報漏洩検知システム

近年、スマートフォンにおける個人情報漏 洩の被害が急増しているため、これを防ぐ対 策が喫緊の課題となっている。ここでは、プ address

図3.SWIFT の原理図

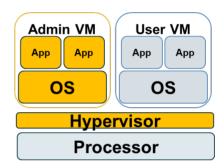

図4 WM セキュアプロセッサ概念図

図 5 Sharkcage の構成

ロセスベースのテイント伝播情報を SELinux に組み込むことにより、ユーザ空間の脆弱性にかかわらず、オーバヘッドをほとんど生じない OS レベルでの個人情報流出検知システムを提案し、評価を行った。その結果、個人情報の流出をきちんと検知できること、オーバヘッドもほぼ生じないことが確認された。

### 4.3 セキュアプロセッサ

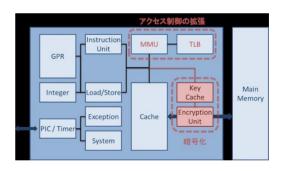

セキュリティ機能をアーキテクチャレベルでもつプロセッサをセキュアプロセッサと呼ぶ。これに関して本科研費を用いて、以下の研究を行った。

(1) ユーザ VM を守るプロセッサアーキテク チャの研究 クラウド環境で悪意の第三者からユーザデータを守る VM セキュアプロセッサSharkcage を考案し(図4) そのアーキテクチャを提案(図5) 設計によってその有効性を検証した。Sharkcage では、ユーザ VM 全体が保護されるため、外部からはもとより、管理 VM などシステムの内側からの攻撃に対してもユーザデータが守られる。

# (2) クラウドフォレンジックに向けた VM セ キュアプロセッサ

クラウドコンピューティングの普及に伴い クラウドフォレンジックの需要も増してい るが、クラウドフォレンジックは通常のフォ レンジックと比べて効率面やセキュリティ 面で課題が多い。研究代表者らは、そのよう なクラウドフォレンジックの課題を解決す るために、ハードウェアによるログファイル 管理に注目した。特にログファイルの機密性。 完全性・真正性を確保するために、暗号化や ハッシュ値・電子署名生成機能を組み込んだ VM セキュアプロセッサの開発を進めている。 本科研費の研究では、クラウドフォレンジッ クの課題を解決するために VM セキュアプロ セッサを導入したログファイル管理システ ムの提案を行い、それに必要な VM セキュア プロセッサの設計と実装を進めた。評価の結 果、従来のソフトウェアベースのフォレンジ ック手法よりも強固かつ効率的であること が示された。

# (3) セキュアプロセッサにおける楕円曲線暗号の評価と実時間的な異常検知

セキュアプロセッサではユーザプロセスの認証のために電子署名を使うが、そのさいに公開鍵暗号が使われる。これまで、公開鍵暗号として RSA 暗号が使われてきたが、本研究では、楕円曲線暗号を用い、さらに回路をハードウェア化することで軽量高速な認証が可能となることを、設計・実装による評価によって示した。

本研究によって、実時間的な異常検知についても実現性に向けての一歩を進めることができた。

# (4) セキュアプロセッサを用いたマルチプロ セッサシステムの設計

セキュアプロセッサは暗号化機構と完全性検証機構によってデータを保護するが、現状ではその普及が進んでいるとは言えない。この理由の1つに、セキュアプロセッサがマルチプロセッサ環境に対応していないことのよるパフォーマンスの低下が挙がられる。本科研費による研究では、セキュアプロセッサを用いてマルチプロセッサシステムを構り、その設計を行った。その結果、本システムは現実的なコストで実装でき、十分なパフォーマンスが得られることが検証された。

# (5) セキュアプロセッサ利用環境における DMA の実現手法

セキュアプロセッサの利用環境下では、信頼性担保のため、従来の外部デバイスによるDMA(Digital Memory Access)を適用することができない。本研究では、信頼できる外部デバイスの存在を仮定し、本来のDMAに期待されるプロセッサからの負荷のオフロードとデータの秘匿性・完全性を両立したDMAを実現するためのモデルを提案し、設計・評価して脆弱性のないDMAが実現されることを検証した。

### 4.5 全体統合

全体統合のベースとして、従来のスーパスカラ・アーキテクチャを軽量・高速化した新しいアーキテクチャを提案、シミュレーションと FPGA 実装によって、電力性能比などにおける有効性を検証した。

さらにこのベース・プロセッサにセキュリティ機構を導入し、VM セキュアプロセッサ Sharkcage を設計した。

タイムボロー方式によるクロッキングは、 実際にこれをカスタムチップとして設計す るときに用いることができる。

ストリーム指向のテイント追跡技術を組み込んだ PHP-SWIFT は汎用ソフトウェアであり、PHP 処理系のあるプロセッサであれば、これを動作させられる。

# 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

### [雑誌論文](計4件)

<u>坂井 修一</u>:情報社会と人間,サイバースペースとセキュリティー 第 5 回,情報管理: Vol. 59 No. 11 p. 768-771 (2017).

Junji YAMADA, Ushio JIMBO, Ryota SHIOYA, Masahiro GOSHIMA, and Shuichi SAKAI: Skewed Multistaged Multibanked Register File for Area and Energy Efficiency, IEICE TRANS. INF. & SYST., VOL.E100-D, NO.4 pp.822-837, (2017) MinSeong Choi, Masahiro Goshima and Shuichi Sakai: An Inductive Method to Select Simulation Points, IEICE Transactions on Inforamtion and Systems, E99-D(12), pp. 2891-2990 (2016)

Naruki KURATA, Ryota SHIOYA, <u>Masahiro GOSHIMA</u>, <u>Shuichi SAKAI</u>: Address Order Violation Detection with Parallel Counting Bloom Filters, IEICE Transactions on Electronics Vol. E98.C, No. 7, pp. 580-593 (2015).

### [学会発表](計 18 件)

甲地 弘幸,入江 英嗣,坂井 修一:プリ

フェッチラインの再参照間隔を予測する キャッシュマネジメント 情報処理学会 研究報告 2017-ARC-227, No. 12, pp. 1 -8 (2017)

谷合 廣紀, 宮永 瑞紀, <u>入江</u>英嗣, <u>坂</u>井 <u>修一</u>: セキュアプロセッサにおける 楕円曲線暗号の評価, 情報科学技術フォ ーラム講演論文集, No. 4, CL-004 (2017).

<u>入江 英嗣</u>: コンピュータを作る,使う,情報科学技術フォーラムイベント企画「東大・情報理工研究 100 連発 ~電子情報学専攻編~」 (2017).

<u>坂井 修一、入江 英嗣</u>: 未来のコンピュータ, 未来のコンピューティング, 情報 科学技術フォーラム展示会 (2017).

島田 伸夫,谷合 廣紀,宮永 瑞紀,<u>入江</u> <u>英嗣,坂井 修一</u>: 侵入検出手法 SWIFT によるゼロデイアタック検出, 信学技 報,vol.116,no.510,CPSY2016-149,pp. 321-326 (2017).

鈴木 璃人,梶原 拓也,宮永 瑞紀,<u>入江</u> <u>英嗣</u>,<u>坂井 修一</u>: セキュアプロセッサ 利用環境における DMA の実現手法, 信 学 技 報 , vol. 116, no. 510, CPSY2016-138, pp. 39-44, (2017).

Mizuki Miyanaga, <u>Hidetsugu Irie</u>, <u>Shuichi Sakai</u>: Accelerating Integrity Verification on Secure Processors by Promissory Hash, 2017 IEEE 22nd Pacific Rim International Symposium on Dependable Computing (PRDC), pp. 22-29 (2017)

梶原 拓哉, 宮永 瑞紀, <u>入江 英嗣</u>, <u>坂</u>井 修一: セキュアプロセッサを用いたマルチプロセッサシステムの設計, 電子情報通信学会技術研究報告, Vol.116, No. 240, pp. 7-10 (2016)

西川 卓,塩谷 亮太,<u>入江 英嗣</u>,五島 正裕,坂井 修一: フィルタを用いたメ モリ・アクセス順序違反検出手法の評価, 情報処理学会研究報告, Vol. 2016-ARC-219, No. 15, pp. 1-6 (2016) 津坂章仁,谷川祐一,広畑壮一郎, 五島正裕,入江英嗣,坂井修一:動 的タイム・ボローイングのための二相化 アルゴリズムの改良と評価,電子情報 通信学会技術研究報告,Vol. 115, No. 518, pp. 133-138 (2016).

千田 拓矢,谷合 廣紀,宮永 瑞紀,入 江 英嗣,坂井 修一: クラウド フォレ ンジックに向けた VM セキュアプロセッ サの設計と実装,電子情報通信学 会技 術 研 究 報 告, Vol. 115, No. 518, CPSY2015-143, pp. 115-120 (2016). 今田 丈雅,宮永 瑞紀,入江 英嗣,坂

今田 丈雅, 宮永 瑞紀, <u>入江 英嗣</u>, 坂井 修一: Android におけるプロセスベースのテイント伝搬を用いた個人情報の漏洩を検知するシステム,電子情報通信学会総合大会, A-7-3, pp.89 (2016)

西川 卓,塩谷 亮太,<u>入江 英嗣</u>,<u>五島</u> <u>正裕</u>,<u>坂井 修一</u>: Bloom-like SVW の評 価,電子情報通信学会技術研究報告, Vol. 115, No. 243, pp. 27-34 (2015).

西川 卓,塩谷 亮太,<u>入江 英嗣</u>,<u>五島</u> <u>正裕</u>,<u>坂井 修一</u>:メモリ・アクセス順序 違反検出手法の評価,電子情報通信学会 技術研究報告 信学技報 ,No.115(174), pp.21-29 (2015).

神保 潮, 五島 正裕, 坂井 修一: タイミング・フォールト検出手法の RAM への適用,情報処理学会研究報告 2015-ARC-214, No. 8, pp. 1-8 (2015).

酒井 一憲,津坂 章仁,神保 潮,<u>五島 正裕,坂井 修一</u>: 回路素子の静的解析を用いた二相化アルゴリズムの改良,情報処理学会第77回全国大会論文集,No.1,pp.77-78 (2015).

神保 潮, 山田 淳二, 五島 正裕, 坂井 修一: ダイナミック・ロジックへのタイ ミング・フォールト検出手法の適用、情 報処理学会研究報告 2014-ARC-210, No. 18, pp. 1-8 (2014).

# [その他]

ホームページ

http://www.mtl.t.u-tokyo.ac.jp/

### 6. 研究組織

### (1)研究代表者

坂井 修一 (Sakai Shuichi)

東京大学・大学院情報理工学系研究科・教

研究者番号: 50291290

### (2)研究分担者

五島 正裕 (Goshima Masahiro) 東京大学・大学院情報理工学系研究科・准 教授(当時)

研究者番号: 90283639

入江 英嗣 (Irie Hidetsugu)

東京大学・大学院情報理工学系研究科・准 教授

研究者番号: 50422407