# 科研費

# 科学研究費助成事業 研究成果報告書

平成 29 年 6 月 1 日現在

機関番号: 11101

研究種目: 基盤研究(C)(一般)

研究期間: 2014~2016

課題番号: 26330057

研究課題名(和文)シリコン貫通ビアを用いた三次元集積回路の物理配線設計に関する研究

研究課題名(英文)A Study on Physical Interconnect Design in 3D ICs Using Through Silicon Vias

#### 研究代表者

黒川 敦 (Kurokawa, Atsushi)

弘前大学・理工学研究科・教授

研究者番号:80610592

交付決定額(研究期間全体):(直接経費) 3,600,000円

研究成果の概要(和文):研究成果の概要は以下の通りである。1) 三次元集積回路の配線RLCを様々な条件下で電磁界解析し、各RLCの値を明らかにし、幾つかの容量式を開発した。2) 伝搬遅延時間とクロストークノイズを回路解析し、基板コンタクトの効果を明らかにし、遅延やノイズを簡単に求める式を開発した。3) 従来のシングルチップと同様に、クロック分配設計ができるクロック分配方法を開発した。4) 電源分配をモデル化して電源電圧効果を解析により明らかにした。5) 様々な条件の熱分布を熱電導解析により明らかにし、温度抑制技術として積層チップの側壁を囲む方法とチップ間にプレートを挿入する方法を開発した。

研究成果の概要(英文): The summaries of research results are as follows. 1) Interconnect resistance, inductance and capacitance under various conditions in 3D ICs were analyzed by an electromagnetic solver, values of each RLC were clarified, and several capacitance equations were developed. 2) The propagation delay and crosstalk noise were analyzed with a circuit simulator, effect of substrate contacts on delay was clarified, and equations to easily get the delay and noise were developed. 3) A method to reduce clock skew among stacked chips by a clock distribution network with multiple source buffers was developed. 4) The power distribution network was modelled and the voltage drops were clarified by circuit simulations. 5) The thermal distribution in 3D ICs was clarified by a thermal conductivity analyzer and new cooling architectures using thermal sidewalls, interchip plates, and a bottom plate (thermal-SIB architectures) were developed.

研究分野: 集積回路設計技術

キーワード: 三次元集積回路 貫通シリコンビア クロック分配 熱解析

#### 1.研究開始当初の背景

近年、三次元集積回路が世界中で活発に研 究され、中でもシリコン貫通ビア(TSV: Through Silicon Via ) を用いた積層は、近未 来の最も有効な手段となってきている。TSV を用いた三次元化は特殊な製造・組立が必要 なことから、研究の焦点がほとんど製造・組 立技術に当てられてきた。最近、ようやく製 造と組立の方向性が定まりつつあり、効果的 な設計が可能になりつつある。メモリだけの 積層は一部商用化されるようになったが、メ ニーコア (10 個以上の CPU) や制御用の口 ジック回路では製品化に至っていない。ロジ ック系積層の物理配線に関する研究報告は まだ少ない状況である。複数チップを積層し た本来の小型軽量・多機能・高性能な三次元 集積回路の実現が望まれている。

三次元集積回路が脚光を浴びるようになってきたが、三次元化の本来の優位性を十分引き出すには、物理配線の設計技術の開発が必要である。従来の単層チップと積層チップの配線はほとんどの部分が共通している層所ップでも配線は三次元であり、多層配線をビアで接続する。しかし、積層チップすると、2)その寸法がチップ内の一般配線よりうと、2)その寸法がチップを接続する縦方の配線の方法によって、電気特性が変動することである。

#### 2.研究の目的

本研究では、三次元集積回路の物理配線における抵抗・インダクタンス・容量(RLC)の値を電磁界解析により定量化し、回路動作に必須な信号伝搬(バス信号、クロック信号)と電源供給の特性を回路解析し、設計に有効な方法を探索する。研究期間内に以下のことを明らかにすることを目的とする。

## (1) 配線 RLC の定量化と効果的な配線 RLC 抽出方法の開発

TSV とチップ間接続及びチップ内多層ビア接続の総合的な配線の RLC の値、TSV に関する配線と周囲の配線と間の容量性及び誘導性結合の値、TSV の形状等のばらつきによる RLC の変動、周波数効果、グラウンド配線を基板コンタクトした際の影響を明らかにする。

さらに、回路動作保証のためのタイミング解析に必要なプロセスばらつきや温度を考慮した配線 RLC の効果的な抽出方法を明らかにする。

# (2) 信号伝搬特性の明確化と効果的なバス信号配線方法の開発

単一信号の伝搬特性と、バス信号伝送のような並走配線における同時スイッチングによる容量性及び誘導性クロストークノイズを明らかにする。さらに、クロストークノイ

ズを電源電圧の 20%以内(単層チップの設計 基準でも厳しい方の数値)に抑制する方法を 明らかにする。

# (3) クロックスキューの明確化と効果的なクロック分配方法の開発

積層チップのクロックツリー方式におけるクロックソース位置とクロックバッファ挿入によるクロックスキューの低減効果を明らかにする。また、新手法として、複数クロック用 TSV を用いたクロックネットワーク方式と、クロックソースに近い配線を明らにしたクロック支線幹線方式の効果を明らかにする。

# (4) 電圧変動の明確化と効果的な電源分配方法の開発

電源・グラウンド用 TSV の配置や配線方法による電源電圧降下、同時スイッチングによる電源・グラウンドの動的ノイズ、デカップリング容量による電源ノイズの低減効果を明らかにする。

#### (5) 熱分布の明確化

チップの消費電力等に基づいた三次元集 積回路の熱分布解析を行い、電源・グラウン ド用 TSV の温度上昇抑制効果を明らかにす る。

## 3.研究の方法

#### (1) 配線 RLC の解析と容量式の開発

三次元電磁界解析ツールを用いて、TSV に関わる配線の RLC を定量的に明らかにする。構造入力は基本的にツールの機能を利用するが、一部詳細な解析では、座標を手入力して構造を作成する。

TSV の寸法(直径、酸化膜厚、高さ) 材質 (TSV の抵抗率、酸化膜の誘電率、シリコン 基板の導電率と誘電率 ) 及び配置(間隔、 スクウェア/千鳥)を変更し、RLCへの影響を 解析する。次に、周波数及びばらつき(例え ば TSV は円錐形や樽型になる場合がある)を 変更し、RLC への影響を調査する。各値の範 囲は「国際半導体技術ロードマップ」や文献 等を参考に、今後の技術の進展も考慮して定 める。TSV の RLC 等価モデルが若干提案され ているが文献により異なる。また、グラウン ドの基板コンタクトの効果が検討されてい ない。これらはシリコン基板を網目状に近似 して、基板コンタクトの位置を変更した解析 を実施することで、モデルの妥当性や基板コ ンタクトの影響を明らかにできる。

TSV は全体の配線の一部であり、接続のためのバックメタルやチップ内配線によって接続される。また、TSV を製造のどの段階で通すか、チップを表裏の順に重ねるか、表と表を向い合せるかにより、配線構造が異なる。さらに、TSV 直上のチップ内配線(もしくは近接配線)は容量性・誘導性結合により影響

を受ける。これらの様々な条件の配線 RLC を解析し、TSV に関わる全ての配線の特徴を明らかにする。

集積回路の設計では、回路動作検証において、寄生抽出より得られた配線のRLCが必要である。精度をできる限り落とさず、高速に抽出する方法を探索する。手順として、まず無視可能な配線構造の境界条件を調査し、考慮すべき配線のばらつきや温度、周波数を考慮した配線RLCの最大/最小を調査し、それらを利用した抽出方法により実現する。また簡易計算用に実験計画法を用いて、配線RLCの解析式の開発も実施する。

#### (2) チップ間バス信号伝搬の解析

TSV の配置、配線構造、信号分配等の異なる条件で、回路シミュレータを用いて信号伝搬特性(遅延時間とノイズ)を解析し、高品質な信号伝搬方法を探索する。

バス信号配線が同時スイッチングした際に、容量性及び誘導性クロストークノイズが大きくなる。回路条件(ドライバの駆動能力、チップ内配線、出力に接続するセル)や TSV 間隔や寸法等を変更し、ノイズへの影響を調査する。電源用 TSV とグラウンド用 TSV の配置を変更し、配置による信号品質の違いも調査する。単一信号と複数信号配線、及び電源・グラウンドの配置を変更して実施する。

#### (3) クロック分配方法の研究

従来の単層チップではクロック分配として、クロックツリーがよく使われる。これを三次元積層に拡張したときのクロックスキュー(到着時間のずれ)への影響について、回路シミュレータを用いて解析する。サブクロック用 TSV の利用が文献で提案されたが具体的な方法は提示されていない。本研究ではスキュー低減手法として、ツリーの方法やバッファリングの位置、サブクロック用 TSV の位置を変更し、それらの効果を調査する。

### (4) 電源・グラウンド分配方法の研究

電源・グラウンド分配に関する解析と設計 方法の研究を行う。特性解析には回路シミュ レータを利用する。

チップを積層するに従い、電源電圧降下と グラウンドバウンスが生じる。この電圧変動 を TSV の寸法や配置、チップ積層数、チップ 消費電力、チップ内電源配線、デカップリン グ容量の配置等の条件を変更して解析する。

## (5) 三次元大規模集積回路の熱解析

三次元大規模集積回路の熱解析を実施し、 熱の分布を明らかにする。

温度により、トランジスタ特性や配線抵抗は変動する。チップの消費電力や関連文献を参考に熱源を定め、電磁界解析ツールを用いて、積層数や各寸法、パッケージ等の条件を変更して熱分布を解析する。また、グラウンド配線(グラウンド用 TSV やチップ内グラウ

ンド配線等)方法を変更することによる温度 上昇抑制効果も明らかにする。

#### 4. 研究成果

#### (1) 三次元集積回路の配線寄生素子(RLC)の モデリングと容量式の開発

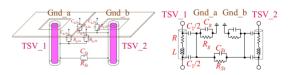

TSV を用いた三次元集積回路における垂直 方向の伝搬遅延に関わる構造として、図1に 示す基盤コンタクトを考慮したモデルと電 気的等価回路を提案した(文献)。チップ 内配線容量(図2(a))の式とバンプ間容量(図 2(b))の式を開発した(文献,)。

$$C_w = \varepsilon l \left( 4 + 2 \frac{t}{w} - 0.43 \frac{h}{w} \right)$$

但し、 $\varepsilon$  は誘電率、l/t/w/h は配線長/厚み/幅/高さである。

$$C_{12} = \varepsilon \left( 0.264 + 0.628 \left( \frac{d}{p} \right) + 1.75 \left( \frac{d}{p} \right)^2 \right) h$$

但し、d/p/h はマイクロバンプの直径/ピッチ/幅/高さである。

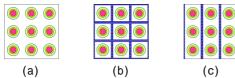

次に、20nm テクノロジ世代以降で使用されるバルクタイプ FinFET に対応するために、標準セル内埋め込み型の場合(細粒度基板コンタクト)と基板コンタクト専用のタップセルを用いる場合(粗粒度基板コンタクト)の物理レイアウトをモデル化し(図3) それぞれに対して容量式を開発した(文献 . )

$$C_X = \varepsilon \left(\beta_0 + \sum_{i=1}^n \beta_i v_i + \sum_{i=1}^n \beta_{ii} v_i^2 + \sum_{i< j}^n \beta_{ij} v_i v_j\right)$$

開発した容量式は電磁界解析を使わず簡単に容量を求めることができる。

さらに、インダクタンス行列の逆行列から TSV 間容量を算出する方法を調査し、多数の TSV が用いられると逆行列計算に膨大な時間 を要するが、規則配置では 4×4 の TSV (16本)配置から逆行列を求めるだけで十分な精度が得られることを見出した(文献 )。

図1 基板コンタクト有りの等価モデル

図 2 (a)チップ内配線と(b)バンプ間容量

図 3 TSV 間容量: (a)基板コンタクト無し、(b) 細粒度基板コンタクト、(c) 粗粒度基板コンタクト

(2) 信号遅延とクロストークノイズ式の開発 垂直方向の伝搬遅延を簡単に見積もれる 式(図4(a))を開発した(文献 , )。

$$\frac{T_d}{T_{d,typ}} = \prod_{i=1}^n f_i(v_i)$$

但し、変数  $v_i$ はチップ基板厚み、TSV 径、バッファサイズ等 13 個から構成される。遅延式は三次元集積回路の設計に有効活用できる。また各変数のばらつきが遅延に与える影響(遅延分散)を求める式を開発した(文献

$$\sigma_{T_d}^2 \cong \left(\frac{\partial T_d}{\partial p_i}\right)^2 \sigma_{p_i}^2$$

但し、σ<sub>pi</sub> は各パラメータの標準偏差である。 さらに貫通シリコンビアを用いた三次元集 積回路における基板コンタクト無し、細粒度 基板コンタクト有り、粗粒度基板コンタト有 りの場合(図3)のクロストークノイズの式 (電気的条件は図4(b))を開発した(文献)

$$\frac{V_p}{V_{p,typ}} = \prod_{i=1}^n g_i(v_i)$$

図4 (a)遅延用構造 (b) ノイズ用構造

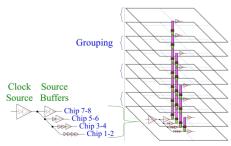

#### (3) クロック分配方式の開発

・積層チップのクロック分配ネットワークとして、複数のソースバッファを用いたクロック分配方法を考案した(文献 3 図 5 にその例を示す。この方法はクロックソースを配置するチップ以外のチップは、現在最も良く使われているバッファ付きクロック分配網を設計方法で、積層チップのクロック分配網を設計できることが利点である。

図5 マルチソースバッファ方式クロック分配

#### (4) 電源分配モデルの開発

三次元集積回路の電源ノイズ解析用の回路モデルを提示し、構造や電気的パラメータの変化に対する電源電圧降下の解析結果を提示し、最も有効な手段は電源 TSV の間隔であること明示した(文献)。

#### (5) 熱対策方法の開発

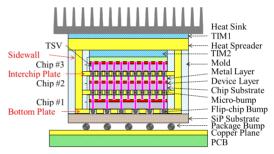

三次元集積回路の積層数やチップサイズ、消費電力、各材質の厚みや熱伝導率、ヒートシンク等様々な条件におけるチップの最高温度の違いについて解析により明らかにした。ヒートシンク間の TIM が最も温度上昇に影響を及ぼしている(熱伝導経路の妨げとなっている)ことも明確にした(文献 )

さらに温度抑制技術として積層チップの側壁を銅で覆う方法を考案した。さらにチップ間に銅プレートを挿入して熱を逃がす方法を開発した(文献 )。図 6 にその熱対策の構造を示す。

図6 熱対策の構造

# <引用文献>

M. Watanabe, M. Fukase, M. Imai, N. Niioka, T. Kobayashi, R. Karel, and A. Kurokawa, "Modeling of substrate contacts in TSV-based 3D ICs," Proc. IEEE 3DIC, pp.1-4, Dec. 2014.

M. Watanabe, N. Niioka, T. Kobayashi, R. Karel, M. Fukase, M. Imai, and A. Kurokawa, "An effective model for evaluating vertical propagation delay in TSV-based 3-D ICs," Proc. ISQED, pp.519-523, Mar. 2015.

N. Niioka, M. Watanabe, M. Fukase, M. Imai, and A. Kurokawa, "Signal propagation delay model in vertically stacked chips," IEICE Trans. Fundamentals, Vol.E98-A, No.12, pp.2614-2624, 2015.

小林徹哉,新岡七奈子,深瀬政秋,黒川敦,"インダクタンス逆行列を用いた三次元集積回路の貫通シリコンビア間結合容量抽出,"電気学会 論文誌 C, Vol.135, No.7, pp.744-751, 2015.新岡七奈子,深瀬政秋,今井雅,古見薫,三浦祐輝,黒川敦,"三次元集積回路の伝搬遅延とクロストークノイズのモデリング,"電子情報通信学会 回路とシス

テムワークショップ 講演論文集,

pp.166-171, 2015年8月.

N. Niioka, M. Imai, M. Fukase, Y. Miura, K. Furumi, and A. Kurokawa, "Clock skew reduction for stacked chips using multiple source buffers," Proc. IEEE ISCIT, pp.327-330, Oct. 2015.

古見薫,深瀬政秋,新岡七奈子,黒川敦, "積層チップの電源分配のモデリングと 電圧降下の解析,"電子情報通信学会 総合大会 講演論文集,p.100,2016年3 月.

古見薫,今井雅,新岡七奈子,黒川敦, "三次元集積回路の熱解析,"電子情報 通信学会 技術研究報告, VLD2016-38, Vol.116, No.94, pp.173-178, Jun. 2016. K. Furumi, M. Imai, and A. Kurokawa, "Cooling architectures using thermal sidewalls, interchip plates, and bottom plate for 3D ICs," Proc. ISQED, pp.283-288, Mar. 2017.

### 5. 主な発表論文等

(研究代表者、研究分担者及び連携研究者に は下線)

# [雑誌論文](計 2件)

Nanako Niioka, Masayuki Watanabe, Masaaki Fukase, Masashi Imai, and "Signal Atsushi Kurokawa, propagation delay model in vertically chips, " stacked IEICE Trans. Fundamentals of Electronics, Communications and Computer Sciences, Vol.E98-A. No.12, pp.2614-2624, 2015. DOI: 10.1587/transfun.E98.A.2614 [查 読有1.

小林徹哉,新岡七奈子,深瀬政秋,<u>黒川敦</u>,"インダクタンス逆行列を用いた三次元集積回路の貫通シリコンビア間結合容量抽出,"電気学会 論文誌 C, Vol.135, No.7, pp.744-751, 2015, DOI: 10.1541/ieejeiss.135.744 (東北支部優秀論文賞)[査読有].

# [学会発表](計20件)

Kaoru Furumi, Masashi Imai, and Atsushi Kurokawa, "Cooling architectures using thermal sidewalls, interchip plates, and bottom plate for 3D ICs," International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA (USA), 2017年3月15日.

Nanako Niioka, Masashi Imai, Masaaki Fukase, Yuuki Miura, Kaoru Furumi, and Atsushi Kurokawa, "Clock skew reduction for stacked chips using multiple source buffers," IEEE International Symposium on Communications and Information

Technologies (ISCIT), Nara Prefectural New Public Hall (Nara), 2015年10月9日.

Masayuki Watanabe, Nanako Niioka, Tetsuya Kobayashi, Rosely Karel, Masaaki Fukase, Masashi Imai, and <u>Atsushi Kurokawa</u>, "An effective model for evaluating vertical propagation delay in TSV-based 3-D ICs," International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA (USA), 2015年3月4日.

Masayuki Watanabe, Masaaki Fukase, Masashi Imai, Nanako Niioka, Tetsuya Kobayashi, Rosely Karel, and Atsushi Kurokawa, "Modeling of substrate contacts in TSV-based 3D ICs," IEEE International Conference on 3D System Integration (3DIC), Cork (Ireland), 2014年12月1日.

Nanako Niioka, Masayuki Watanabe, Rosely Karel, Tetsuya Kobayashi, Masashi Imai, Masaaki Fukase, and Atsushi Kurokawa, "Impact of on-chip interconnects on vertical signal propagation in 3D ICs," IEEE Asia Pacific Conference on Circuit and Systems (APCCAS), ANA Intercontinental Ishigaki Resort (Okinawa), 2014年11月19日.

#### 6. 研究組織

### (1)研究代表者

黒川 敦(KUROKAWA, Atsushi) 弘前大学・大学院理工学研究科・教授 研究者番号:80610592