#### 科学研究費助成專業 研究成果報告書

平成 29 年 6 月 9 日現在

機関番号: 22604

研究種目: 基盤研究(C)(一般)

研究期間: 2014~2016

課題番号: 26420242

研究課題名(和文)次世代電力変換回路に適したSAWフィルタを用いたゲート駆動回路の提案

研究課題名(英文)Proposal of multiplex transmission systems for gate drive signals of inverter circuit using surface acoustic wave filters

研究代表者

五箇 繁善(GOKA, SHIGEYOSHI)

首都大学東京・理工学研究科・准教授

研究者番号:80305416

交付決定額(研究期間全体):(直接経費) 3,900,000円

研究成果の概要(和文):次世代電力変換回路に適した,表面弾性波(SAW)を用いたゲート駆動回路を提案した.本提案法は,SAWフィルタを用いることで高温動作と信号多重化が可能となるため,次世代ワイドギャップ半導体素子の高温動作利用と,信号多重化によるマルチレベルインバータへの適用できる.得られた研究成果は次の通りである. まず,提案システム用の送・受信器の設計を行った.次に,提案法に適したSAWフィルタを設計・作製し,低い遅延時間と対すに持性との両立を図れた.さらに,作製した4chのSAWフィルタを用いてゲート信号伝送を行い,遅延時間と対していば、タの動作を発力した。以上の45円には、本規室法の方効性を実証した。

単相3レベルインバータの動作を確認した.以上の結果より,本提案法の有効性を実証した.

研究成果の概要(英文): A gate drive signal transmission system for next-generation power electric circuits using surface acoustic wave filters was proposed. Since SAW filters fabricated on lithium niobate wafers can work in the range of ~1000 degree Celsius, receivers can be located near motors and engine room, such as high temperature conditions for reducing energy loss and EMI. We designed a transmitter and receiver and fabricated 4-channel SAW filter arrays on lithium niobate wafers suitable for the proposed system. The 3-level inverter system based on the proposed system

was demonstrated without problems.

These results indicate that the proposed system design can be used to the multi-level inverter system.

研究分野: 精密周波数応用

キーワード: 電力変換回路 パワーエレクトロニクス インバータ マルチレベル 弾性表面波 SAW 次世代スイッチングデバイス

# 1.研究開始当初の背景

パワーエレクトロニクス回路は, 小電力の 電源装置から数 + MW の電力系統用機器,産 業用機器まで幅広く様々な分野へ応用され ている.最近では,スマートグリッドを実現 するための送配電系統に接続する高電圧用 途の電力変換回路の研究が活発に進められ ている.現在,一般的に利用されているパワ ーデバイスは 1.200V 以下の耐圧であれば MOSFET , 1.200V ~ 4.500V 耐圧では IGBT が 主として利用されている.これらのパワーデ バイスを用いて高電圧用電力変換回路を実 現するためには,素子損失が小さく,信頼性 の高い 2,000V 以下の耐圧の素子を多数直列 接続して構成する回路かマルチレベルイン バータと呼ばれる低耐圧素子を多数接続す る回路で実現することが有望であると考え られている.そのため,複数の回路方式が国 内外で活発に議論されている.マルチレベル インバータは,高電圧用途としての利用が期 待されている回路方式ではあるが .1.000V 以 下の電圧で利用される太陽光発電用インバ ータにもマルチレベルインバータの実用化 例は報告されており,今後はさらに幅広い用 途への展開が期待される.

一方, SiC や GaN などのワイドギャップ半 導体は,高速応答性と耐熱・放熱性から次世 代パワーデバイスの担い手として幅広く研 究・開発されている.次世代スイッチング (SW) 素子の大きな特徴の一つが幅広い使 用温度範囲であり,SW 素子単体での使用温 度は 200°C を超える動作が期待されている. これまで熱的問題から困難であったモータ - 等への直付,エンジンルーム内への設置, インホイールモータの実現などが可能とな り,電力配線の短線化によるエネルギー損失 の大幅な改善が期待できる.一般的な電力変 換回路は,制御信号を回路の電圧・電流の瞬 時値を用いてマイクロプロセッサ(マイコン, DSP, FPGA)で演算を行い,その結果を元に スイッチング信号(0-5V のパルス信号)が生 成される.しかし,現状ではSiベースの集積 化回路を用いる以外に方法は無く,動作温度 は最大でも 125°C 以下に制限される. したが って,次世代SW 素子の特徴を活かし切れる 温度範囲での動作が可能となるゲート駆動 回路が要望されていた.

## 2.研究の目的

本研究では、SW 素子を制御回路から分離し、制御信号のみを伝送することでマルチレベルインバータや次世代 SW 素子の特徴を活かす新しいゲート駆動回路を提案する.各 SW 素子に対応する受信回路として弾性表面波(SAW: Surface Acoustic Wave)フィルタを用いることで周波数多重化を図り、伝送用ケーブルを1本に簡素化する。SAW フィルタは,圧電基板上に入出力用の櫛形電極対を成膜することで、電気信号を弾性波に変換して伝

搬させることで電気的なバンドパスフィルタ特性が得られる圧電デバイスであるが,電力変換回路に必須とされる,電気的絶縁,耐熱性,安価,小型,信頼性の5つの要件を満たしている.それゆえ,次世代電力系統を担うマルチレベルインバータなどへの応用として最適である.

本研究は新規提案であるため,まず提案法の実現可能性を図るべく,基礎的な特性把握・設計手法についての検討を行う.本研究期間における最終目標は,SAW フィルタを用いたゲート駆動回路を実装し,インバータ回路を動作させることである.

#### 3.研究の方法

本研究を実施する上での具体的な課題は次の4つであり,各課題に関しての研究方法をそれぞれ示す.

#### (1) [課題 I] 送信器機構成の確立

パワーエレクトロニクスのゲート駆動回 路に求められる性能の一つに駆動波形の立 ち上がり速度が挙げられる.本システムでは, SAW フィルタを伝搬する弾性表面波が電気 信号に変換される際の立ち上がり特性がゲ ート駆動波形の立ち上がりに影響する. 櫛形 電極の電極対数は特性インピーダンスを決 定する要因となるため,一般的な50 で使用 する場合には対数はほぼ固定化される.それ ゆえ, 伝送周波数が高いほど弾性表面波の波 長が短くなり櫛形電極の伝搬方向サイズが 小さくなるため,電気信号の立上り速度が上 昇する. そこで, 立ち上がり速度を高めるた めに伝送周波数の範囲を 100~600MHz と想 定した.現状では,周波数多重処理をリアル タイムで処理するには周波数が高過ぎる. そ のため,将来的には周波数多重処理を行った データ全てをあらかじめメモリ上に配置し、 D/A 変換回路が繰り返し読み込むアドレスを 適宜変更する方法を検討するが,まずは実現 可能性を検証する段階であるため、複数の DDS (Direct Digital Synthesizer ) を用いた方法 を提案し,実験的に実証する.

# (2) [課題 ]SAW フィルタの最適設計

SAW フィルタで電気的絶縁性能を得るためには入出力電極間に距離を置けるトランスバーサル型が適している.ただし電極間の距離は弾性表面波の伝搬時間に比例するため,出来るだけ短い方が望ましい.したがって,要求される応答速度や耐絶縁性などに関して,本提案に適した設計を検討する.電力変換回路で伝送する信号は1/0の2値データで良いため,伝送周波数帯域はそれ程広の通過で良いため,伝送周波数帯域はそれ程広の通過帯域が変動しても送信機からの信号スペクトルが通過帯域内に収まっていれば問題無い.それゆえ,通過帯域を広げる方向での検討を行う.

# (3) [課題 ]受信・検波回路の構成

受信器では最小限の部品点数で SW 素子の駆動を行いたい . SW 素子のゲート~ソース端子間にはしきい値以上の電圧を印加する必要がある . したがって検波回路では電圧を大きくする構成が必要となる . また , エネルギー損失が最小となるような回路構成も検討する .

# (4) [課題 ]インバータ回路の試作

本提案法の有用性を示すため,課題 ~ で得られた成果を基に100 V,10A の電力変換回路(インバータ)を実際に試作し動作させる.その結果を基に,本方式を用いた場合のスイッチング周波数の制約等について検討を行う.

以上の課題 I~IV の利点を組み合わせて, 本提案法の有効性を明らかにする.

# 4.研究成果

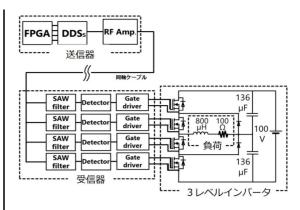

(1)課題 I に関して,実験に用いた提案システ ムの構成図を図1に示す.送信器では,FPGA により必要なチャネル(SW 素子数に相当) 数分のゲート駆動信号を生成し,このデジタ ル信号の ON/OFF に従って各チャネルに割り 振られた SAW フィルタの中心周波数を各 DDS より出力させる .DDS からの RF 信号は コンバイナーで加算され,アンプにより電力 増幅した後 RF 信号として同軸ケーブルで送 信される . 受信器では送信器からの RF 信号 をチャネル数に応じてデバイダーで分配す る .分配された RF 信号は SAW フィルタによ り各チャネル用の RF 信号のみを後段に伝達 し,検波回路により整流され,RF 成分が直 流成分に変換される. したがって, RF 信号 の ON/OFF により直流成分が ON/OFF するた めゲート駆動用のデジタル信号が復調され る.同図の実験例では,3 レベルインバータ を正常動作させることが確認出来た.実験結 果については 4-(4)章に記述する.

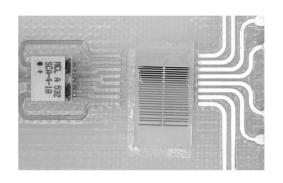

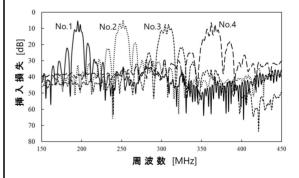

(2)課題 の SAW フィルタの最適設計につい て検討した.使用する圧電基板には,電気機 械結合係数の大きさ,およびキュリー点(相 転移温度)が 1,200 と十分に高いことから 128°Y-X LiNbO3を用いた.全ての SAW フィ ルタで同じ電気的絶縁性能を確保するため に,入出力の櫛形電極間距離(伝搬路長)を 0.2 mm に統一した .櫛形電極の交差幅は 50λ , 対数は22対,電極膜厚は1,200,電極素材 はアルミニウムを使用した.図2に専用設計 の 12 チャネル SAW フィルタアレイを示す. PCB 基板上の電極配線へはワイヤボンディ ングで接続した.12 チャネルの中から,近接 する 4 つの SAW フィルタの特性を計測した 結果を図 3 に示す.同図より, 各 SAW フィ ルタの中心周波数における挿入損失はすべ て 8dB 以下であり,お互いの通過周波数にお ける抑圧比は 27dB 以上確保できている事が

図1 インバータシステムの構成

図 2 作製した SAW フィルタアレイ (SAW は写真中央部)

図 3 インバータに用いた SAW フィルタ の周波数通過特性

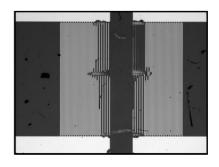

図 4 絶縁破壊試験後(DC1,120V 印加)

分かる . また , クロストークの影響は確認できないレベルであった .

次に,電気的絶縁性能を調べるために絶縁破壊試験を行った.試験条件として,入出力の櫛形電極はインピーダンス50Ωであり,数VのRF信号が印加される状況を考慮すると,数百Vの一次電圧に比べほぼ無視できる.したがって,入出力それぞれの櫛形電極を短絡し,入出力間に直流電圧を印加しながら試験を行った.

図4に絶縁破壊試験後の SAW フィルタの写真を示す.この資料では直流電圧 1,120V 印加時に絶縁破壊を起こし伝搬路近傍の櫛形電極が損傷した.この時の電界強度は5.6kV/mm であり,一般的な空気の絶縁破壊電界強度 3kV/mm の 2 倍程度の値であった.今回は,目標電圧 600V を基に設計していたため,まだまだ十分な余裕がある事が分かった.したがって,SAW デバイスの動作環境を整える事で伝搬路長の低減が可能であることから、SAW フィルタのさらなる伝搬遅延時間短縮が可能である事を明らかにできた.

(3)課題 の受信・検波回路の構成について検討した。SAW フィルタの出力で得られる波形の電圧振幅はあまり大きくないため,通常の整流回路や検波回路では十分な出力電圧を確保できない.そこで,電圧増倍回路としてコッククロフト・ウォルトン回路(CW 回路にした整流回路を検討した.CW 回路には電圧を増大する基本構成があり,この構えとして、2 段の倍電圧整流回路を基本とし,RF信号の+側とー側それぞれにCW 回路を組む差動型を提案し,4 倍近い電圧を確保する事が可能となった.

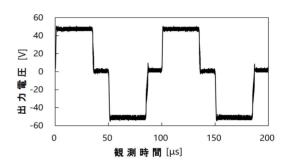

(4)課題 のインバータ回路の試作を行った.当初予定よりも研究が順調に進んだため,4チャンネルの駆動波形伝送が必要な単相3レベルインバータの試作を行うことが出来た.回路構成は図1の通りである.図5は試作したインバータの出力電圧波形を示している.同図より,+50,0,-50 Vの3レベル状態が出力できていることが確認できる.

表 2 に試作したシステムの伝搬遅延時間を示す.一般的なインバータ回路はスイッチング音が聞こえないように可聴帯域外 (20kHz) で使用することが求められるため,20kHz の周期の 5%である  $2.5\mu s$  以内を目標値とした.同表より,各チャネル間の伝搬遅延時間差があるが,これは SAW フィルタの中心周波数が異なること,および作製バラつきによるが、最近により十分解決できる問題であると考えている.立下り・上りの合計時間は概ね  $1\mu s$  以下であり,目標値を十分に下回っていることを確認できた.

#### (5)まとめ

本研究では,提案システムの有効性を実証するために,送受信構成の構築,SAW フィルタの最適設計,検波回路の性能向上,インバータの試作を行った.実験結果からは,本システムが問題なくインバータシステムを動作可能であること,遅延時間が目標値を十分に下回ったこと,十分な電気的絶縁性能を有することが明らかになった.

以上の結果より,提案システムがマルチレベルインバータ駆動回路に求められる要求を満たせることを実証した.今後は実用化に向けた性能向上に関する研究を行う予定である.

図 5 試作した 3 レベルインバータの 出力波形

表 2 試作したインバータシステムの 遅延時間

| チャネル | 立上<br>リ<br>[μs] | 立下<br>リ<br>[µs] | 立上り<br>下り合計<br>[µs] | 目標<br>[µs] |

|------|-----------------|-----------------|---------------------|------------|

| 1    | 0.53            | 0.52            | 1.05                |            |

| 2    | 0.33            | 0.47            | 0.80                | 2.5        |

| 3    | 0.46            | 0.40            | 0.86                | 2.3        |

| 4    | 0.50            | 0.44            | 0.94                |            |

# 5 . 主な発表論文等

(研究代表者,研究分担者及び連携研究者に は下線)

#### 〔雑誌論文〕(計3件)

Keita Kubo, Nanae Kanai, Fumiya Kobayashi, <u>Shigeyoshi Goka</u>, <u>Keiji Wada</u>, and <u>Shoji Kakio</u>, 「Design of surface acoustic wave filters for the multiplex transmission system of multilevel inverter circuits」, Japanese Journal of Applied Physics,查読有,**56**, 2017, 07JD03

五箇繁善, 和田圭二, 垣尾省司,「SAW

フィルタを用いたインバータにおけるゲート駆動信号多重化の動作検証 = 次世代インバータ回路に適したゲート駆動回路の提案 = 」、超音波テクノ(掲載決定)、査読無(解説論文)

Akifumi Suzuki, Kensuke Ueda, <u>Shigeyoshi</u> <u>Goka</u>, <u>Keiji Wada</u>, and <u>Shoji Kakio</u>,

<sup>r</sup> Multiplex transmission system for gate drive signals of inverter circuit using surface acoustic wave filters J, Japanese Journal of Applied Physics,查読有,55, 2016, 7S1

#### [学会発表](計8件)

金井七重,久保慶太,<u>和田圭二,五箇繁</u> <u>善</u>,ゲート信号と駆動電力を同時に伝送 可能な SAW フィルタを用いたゲート駆 動回路の実験検証」 電気学会,全国大 会,2017年3月16日,富山大学(富山 県・富山市)

小林史弥,久保慶太,<u>五箇繁善</u>,<u>和田圭</u> 二,<u>垣尾省司</u>,「SAW フィルタを用いた 3レベルインバータシステムの検証」電 気学会 EM & 精密周波数合同委員会, 2016年12月2日,登別市民会館(北海 道・登別市)

Kubo, Kanai, Kobayashi, <u>Goka</u>, <u>Wada</u>, <u>Kakio</u>, <sup>r</sup> Three-level inverter system based on multiplex transmission using SAW filters J USE2016, 2016年11月18日,釜山(韓国)

久保慶太,小林史弥,五箇繁善,和田圭二,垣尾省司,「SAW フィルタを用いた多重通信システムのフルブリッジインバータへの適用」第45回 EMシンポジウム,2016年6月17日 東京理科大学森戸記念館(東京都・新宿区)

鈴木陽文,上田健介,五箇繁善,和田圭二,垣尾省司「SAW フィルタを用いたインバータにおけるゲート信号多重化の動作検証」 USE2015,2015年11月6日,つくば国際会議場(茨城県・つくば市)

鈴木陽文,上田健介,<u>五箇繁善,和田圭</u> 二,「SAW フィルタを用いた次世代イン バータ用多重通信における動作検証」 第 44 回 EM シンポジウム,2015 年 6 月 18 日,東京理科大学森戸記念館(東京都・ 新宿区)

上田健介, 鈴木陽文, 和田圭二, 五箇繁 <u>善</u>, 垣尾省司「インバータのゲート駆動 回路用 SAW フィルタの設計とその実験 検証」半導体電力変換研究会 ,SPC-15-173, 2015年10月30日, 長崎歴史文化博物館 (長崎県・長崎市) 五箇繁善,和田圭二,粂尚成,「SAW フィルタを用いた次世代インバータ用周波数多重通信における 送受信機の基礎検討」第43回 EMシンポジウム,2014年6月6日,東京理科大学森戸記念館(東京都・新宿区)

〔その他〕

ホームページ等

http://researchmap.jp/read0192151/

#### 6. 研究組織

# (1)研究代表者

五箇 繁善(GOKA SHIGEYOSHI) 首都大学東京・理工学研究科・准教授 研究者番号:80305416

#### (2)研究分担者

和田 圭二 (WADA KEIJI) 首都大学東京・理工学研究科・准教授 研究者番号: 00326018

# (3)連携研究者

垣尾 省司 (KAKIO SHOJI) 山梨大学大学院・総合研究部・教授 研究者番号: 70242617